Reducing Parasitic Effects in High-Frequency PCB Layouts

JUN 27, 2025 |

Understanding Parasitic Effects

Parasitic effects are unintended electrical characteristics that arise from the physical layout and materials of a PCB. At high frequencies, even the smallest inductance from a trace or the tiniest capacitance between two adjacent pathways can influence circuit behavior. These parasitic elements can lead to impedance mismatches, signal reflections, and undesired coupling, ultimately degrading signal integrity and performance.

Strategies for Minimizing Parasitic Inductance

One primary parasitic effect to consider is inductance. Parasitic inductance can be minimized through careful design choices:

1. **Trace Geometry**: Shorten trace lengths where possible, as longer traces can increase inductance. Utilize wider traces to reduce inductance by lowering trace resistance and increasing the skin effect area.

2. **Ground Planes**: Implement solid ground planes to provide a low-inductance return path for signals, minimizing loop areas and hence inductance. Ensure the ground plane is directly beneath signal traces to enhance performance.

3. **Via Optimization**: Reduce the use of vias, which contribute to inductance. When necessary, use multiple vias in parallel to distribute current evenly and reduce the associated inductive effects.

Reducing Parasitic Capacitance

Parasitic capacitance occurs between conductors separated by a dielectric material. It can couple signals unintentionally and affect signal timing and integrity. To reduce parasitic capacitance:

1. **Layer Spacing**: Increase the spacing between signal layers and adjacent ground or power planes to decrease inter-layer capacitance.

2. **Controlled Impedance**: Design with controlled impedance to prevent mismatches that can amplify parasitic capacitance effects. This involves maintaining consistent trace width, spacing, and dielectric material properties.

3. **Isolation Techniques**: Use ground shielding or guard traces to isolate sensitive signals from noisy environments, effectively reducing capacitive coupling.

Mitigating Parasitic Resistance

Though often overlooked, parasitic resistance can dissipate power and introduce noise. Mitigation strategies include:

1. **Material Selection**: Use low-resistance materials for traces, such as copper, and ensure traces are adequately thick to handle expected current loads without excessive resistance.

2. **Plated Through-Holes and Vias**: Properly size plated through-holes and use multiple vias to minimize resistance in power delivery networks.

3. **Thermal Management**: Implement efficient thermal management strategies to prevent resistance increase due to temperature rise, which can affect material resistivity.

Signal Integrity and Crosstalk Reduction

Signal integrity is crucial in high-frequency designs. Crosstalk, or unwanted coupling between adjacent traces, can distort signals and introduce noise. To combat this:

1. **Trace Routing**: Keep high-speed and sensitive signal traces apart from noisy signals. Route differential pairs close together to minimize loop areas and improve immunity to external noise.

2. **Layer Stackup**: Carefully plan your layer stackup to isolate and shield critical signals from potential sources of interference. Employ ground or power planes between signal layers for added isolation.

3. **Decoupling Capacitors**: Strategically place decoupling capacitors near IC power pins to suppress power supply noise and stabilize voltage levels.

Conclusion

Reducing parasitic effects in high-frequency PCB layouts requires a comprehensive understanding of how these effects arise and impact circuit performance. By implementing thoughtful design strategies, such as optimizing trace geometry, ensuring proper grounding, and using appropriate materials, designers can minimize the impact of parasitic inductance, capacitance, and resistance. These efforts will enhance signal integrity, reduce noise, and improve the overall performance of high-frequency electronic devices. As technology continues to advance, staying vigilant about parasitic effects will remain an essential aspect of effective PCB design.

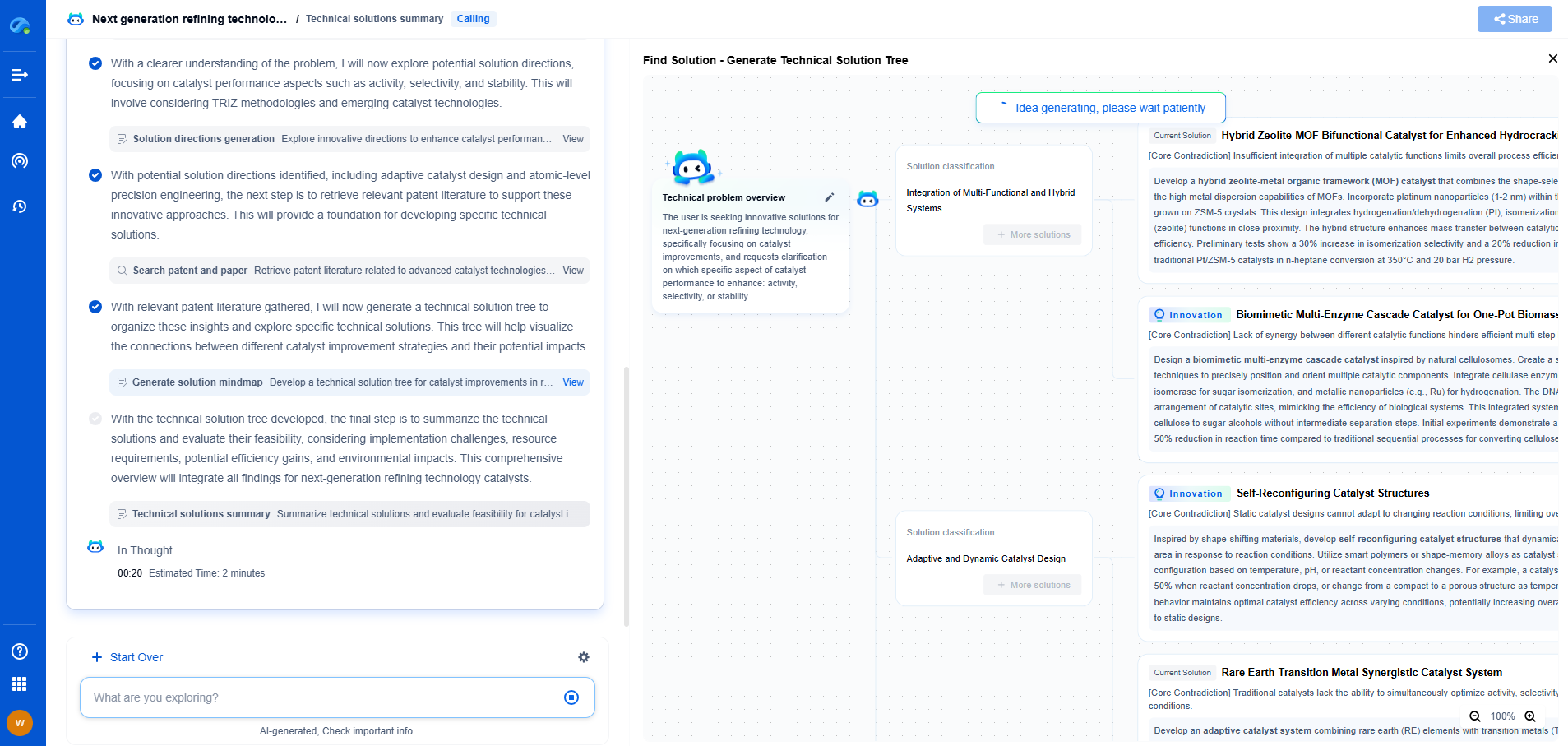

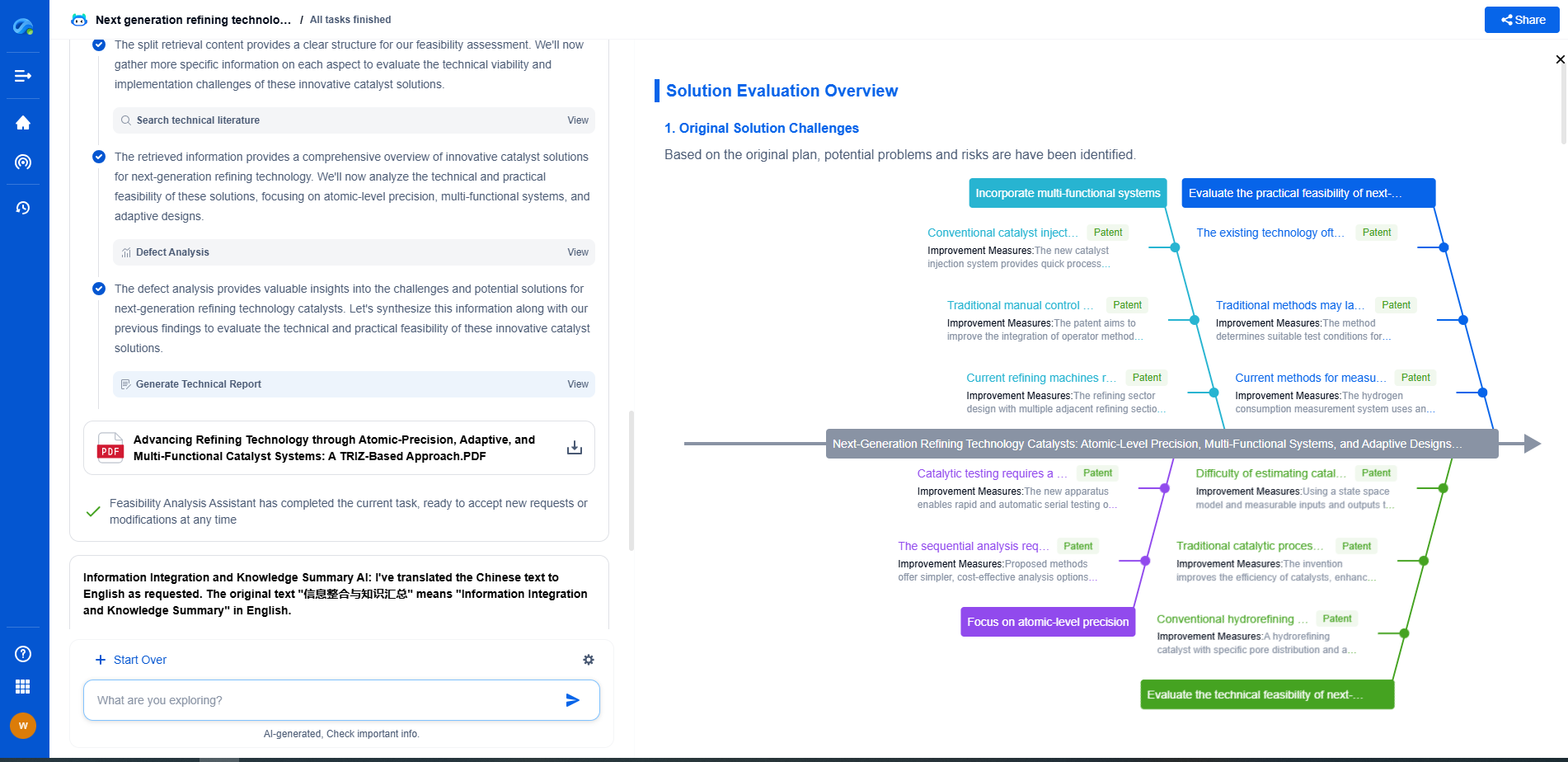

Unlock Next-Gen Innovation in Communication Technology with Patsnap Eureka

The field of communication technology is evolving at breakneck speed—from 5G and satellite systems to next-gen wireless protocols and quantum communications. Staying ahead demands more than just information—it requires strategic insights, real-time patent intelligence, and a deep understanding of technological trajectories.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface. Whether you're optimizing signal processing designs, navigating 3GPP standards, or exploring IP strategies for IoT and 6G networks, Eureka helps you move faster, think deeper, and innovate smarter.

Try Patsnap Eureka today—and see how it can transform the way you work across the entire communication technology innovation lifecycle.