SADP Mandrel Formation: Litho-Etch-Litho-Etch Sequence

JUL 28, 2025 |

The semiconductor industry constantly evolves, driven by the relentless pursuit of higher performance and greater energy efficiency. One of the critical challenges faced is the need to create increasingly smaller and more intricate patterns on silicon wafers. Spacer-Assisted Double Patterning (SADP) is a sophisticated technique that has emerged as a solution, enabling the fabrication of extremely fine features. This blog focuses on the litho-etch-litho-etch sequence in SADP mandrel formation, a crucial step in advancing semiconductor manufacturing.

Understanding the Basics of SADP

To grasp the intricacies of SADP mandrel formation, it's essential to understand the basic principles of the SADP process. SADP leverages the concept of pitch splitting to double the pattern density of a given lithographic technology. This is accomplished by using a spacer material to define additional features, effectively allowing chip manufacturers to achieve smaller feature sizes than the resolution limits of their lithography tools.

The Role of Mandrels in SADP

Mandrels are the initial patterns created on the wafer, serving as the template for subsequent spacer deposition. Think of them as the skeleton of the final structure, around which additional features will be built. The accuracy and precision of mandrel formation are critical, as any deviation can lead to cascading errors in the final circuit patterns.

The Litho-Etch-Litho-Etch Sequence

The litho-etch-litho-etch sequence is a series of steps employed in the SADP process to define the mandrels with high precision. This sequence is crucial for achieving the intended structural dimensions and ensuring the integrity of subsequent manufacturing steps.

1. **First Lithography Step**: The process begins with the deposition of a photoresist layer on the wafer. Using a photomask, the resist is exposed to light, defining the initial pattern of the mandrels. This step is crucial for determining the ultimate fidelity of the patterning process.

2. **First Etching Step**: Following exposure, the resist-covered wafer undergoes an etching process. This removes the exposed regions, transferring the pattern into the underlying material, usually a silicon dioxide or silicon nitride layer. The precision of this etch determines the accuracy of the mandrel dimensions.

3. **Second Lithography Step**: After the first etching, another photoresist layer is applied. This step involves a second round of exposure and development, further refining the pattern complexity. This stage is essential for achieving the desired feature density.

4. **Second Etching Step**: The final etching step removes the exposed regions of the second resist layer, completing the mandrel formation. This etch is critical in defining the exact shape and size of the mandrels, which will serve as the foundation for spacer deposition.

Challenges and Considerations

While the litho-etch-litho-etch sequence offers a pathway to creating extremely fine patterns, it is not without challenges. The alignment between the two lithographic steps must be perfect to ensure that the final pattern meets the necessary specifications. Additionally, the etching processes must be finely tuned to maintain dimensional accuracy without compromising the structural integrity of the mandrels.

Applications and Future Prospects

SADP mandrel formation using the litho-etch-litho-etch sequence has become indispensable in manufacturing advanced semiconductor devices. It is particularly useful in the production of DRAM, NAND flash, and other memory devices that require high-density patterning. As the industry pushes towards even smaller nodes, innovations in SADP techniques and etch chemistries will be critical to overcoming the challenges of next-generation semiconductor fabrication.

Conclusion

The litho-etch-litho-etch sequence in SADP mandrel formation represents a cornerstone of modern semiconductor manufacturing. By enabling the creation of incredibly fine patterns, it allows for the continued miniaturization of electronic components, driving advancements in technology and performance. As we look to the future, ongoing research and development in this area will be vital to meeting the ever-growing demands of the semiconductor industry.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

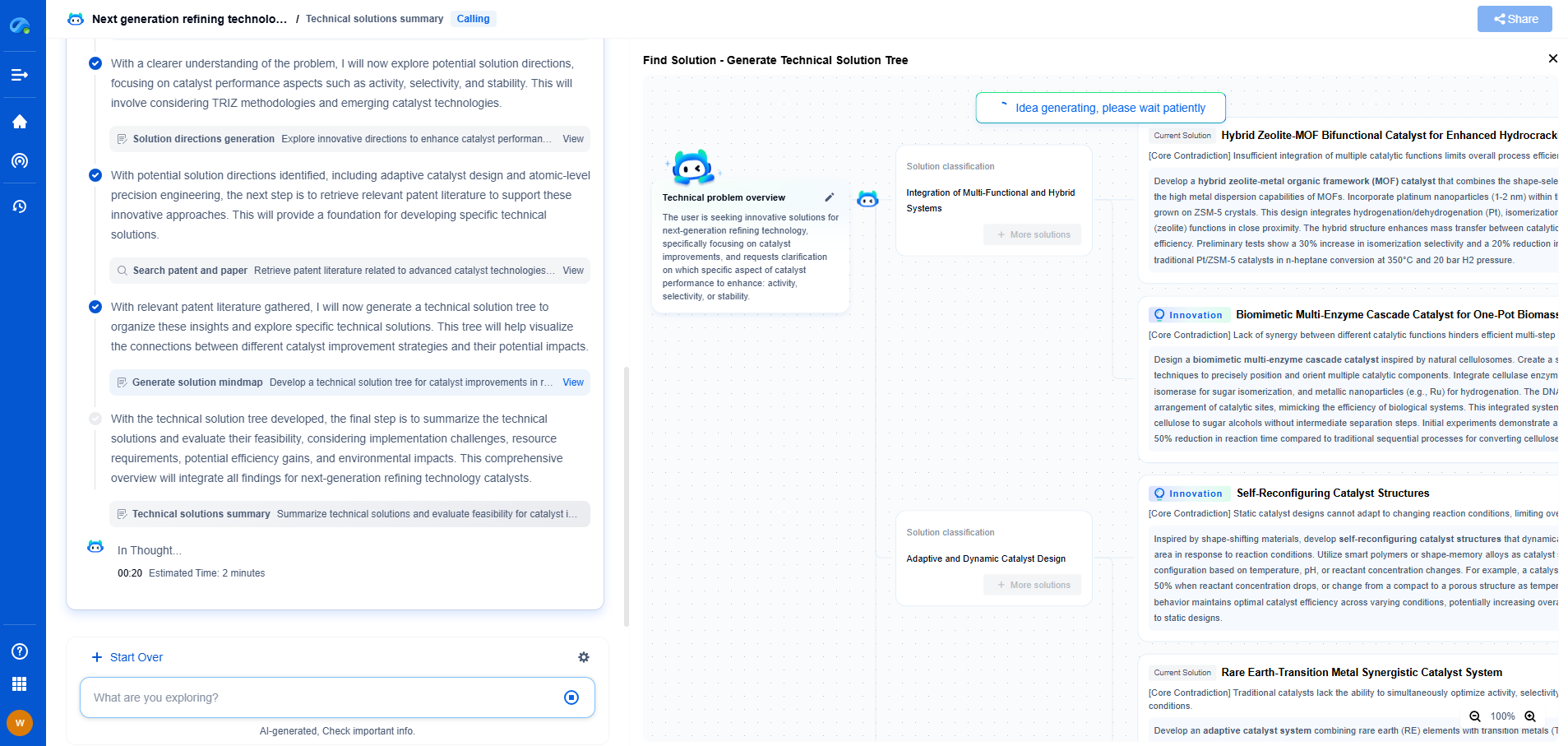

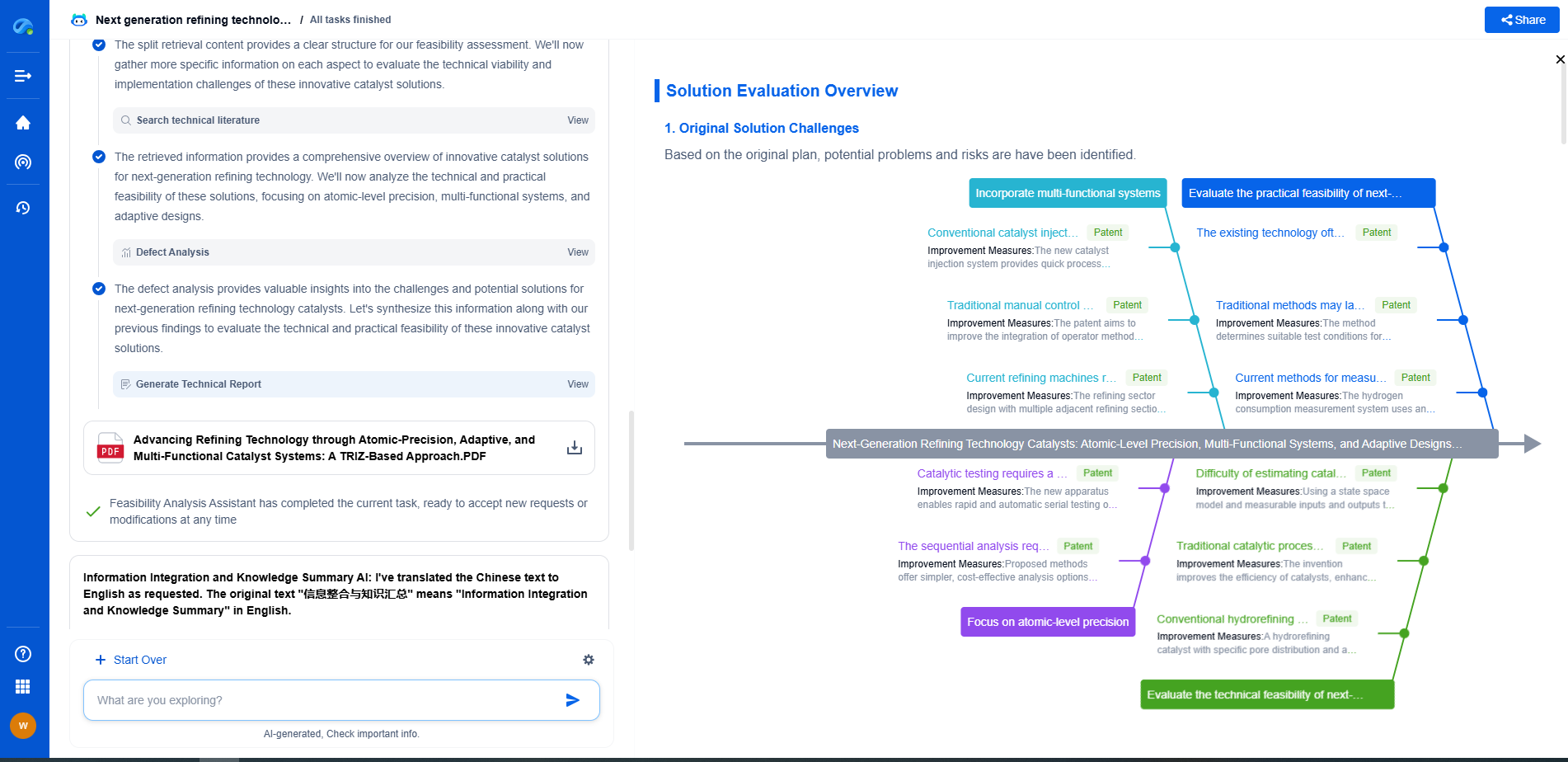

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.