Sample-and-Hold Errors: How to Minimize Droop and Aperture Jitter

JUL 17, 2025 |

Sample-and-hold (S/H) circuits are fundamental components in analog-to-digital conversion systems, playing a critical role in capturing and maintaining an analog signal's amplitude for processing. However, like any electronic component, S/H circuits can introduce errors that affect the accuracy and performance of the system. Two common issues are droop and aperture jitter. Understanding these errors and knowing how to minimize them is essential for optimizing the performance of your circuits.

Defining Droop in Sample-and-Hold Circuits

Droop refers to the gradual decline in the held voltage level over time in a sample-and-hold circuit. It is primarily caused by leakage currents in the holding capacitor and the switches used in the circuit. Droop can lead to a loss of signal integrity and accuracy, which is especially problematic in applications requiring long hold times or high levels of precision.

Strategies to Minimize Droop

1. **Use High-Quality Capacitors**: Choosing capacitors with low leakage characteristics can significantly reduce droop. Teflon or polypropylene capacitors are good choices due to their excellent insulation properties.

2. **Optimize Switch Design**: Employing switches with low on-resistance and minimal charge injection can help minimize the errors introduced during the sample and hold phases. MOSFETs and CMOS switches are often preferred for their low leakage attributes.

3. **Temperature Management**: Ensure that the circuit operates within an optimal temperature range, as higher temperatures can increase leakage currents. Proper heat dissipation techniques and temperature compensation can help maintain consistent performance.

4. **Correct Circuit Layout**: A well-designed layout that minimizes parasitic capacitances and leakages can contribute significantly to reducing droop. Employing guard rings and proper grounding techniques can be beneficial.

Understanding Aperture Jitter

Aperture jitter, another significant error in S/H circuits, refers to the uncertainty in the exact moment the sampling occurs. This time uncertainty can lead to errors in the amplitude of the sampled signal, especially in high-frequency applications. Aperture jitter is often introduced by noise in the clock signal and the inherent characteristics of the sampling switch.

Methods to Reduce Aperture Jitter

1. **Use Low-Jitter Clocks**: Utilizing a high-quality clock source with low phase noise can significantly reduce aperture jitter. Crystal oscillators with proper buffering and filtering can help achieve this.

2. **Enhance Switching Speed**: Faster switches can minimize the duration of the sampling phase, thereby reducing the window for jitter to occur. Technologies such as GaAs or SiGe can provide faster switching times compared to traditional silicon.

3. **Minimize Signal Path Length**: Reducing the physical path length of the signal can decrease the potential for jitter-inducing delays. This involves careful PCB design to ensure that the critical paths are as short and direct as possible.

4. **Proper Power Supply Decoupling**: Ensuring a stable power supply with adequate decoupling can reduce the effects of jitter. Using bypass capacitors and low-dropout regulators can help maintain a stable voltage level.

Conclusion: Optimizing Sample-and-Hold Performance

Minimizing droop and aperture jitter is crucial for maintaining the integrity and accuracy of sample-and-hold circuits. By carefully selecting components, optimizing circuit design, and employing effective layout strategies, these errors can be significantly reduced. Ultimately, understanding the sources of these errors and taking proactive steps to mitigate them will lead to more reliable and precise analog-to-digital conversion systems, enhancing the performance of your electronic projects.

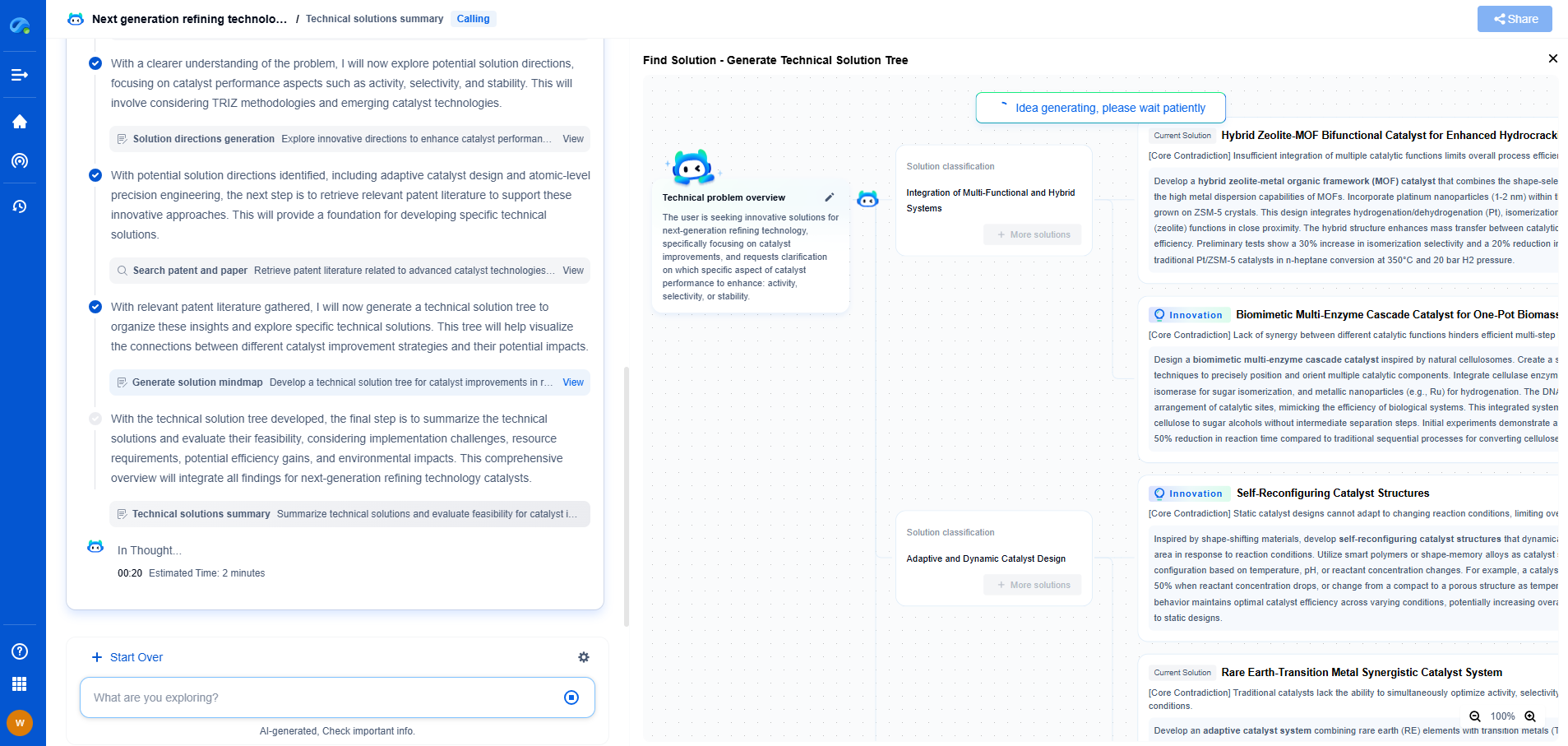

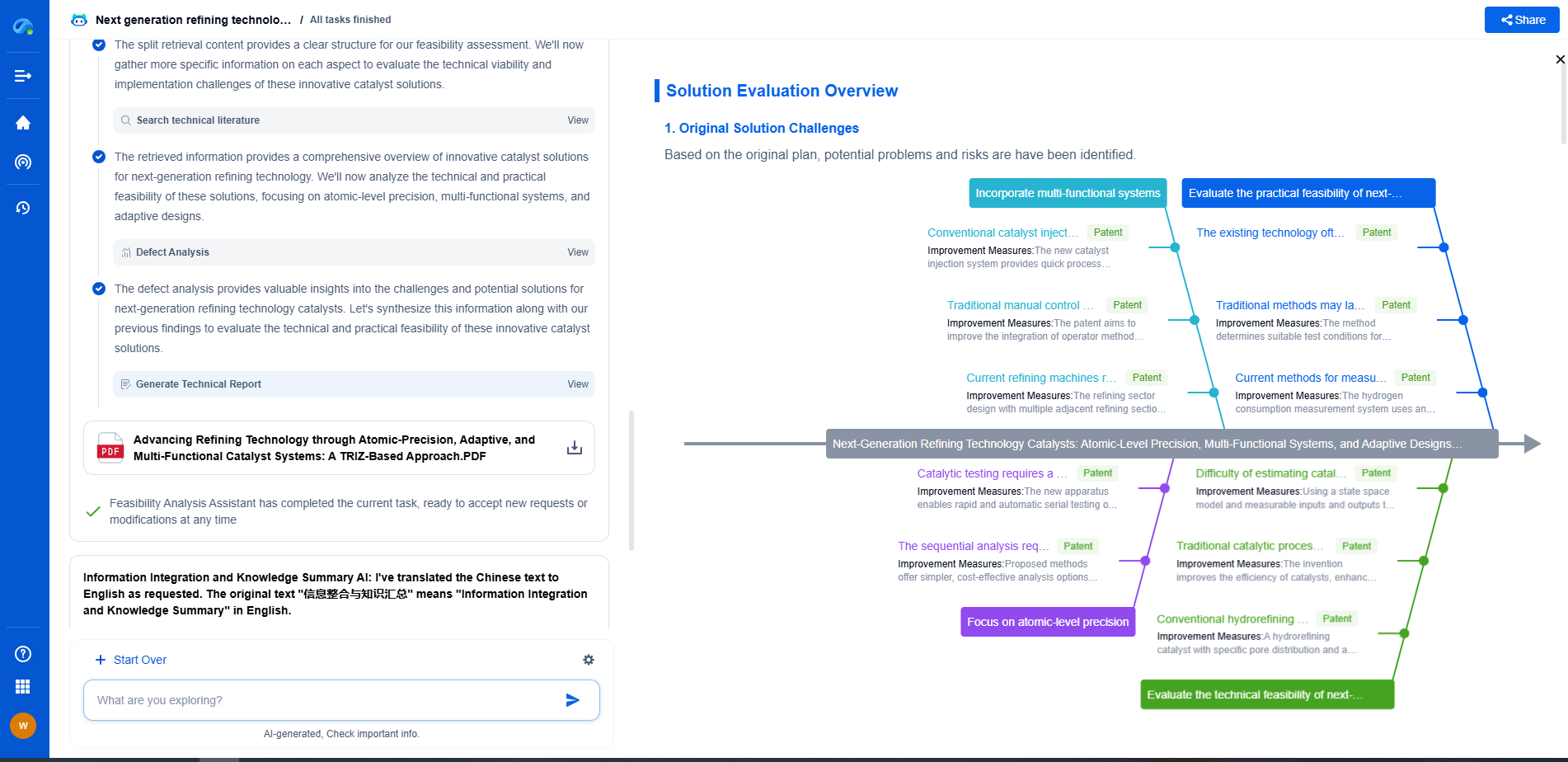

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com