Signal Integrity Design: Optimizing Capacitor Placement for Decoupling

JUL 9, 2025 |

Signal integrity is a critical aspect of electronic design, ensuring that signals maintain their integrity and functionality as they travel through a system. One of the key elements in maintaining signal integrity is the proper use of decoupling capacitors. Decoupling capacitors help to stabilize voltage levels by providing a local energy reservoir, thereby reducing noise and improving overall performance. Effective capacitor placement is crucial for optimizing decoupling and enhancing signal integrity in electronic systems.

Understanding the Role of Decoupling Capacitors

Decoupling capacitors serve two primary functions: they filter out high-frequency noise and provide immediate current to the integrated circuits (ICs) as needed. This is particularly important in high-speed digital circuits where rapid changes in current can cause voltage fluctuations, known as ground bounce or Vcc sag. By strategically placing decoupling capacitors, designers can mitigate these issues, ensuring a stable power supply for the ICs.

Factors Influencing Capacitor Placement

Several factors must be considered when determining the optimal placement of decoupling capacitors. These include the layout of the power and ground planes, the frequency characteristics of the signals, and the physical constraints of the board. The capacitors should be placed as close as possible to the power pins of the ICs to minimize the loop inductance, which can adversely affect performance.

Placement Strategies for Optimal Decoupling

1. **Proximity to Power Pins**: The most effective way to minimize inductance is to place decoupling capacitors directly adjacent to the power pins of the ICs. This minimizes the distance that the decoupling current must travel, thereby reducing the potential for noise and voltage fluctuations.

2. **Use Multiple Capacitors**: Employing a combination of capacitors with different values can effectively cover a broad frequency range. For instance, larger capacitors can handle lower frequencies, while smaller capacitors are better suited for higher frequencies. This ensures comprehensive decoupling across the board.

3. **Minimize Loop Area**: The area enclosed by the current path from the power pin through the capacitor and back to the ground should be minimized. A smaller loop area reduces inductance and enhances the effectiveness of the decoupling capacitor.

4. **Optimize Via Placement**: Proper via placement is essential to maintain a low inductance path. Vias should be placed close to the power and ground pads of the capacitor to provide a direct and efficient current path.

5. **Consider the Stack-Up**: The arrangement of power and ground layers in the PCB stack-up can impact the effectiveness of decoupling capacitors. Adjacent power and ground planes provide inherent capacitive coupling, which can aid in decoupling efforts.

Simulation and Testing

Once the capacitors are placed, it is crucial to validate their effectiveness through simulation and testing. Advanced simulation tools can model the electrical behavior of the board and predict potential signal integrity issues. Testing the physical prototype can confirm the simulation results and ensure that the design meets performance requirements.

Conclusion

Optimizing capacitor placement for decoupling is a vital component of signal integrity design. By considering factors such as proximity to power pins, loop area, and the use of multiple capacitors, designers can significantly enhance the performance and reliability of electronic systems. Through careful planning and validation, signal integrity can be maintained, ensuring the success of high-speed digital applications.

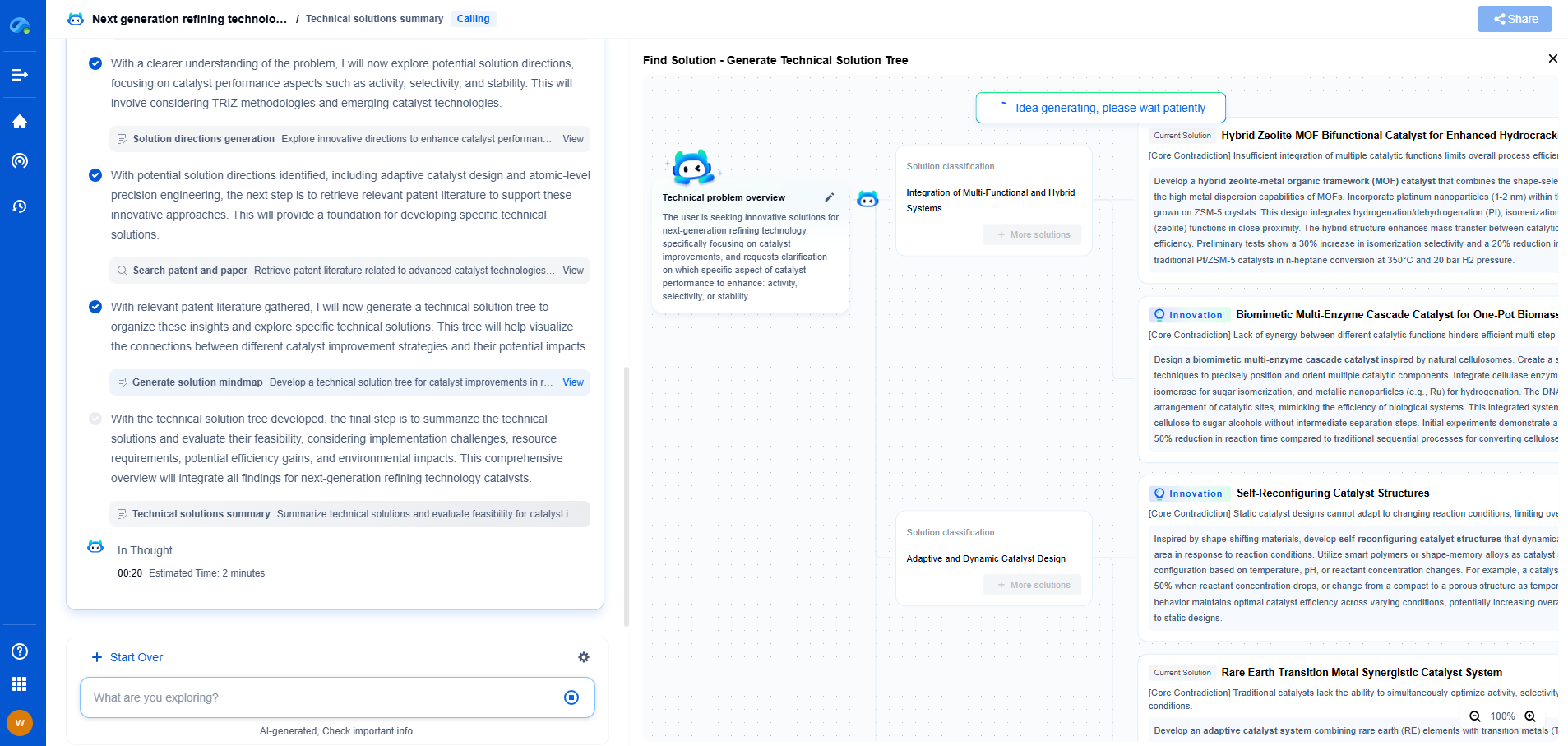

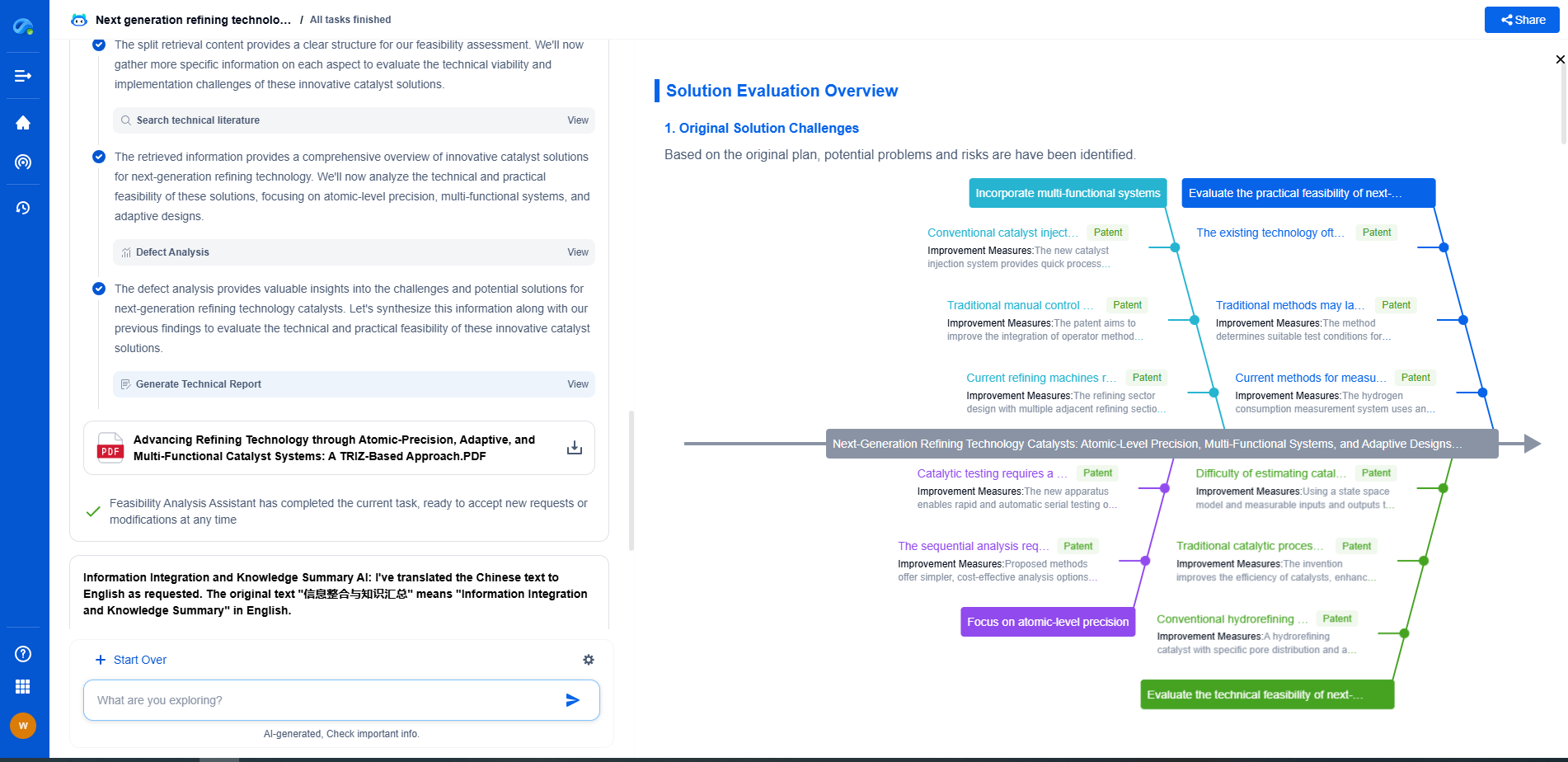

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com