SMT Pad Design Rules for Large Chip Capacitor Placement

JUL 9, 2025 |

Understanding the Importance of SMT Pad Design

In SMT, the pad design serves as the foundation for the component placement, influencing both the electrical and mechanical stability of the assembly. Large chip capacitors, in particular, require careful consideration due to their size and potential for mechanical stress. A well-designed pad ensures proper alignment, solder joint formation, and thermal management, ultimately enhancing product performance and lifespan.

Key Design Considerations for Pad Geometry

The geometry of the SMT pad plays a crucial role in accommodating large chip capacitors. The pads must be appropriately sized to match the capacitor's terminations. Typically, the pad length should be slightly longer than the capacitor end to allow for thermal expansion and contraction, while the width needs to support the solder joint without excessive spreading. Additionally, the space between the pads (pad-to-pad clearance) should be optimized to prevent solder bridging, which can cause short circuits.

Solder Mask and Paste Application

Solder mask design is another critical factor in pad design. It serves to define the PCB area where solder is applied and to avoid solder flow in unintended areas. For large chip capacitors, ensuring that the solder mask opening is well-aligned and slightly larger than the pad helps in controlling the solder paste volume and preventing solder balling. The solder paste stencil design should distribute an adequate amount of solder to form reliable joints, typically covering 50-75% of the pad area.

Thermal and Mechanical Considerations

Large chip capacitors can generate and be affected by heat, so thermal management is vital. Incorporating thermal vias in the pad design can help dissipate heat effectively, reducing the risk of thermal damage to the component and surrounding circuitry. Moreover, mechanical stability is paramount, as large components are prone to stress due to vibration and thermal cycling. Using a combination of anchors and robust solder joints can mitigate these stresses.

Minimizing Parasitic Effects

The layout of SMT pads also influences the electrical characteristics of the circuit. Large chip capacitors can introduce parasitic inductance and resistance if not properly managed. To minimize these effects, keep the pad traces as short and direct as possible, and use a ground plane to reduce impedance. This approach not only ensures optimal capacitor performance but also reduces electromagnetic interference (EMI) issues.

Testing and Validation

Once the pad design is finalized, it's important to validate its effectiveness through testing. Prototype boards should be manufactured and subjected to various stress tests, such as thermal cycling and mechanical vibration, to assess the reliability of the pad design. Any issues identified during testing should be fed back into the design process for refinement. This iterative approach ensures that the final design meets the required performance standards.

Conclusion

The design of SMT pads for large chip capacitors is a critical aspect of electronics manufacturing that requires a careful balance between mechanical, thermal, and electrical considerations. By adhering to sound design principles and thoroughly testing prototypes, manufacturers can achieve reliable and high-performance electronic assemblies.

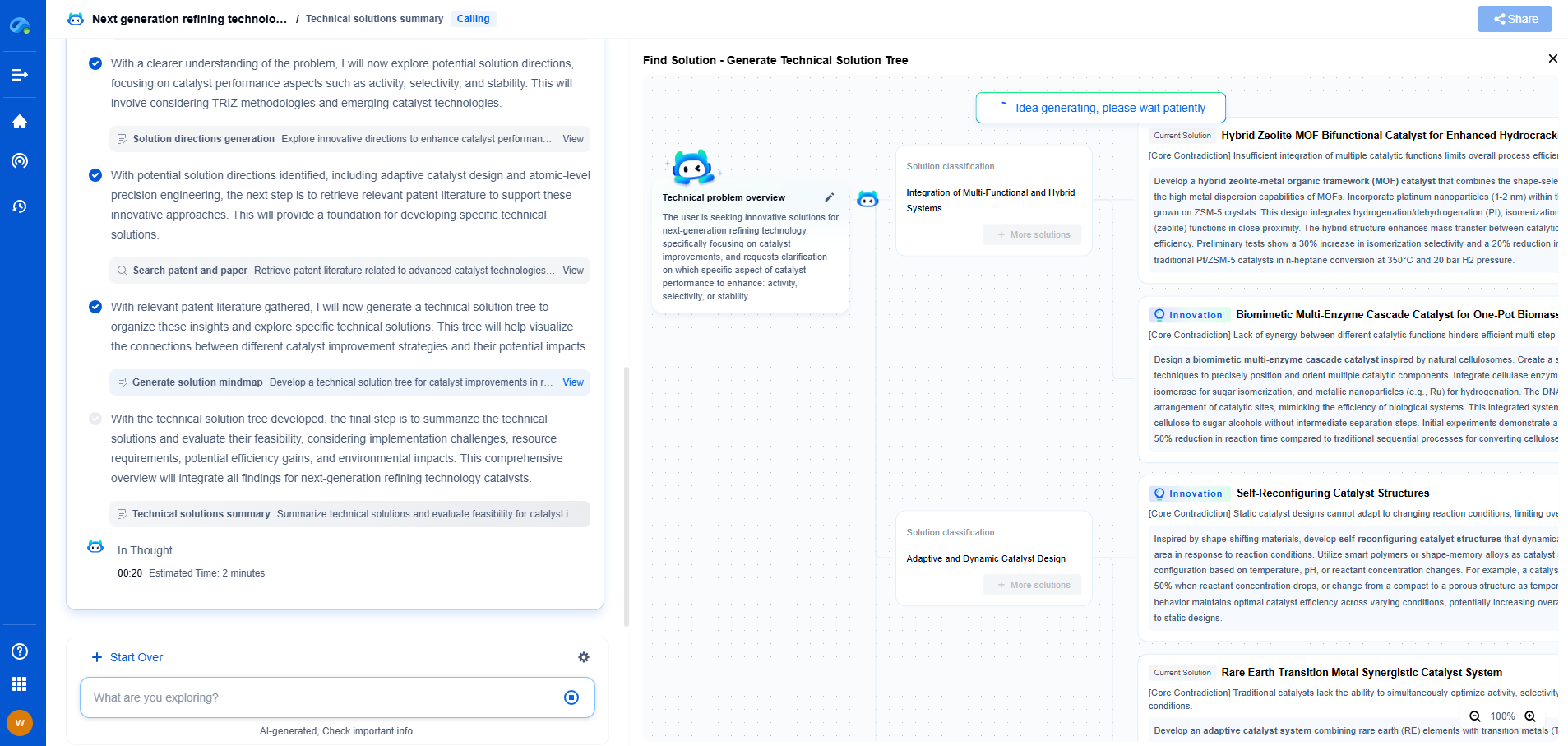

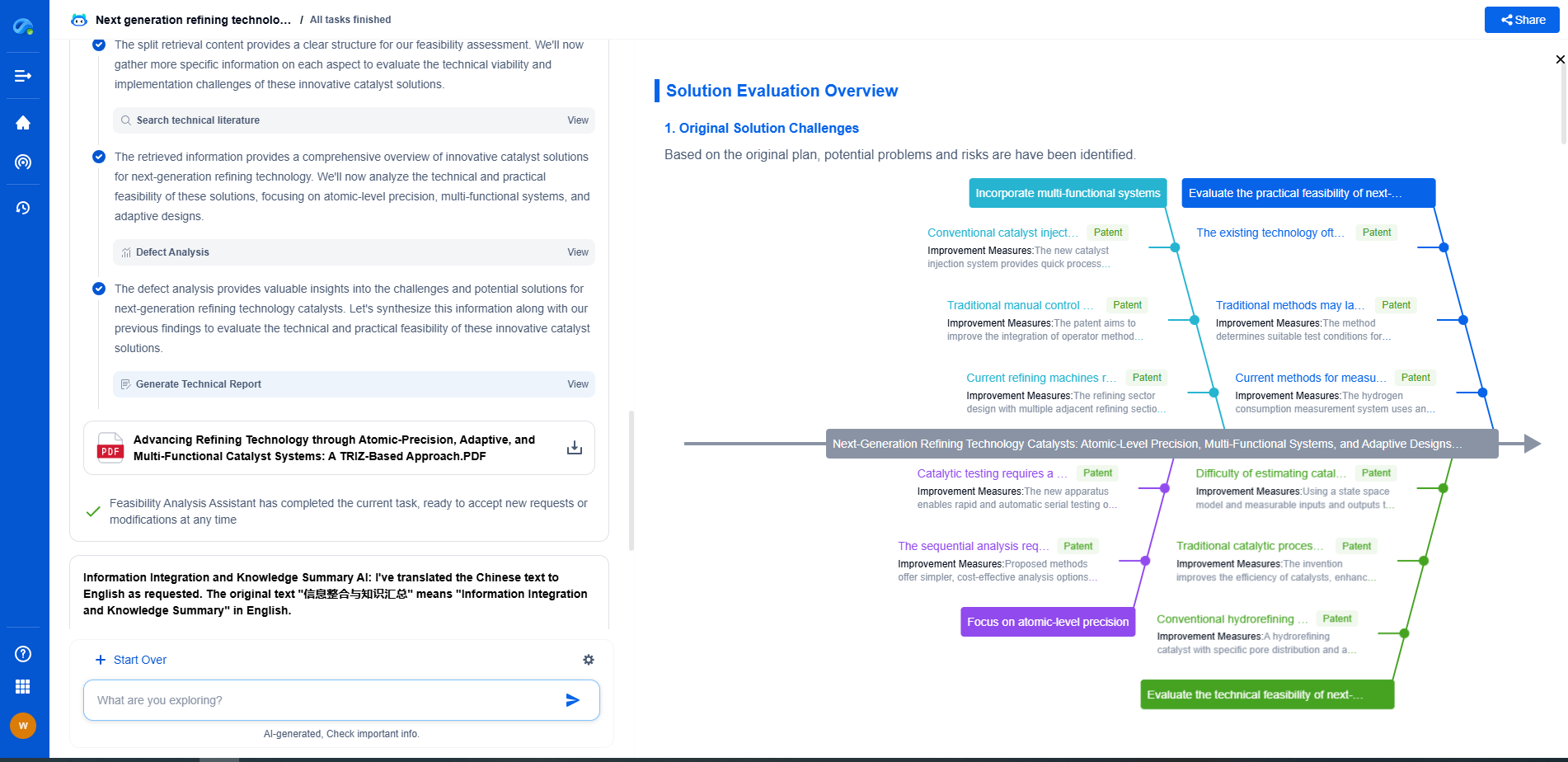

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.