Solving Latency Problems in FPGA-Controlled Systems

JUL 2, 2025 |

Field Programmable Gate Arrays (FPGAs) are widely used in various applications due to their flexibility, high performance, and capacity for parallel processing. However, like any complex system, they can suffer from latency issues that impact overall performance. Understanding and solving latency problems in FPGA-controlled systems is crucial for optimizing their efficiency and reliability.

Causes of Latency in FPGA Systems

There are several factors that can contribute to latency in FPGA systems. First, the inherent architecture of FPGAs, while flexible, can introduce delays. Signal propagation delay, for instance, occurs as signals travel through the routing channels within the FPGA. Additionally, processing latency might arise from the time it takes for the FPGA to complete a given task, especially if the design is not fully optimized.

Another common cause of latency is memory access delays. Accessing external memory resources can introduce significant delays if the data paths are not efficiently managed. Furthermore, the communication between the FPGA and other system components, such as CPUs or peripheral devices, can also be a source of latency. This is often due to the bandwidth limitations or insufficient synchronization between different system parts.

Techniques for Reducing Latency

To address latency issues, engineers can employ a variety of techniques. Firstly, optimizing the FPGA design is paramount. This involves refining the logic design to minimize the number of logic levels that signals have to traverse, thereby reducing propagation delays. Utilizing pipelining techniques can also help by allowing multiple operations to be carried out simultaneously, effectively reducing the processing time for each task.

Efficient memory access strategies are also crucial. Designers can make use of on-chip memory resources, like block RAMs, to minimize the need to access slower external memories. When external memory access is necessary, employing burst access modes or cache systems can significantly improve data throughput and reduce waiting times.

Additionally, improving the communication protocols between the FPGA and other system components is essential. Implementing high-speed interfaces and ensuring efficient handshaking can help mitigate latency introduced by data transfers. In cases where bandwidth is a bottleneck, using compression techniques to reduce the amount of data being transferred can also be beneficial.

Leveraging Parallelism

One of the key advantages of FPGAs is their ability to handle parallel processing efficiently. Exploiting this feature can greatly reduce latency. By designing the FPGA to execute multiple tasks concurrently, the overall system throughput can be increased, effectively lowering the time required for each individual task. For instance, tasks such as data filtering, transformation, and computation can be handled simultaneously rather than sequentially.

Adopting parallelism requires careful planning and design. It is essential to ensure that tasks do not interfere with each other and that resources are allocated efficiently. Load balancing is another consideration, as it ensures that no single processing unit within the FPGA is overburdened, which could otherwise lead to increased latency.

Monitoring and Profiling

To effectively solve latency problems in FPGA systems, continuous monitoring and profiling are necessary. By using tools and methods to profile the system’s performance, engineers can identify specific areas where latency is being introduced. This information can then be used to make informed decisions about where to apply optimization efforts.

Profiling might involve measuring signal propagation times, memory access times, and execution cycles. Moreover, it can be valuable to simulate different scenarios to observe how the system behaves under various conditions. By understanding these factors, engineers can iteratively refine their designs to minimize latency.

Conclusion

Latency in FPGA-controlled systems can significantly impact performance, but through careful design and optimization, it is possible to mitigate these issues. By understanding the causes of latency, employing strategic techniques to reduce it, leveraging parallelism, and continuously monitoring system performance, engineers can enhance the efficiency and reliability of FPGA systems. As technology advances, ongoing research and development in this area are likely to yield even more sophisticated solutions for tackling latency problems.

Ready to Reinvent How You Work on Control Systems?

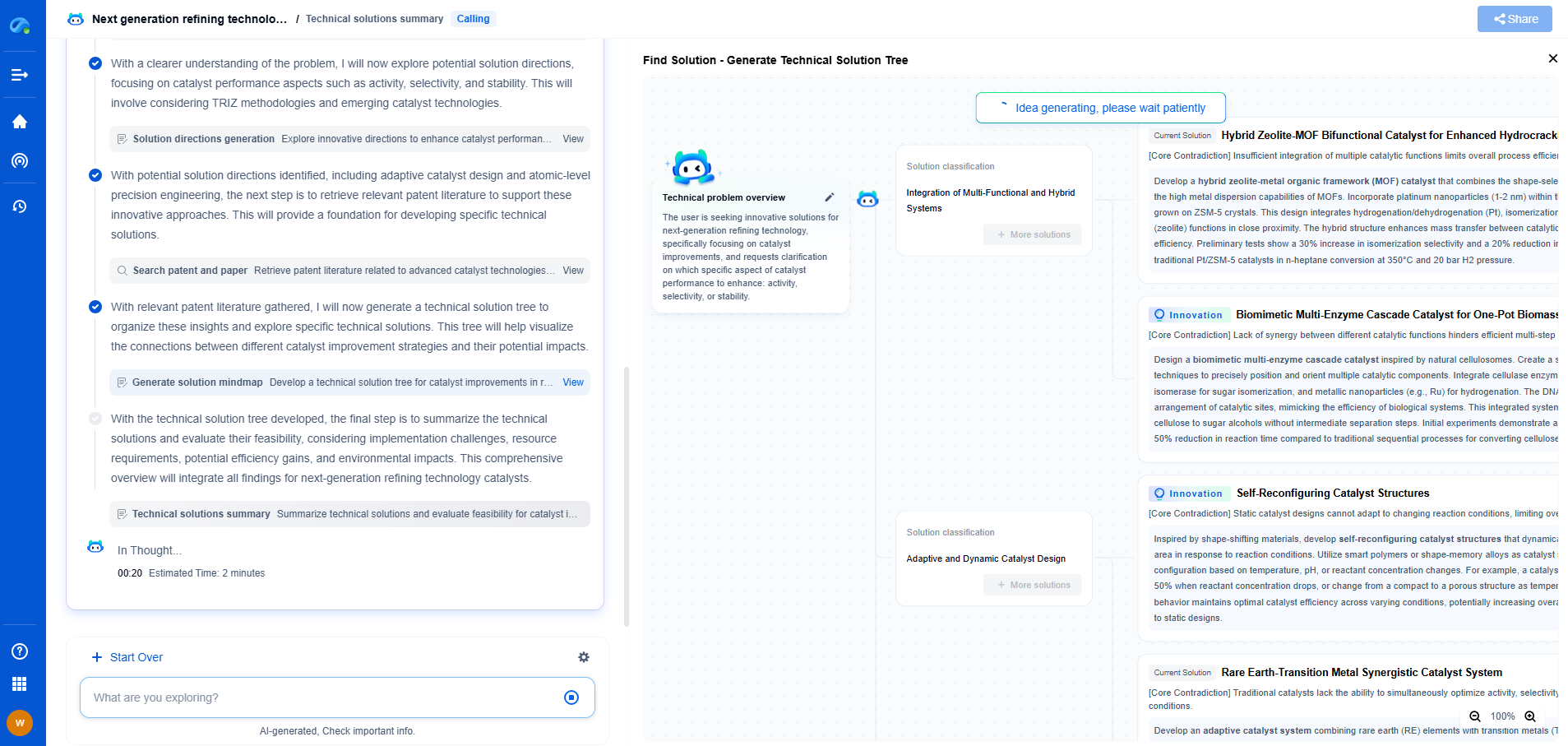

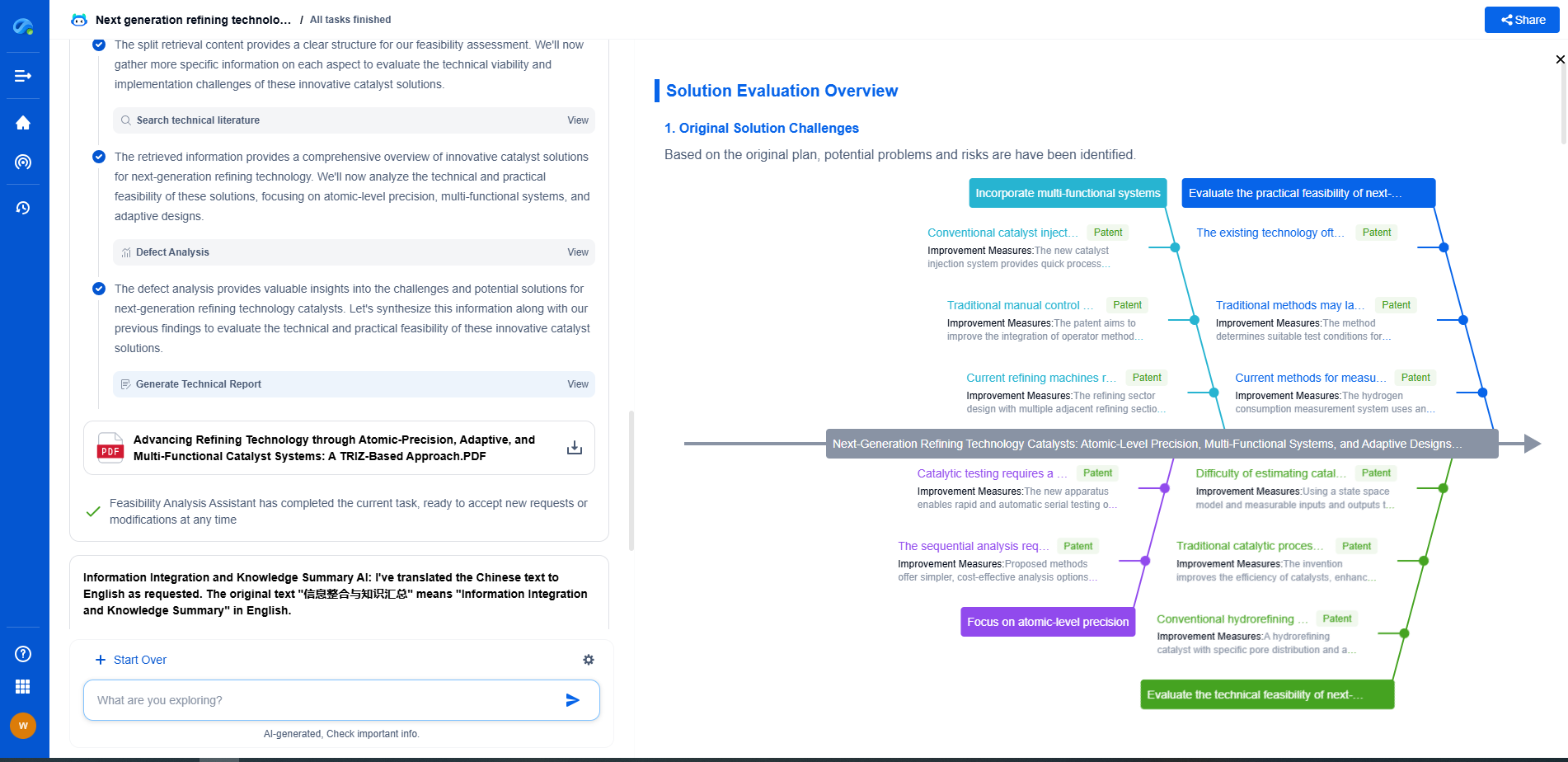

Designing, analyzing, and optimizing control systems involves complex decision-making, from selecting the right sensor configurations to ensuring robust fault tolerance and interoperability. If you’re spending countless hours digging through documentation, standards, patents, or simulation results — it's time for a smarter way to work.

Patsnap Eureka is your intelligent AI Agent, purpose-built for R&D and IP professionals in high-tech industries. Whether you're developing next-gen motion controllers, debugging signal integrity issues, or navigating complex regulatory and patent landscapes in industrial automation, Eureka helps you cut through technical noise and surface the insights that matter—faster.

👉 Experience Patsnap Eureka today — Power up your Control Systems innovation with AI intelligence built for engineers and IP minds.