SPI Clock Skew Problems: How to Synchronize High-Speed Data Transfers

JUL 17, 2025 |

Serial Peripheral Interface (SPI) is a widely-used protocol for short-distance communication, especially in embedded systems. However, as the data transfer rates increase, clock skew becomes a significant challenge. Clock skew occurs when there is a delay between the clock signal reaching different components in the system. This can lead to data misalignment, errors, and even system failures if not properly managed.

Causes of Clock Skew in SPI

Clock skew in SPI systems can arise from several factors. One primary cause is the physical layout of the circuit. Variations in trace lengths on a printed circuit board (PCB) can lead to different propagation times for the clock signal. Components such as capacitors and inductors can also introduce delays. Additionally, variations in temperature and supply voltage can affect the speed at which signals propagate through the circuit.

Impacts of Clock Skew

The impact of clock skew can be severe, especially in high-speed data transfers. Data might be sampled at the wrong time, leading to incorrect values being read. This can result in communication errors between the master and slave devices. In the worst-case scenario, significant clock skew can lead to complete communication breakdown, causing the system to malfunction.

Strategies to Mitigate Clock Skew

1. Careful PCB Design

One of the most effective ways to mitigate clock skew is by careful PCB design. Ensuring that trace lengths for the clock and data lines are equal can minimize skew. Using controlled impedance traces and paying attention to the layer stack-up can also help in reducing delays due to parasitic capacitance and inductance.

2. Use of Synchronization Techniques

Synchronization techniques, such as using a delay-locked loop (DLL) or a phase-locked loop (PLL), can help in aligning the clock signal at different points in the system. These techniques allow for dynamic adjustment of the clock phase, compensating for any skew introduced by the system.

3. Incorporating Buffering

Incorporating buffering techniques can also help in managing clock skew. By introducing buffers along the clock path, the system can help equalize any differences in propagation delays, ensuring that data is sampled accurately.

4. Differential Signaling

Using differential signaling instead of single-ended signaling can help reduce the effects of clock skew. Differential signaling is less susceptible to noise and can provide more consistent timing signals, reducing the chances of skew-related errors.

5. Temperature and Voltage Compensation

Implementing temperature and voltage compensation in the system can help mitigate skew caused by environmental factors. By monitoring and adjusting for temperature and voltage variations, the system can maintain more consistent performance.

Conclusion

Clock skew is a critical challenge in high-speed SPI data transfers. Understanding its causes and impacts is crucial for designing robust systems. By implementing strategies such as careful PCB design, synchronization techniques, and environmental compensation, engineers can effectively manage clock skew, ensuring reliable and accurate data communication. As technology continues to advance and data rates increase, addressing clock skew will remain a vital aspect of system design and optimization.

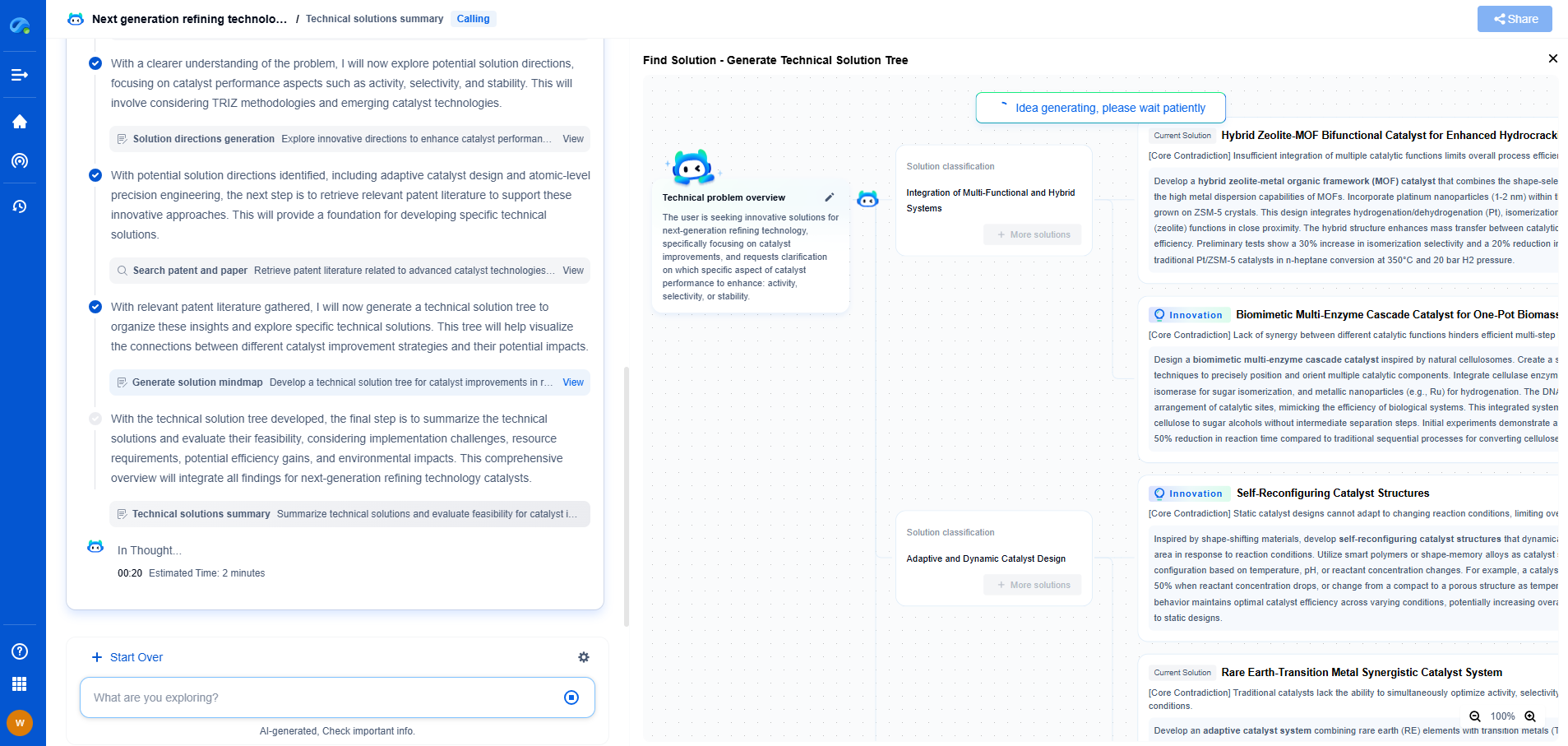

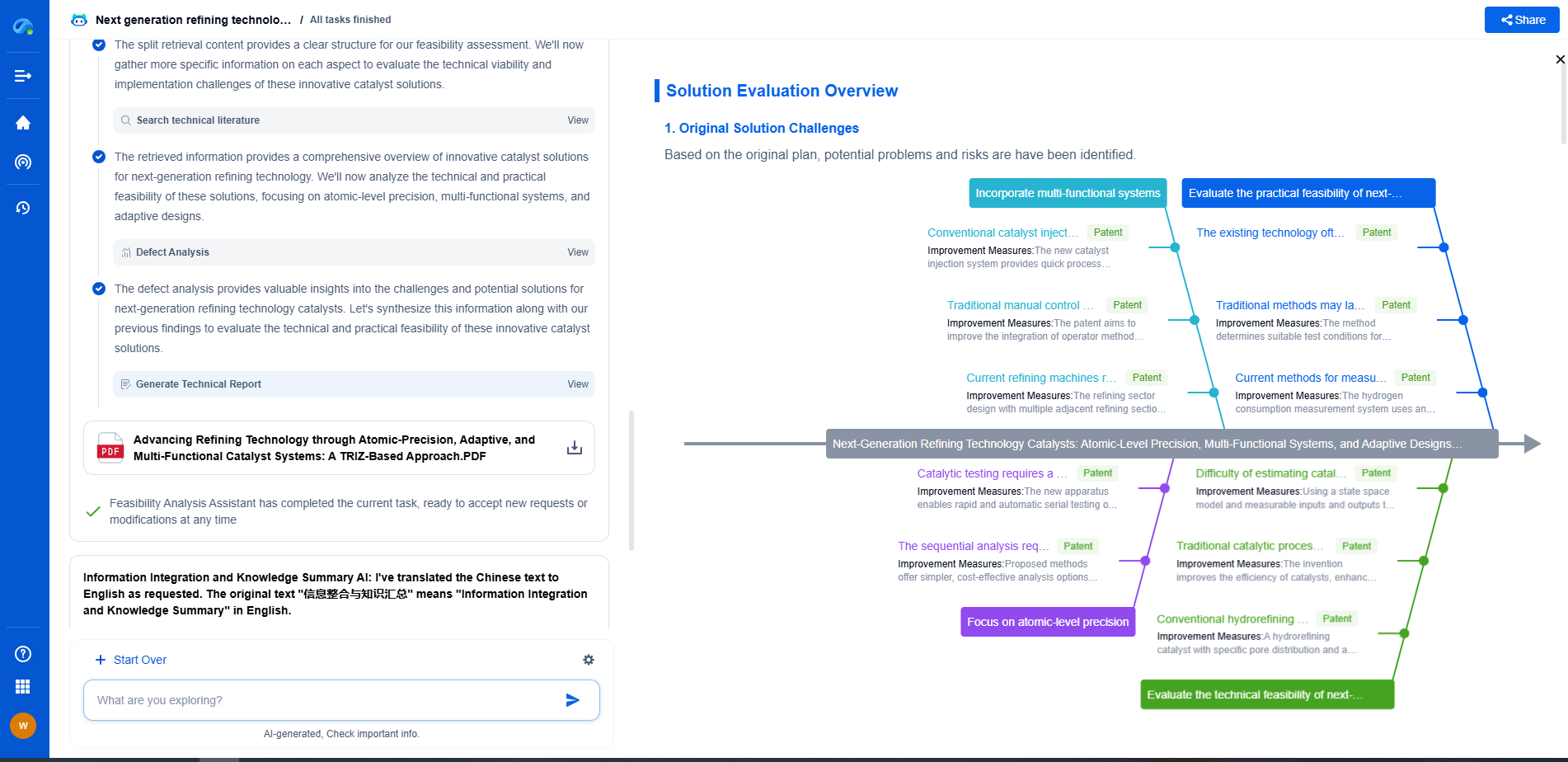

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.