Stochastic defects in EUV lithography: Origins, types, and impact

JUL 28, 2025 |

Extreme Ultraviolet (EUV) lithography is a cutting-edge technology that has revolutionized the semiconductor manufacturing industry. It allows for the production of smaller, more powerful, and more efficient chips. However, as with any advanced technology, EUV lithography is not without its challenges. One of the most significant challenges faced by manufacturers is the presence of stochastic defects. These random and unpredictable defects can have profound implications for the overall yield, performance, and reliability of semiconductor devices.

Origins of Stochastic Defects in EUV Lithography

The origins of stochastic defects are rooted in the inherent nature of the EUV lithography process. Unlike traditional photolithography which uses longer wavelengths of light, EUV lithography employs a 13.5 nm wavelength. This shorter wavelength is essential for producing the fine features required for advanced semiconductor nodes. However, it also introduces a degree of randomness into the process. At this scale, variations in the exposure dose, resist chemistry, and photon shot noise can all contribute to the formation of stochastic defects. Additionally, the materials used in the EUV process, such as photoresists and masks, can also be sources of variability, further complicating defect control.

Types of Stochastic Defects

Stochastic defects in EUV lithography can be broadly classified into several categories:

1. Line-Edge Roughness (LER) and Line-Width Roughness (LWR): These defects occur due to variations in the edges and widths of the lines patterned on the wafer. They are primarily caused by resist-related issues and can lead to significant variability in device performance.

2. Missing Contacts or Vias: These defects arise when the EUV exposure dose is insufficient or when there are issues with the development process. Missing contacts can lead to open circuits, severely impacting device functionality.

3. Bridging Defects: These occur when unintended connections are formed between two features. Bridging is often a result of dose variations and resist collapse during development, leading to short circuits.

4. Random Bridge or Break: These defects are a combination of bridging and missing features and are often the result of variations in the EUV process conditions.

Impact of Stochastic Defects on Semiconductor Manufacturing

The presence of stochastic defects poses significant challenges in semiconductor manufacturing. These defects can result in reduced yield, as chips with defects are often rendered unusable. In addition to impacting yield, stochastic defects can also affect device performance and reliability. For instance, line-edge roughness can lead to variability in transistor performance, which in turn can affect the overall speed and power consumption of a chip.

Furthermore, addressing stochastic defects requires additional process steps and tighter process controls, leading to increased manufacturing costs. It may also necessitate more rigorous testing and quality control measures to ensure that only defect-free chips reach the market.

Mitigation Strategies

To mitigate the impact of stochastic defects, manufacturers are employing several strategies. Advances in photoresist materials and formulations are being explored to reduce line-edge roughness and improve process stability. Additionally, improvements in the design and fabrication of EUV masks are crucial in minimizing mask-related defects.

Optimization of process conditions, including exposure dose and development parameters, is also critical in reducing defectivity. Advanced metrology and inspection techniques are being developed to detect and characterize defects more effectively, enabling prompt corrective actions.

Conclusion

Stochastic defects in EUV lithography are a significant challenge that the semiconductor industry must address to fully realize the potential of this advanced technology. Understanding the origins and types of these defects is crucial in developing effective mitigation strategies. While progress is being made, ongoing research and development efforts are essential to overcome these challenges and ensure the continued advancement of semiconductor technology. As manufacturers refine their processes and technologies, the impact of stochastic defects will likely diminish, paving the way for the next generation of high-performance, reliable semiconductor devices.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

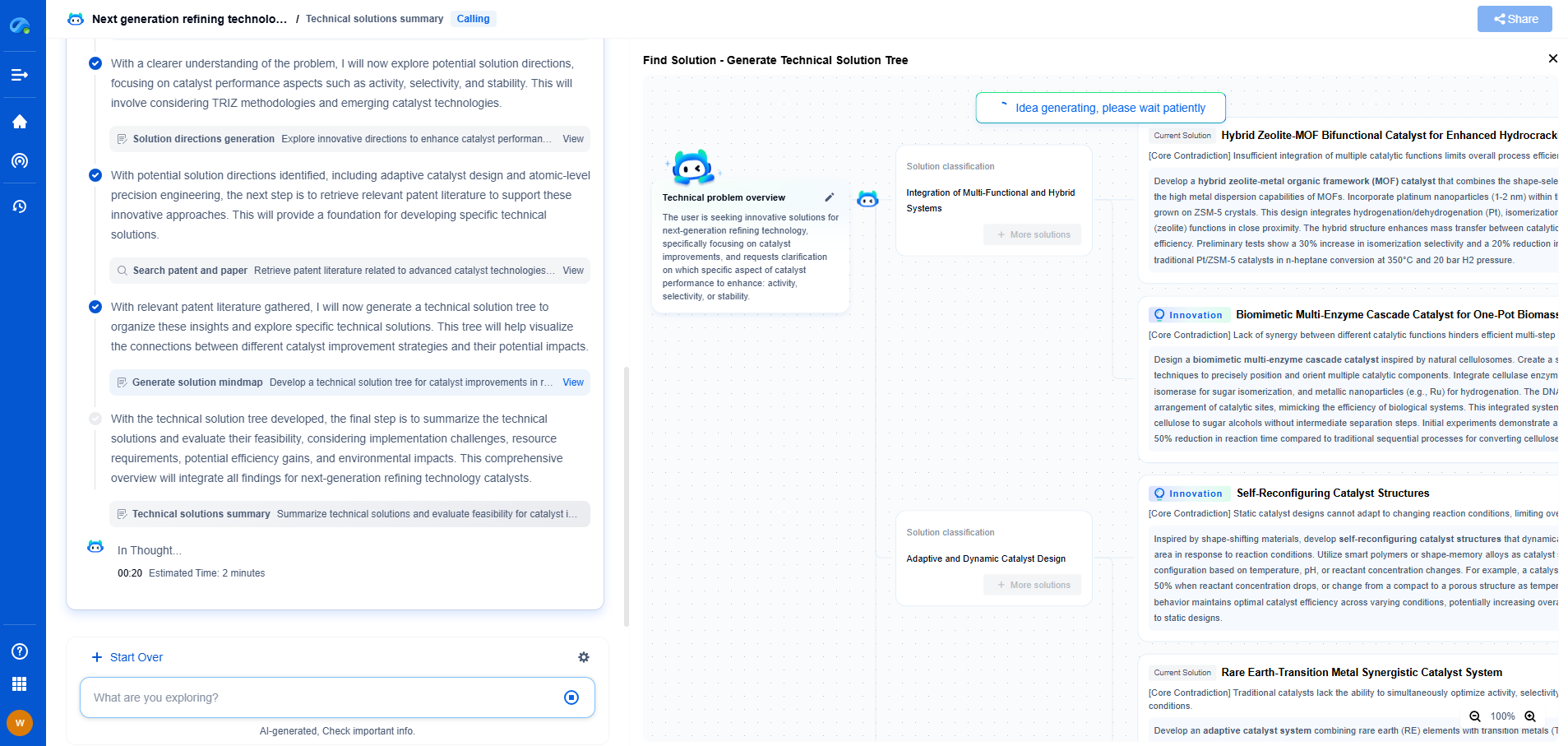

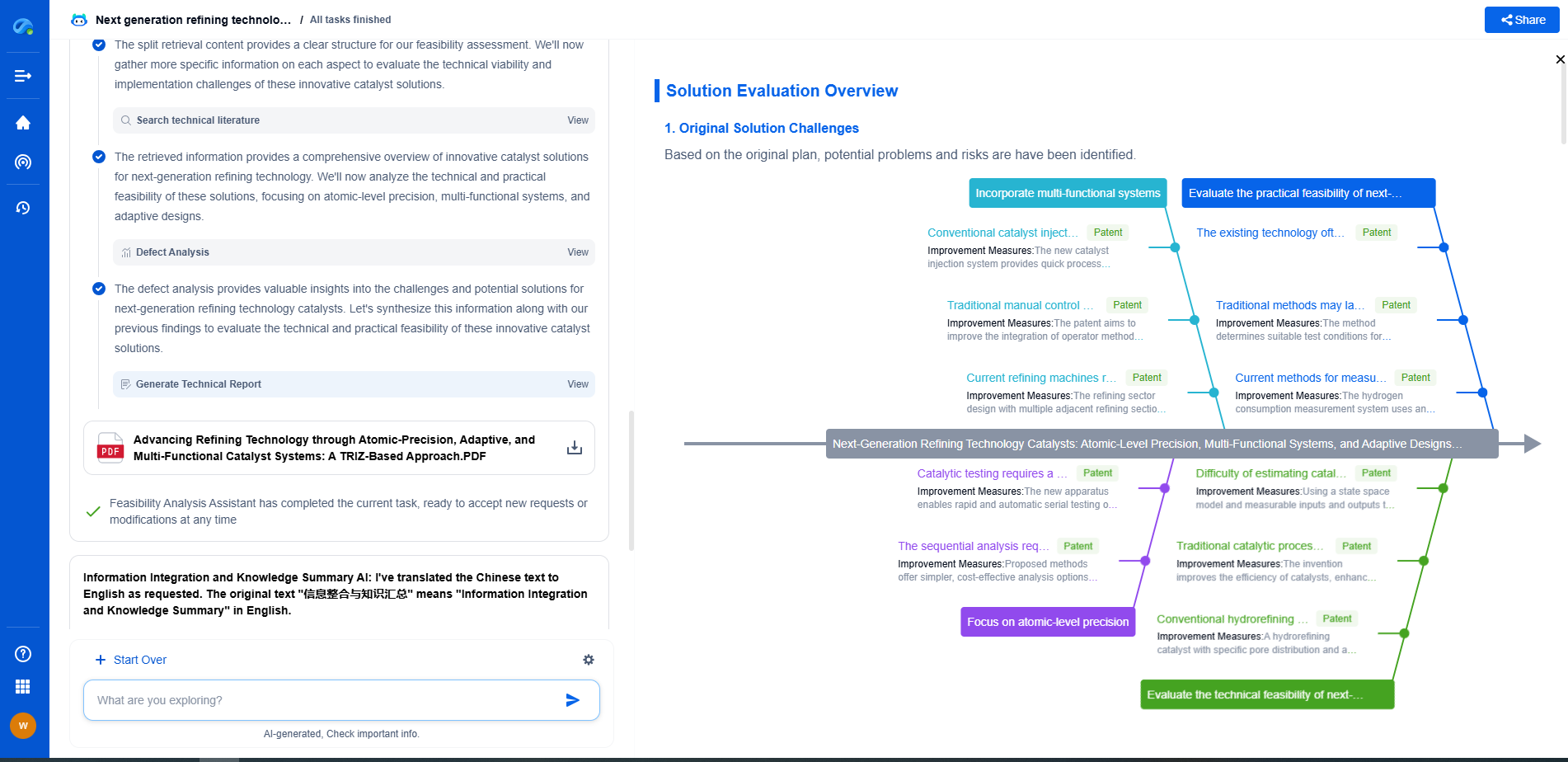

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com