The Impact of Clock Jitter on High-Speed Measurement Accuracy

JUL 17, 2025 |

In the realm of high-speed measurements, the precision and accuracy of data acquisition are paramount. One of the critical factors that can significantly affect these measurements is clock jitter. Clock jitter refers to the small, rapid variations in the timing of a clock signal. While these deviations might seem negligible, they can introduce substantial errors in high-speed systems, where precision timing is crucial. This blog delves into the impact of clock jitter on high-speed measurement accuracy and explores potential solutions to mitigate its effects.

Understanding Clock Jitter

Clock jitter is a phenomenon that arises from the inherent imperfections in clock generation systems. It can manifest as phase jitter, where the clock edge timing varies, or as period jitter, which affects the clock cycle duration. In high-speed applications, where measurements are taken in the gigahertz range, even picoseconds of jitter can lead to significant discrepancies in data interpretation.

Impact on High-Speed Measurements

When clock jitter is present, it can distort the timing of digital signals, leading to errors in data sampling and conversion. In applications such as telecommunications, data centers, and high-frequency trading, precise timing is critical for synchronization and data integrity. Jitter can cause misalignment in signal sampling, resulting in bit errors and degraded signal-to-noise ratios.

Clock jitter also affects analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) used in high-speed data acquisition systems. For ADCs, jitter can cause errors in the conversion process, as the sampling instant might not align with the actual signal waveform. This misalignment can introduce distortion and noise into the digitized signal, affecting the overall accuracy of the measurement.

Factors Contributing to Clock Jitter

Several factors contribute to clock jitter, including thermal noise, power supply variations, and electromagnetic interference. Device imperfections, such as variations in semiconductor manufacturing processes, can also introduce jitter. Understanding these contributing factors is essential for designing systems that are resilient to jitter.

Mitigation Strategies

To minimize the impact of clock jitter on high-speed measurements, several strategies can be employed. One approach is to use low-jitter clock sources, such as crystal oscillators, which offer better stability and precision. Additionally, employing phase-locked loops (PLLs) and jitter-cleaning circuits can help reduce jitter by filtering out noise and aligning clock signals.

Another critical strategy is to optimize the design of the measurement system. This includes careful layout of printed circuit boards (PCBs) to minimize electromagnetic interference, using differential signaling to reduce susceptibility to noise, and ensuring stable power supply lines. Signal integrity analysis tools can also be used to simulate and verify the impact of jitter on system performance, allowing for proactive design adjustments.

Additionally, advanced digital signal processing (DSP) techniques can compensate for the effects of jitter in post-processing. By analyzing the characteristics of the jitter and applying corrective algorithms, it is possible to enhance the accuracy of the measured data.

Conclusion

Clock jitter poses a significant challenge in high-speed measurement systems, affecting the precision and accuracy of data acquisition. Understanding the nature of jitter and its impact on measurement accuracy is crucial for engineers and designers working in high-speed applications. By implementing robust design strategies and employing advanced technologies, it is possible to mitigate the effects of clock jitter and ensure the integrity of high-speed measurements. As technology continues to evolve, the demand for precise timing will only increase, making the management of clock jitter an essential aspect of modern high-speed systems.

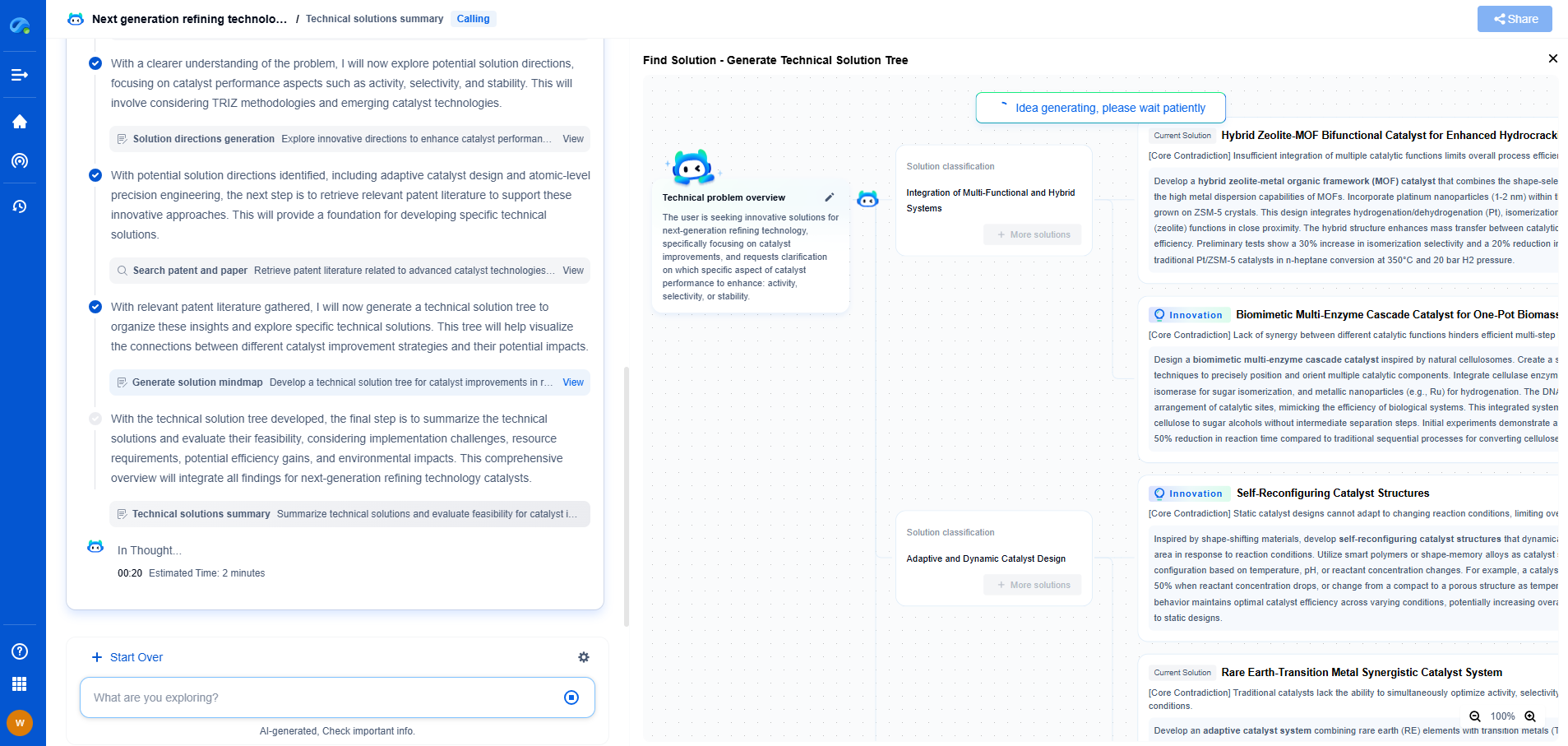

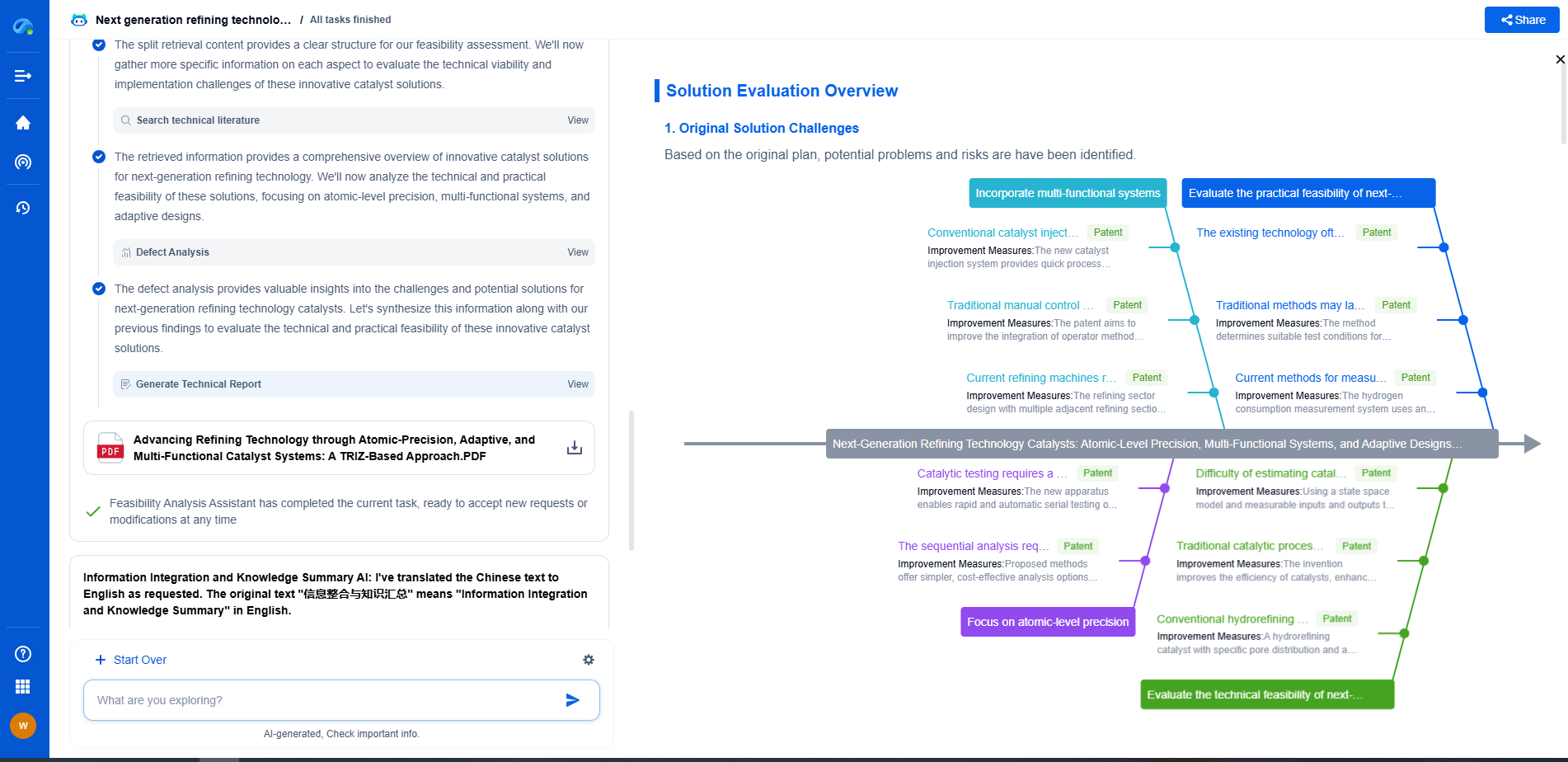

Whether you’re developing multifunctional DAQ platforms, programmable calibration benches, or integrated sensor measurement suites, the ability to track emerging patents, understand competitor strategies, and uncover untapped technology spaces is critical.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🧪 Let Eureka be your digital research assistant—streamlining your technical search across disciplines and giving you the clarity to lead confidently. Experience it today.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com