The Rise of Chiplet-Based Architecture and Packaging Challenges

JUN 27, 2025 |

In the realm of semiconductor technology, the race to enhance computing performance while managing power efficiency and cost is perpetual. Traditional monolithic chip designs have driven the innovations so far, but as we approach the limits of Moore's Law, a new contender is gaining momentum: chiplet-based architecture. This method is revolutionizing the industry by allowing manufacturers to design complex systems by combining smaller, functional chips, or chiplets, into a single package. This approach not only provides flexibility and scalability but also presents unique challenges, particularly in the realm of packaging.

Advantages of Chiplet-Based Design

One of the primary advantages of chiplet-based architecture is its modularity. By using chiplets, manufacturers can mix and match different functionalities like CPUs, GPUs, and memory components to create a tailored solution for specific applications. This modularity accelerates innovation and reduces time-to-market since individual chiplets can be developed and optimized independently.

Moreover, chiplet design allows for better yield management. In traditional monolithic chips, a defect in any part can render the entire chip unusable. Chiplets, however, can be individually tested and replaced, improving the yield and reducing the cost of production. This results in significant cost savings and more efficient use of resources, which is crucial given the rising expense of semiconductor fabrication.

Performance and Scalability

Chiplet-based designs also provide significant performance boosts. By enabling closer integration of heterogeneous components, they allow for efficient data transfer and communication between chiplets. This proximity minimizes latency and power consumption, enhancing the overall performance of the system. Furthermore, chiplets facilitate the scaling of performance with relative ease. Instead of designing a new monolithic chip to achieve higher performance, manufacturers can simply add more chiplets tuned to the desired specifications. This scalability is crucial in meeting the ever-increasing demands for computational power in areas such as AI, gaming, and data centers.

Packaging Challenges

Despite their advantages, chiplet-based architectures introduce several packaging challenges. Packaging in this context refers to the housing and interconnection of chiplets to form a cohesive unit that functions as intended. One key challenge is the development of high-density interconnects that can support the increased data rates while maintaining signal integrity. Achieving this requires advances in materials and techniques, such as through-silicon vias (TSVs) and advanced substrate technologies.

Thermal management is another significant concern. As more chiplets are packed into a smaller area, dissipating the generated heat becomes more challenging. Effective thermal solutions are necessary to prevent overheating, which can degrade performance and reliability. This demands innovation in cooling technologies and materials that can efficiently transfer and dissipate heat.

Additionally, designing a package that accommodates the diverse requirements of different chiplets—each with its own power, thermal, and signal characteristics—requires careful consideration and sophisticated engineering. Ensuring compatibility and seamless communication between heterogeneous chiplets is a non-trivial task that necessitates precise control over power delivery, clock distribution, and signal integrity.

Future Prospects and Innovations

The rise of chiplet-based architecture is poised to continue as the industry seeks to overcome the limitations of traditional chip designs. Collaborative efforts among industry leaders, such as the development of open standards for chiplet interfaces, are paving the way for more widespread adoption. These standards will facilitate interoperability between chiplets from different manufacturers, further enhancing the modularity and flexibility of chiplet-based systems.

Moreover, ongoing research in advanced packaging techniques, including 3D stacking and wafer-level packaging, promises to address many of the current challenges. These innovations will enable more efficient integration of chiplets and open new avenues for performance improvements and cost reductions.

Conclusion

Chiplet-based architecture represents a significant shift in semiconductor design and manufacturing. By offering modularity, improved yields, and enhanced performance, it addresses many of the challenges faced by traditional monolithic chips. However, the packaging of these chiplets remains a critical hurdle that must be overcome to fully realize their potential. As the industry continues to innovate and collaborate, chiplet-based designs are likely to play an increasingly vital role in the future of computing, driving the next wave of technological advancements.

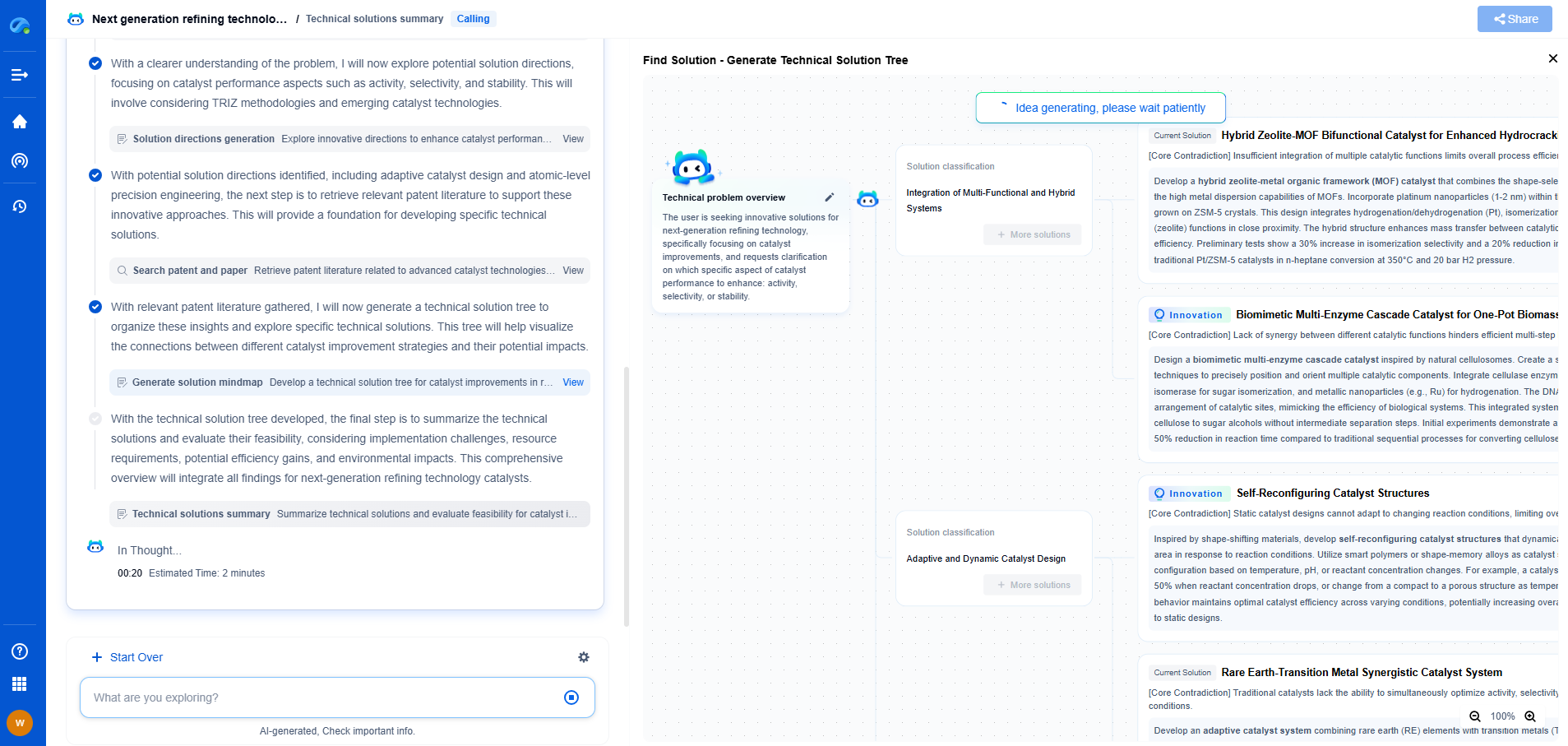

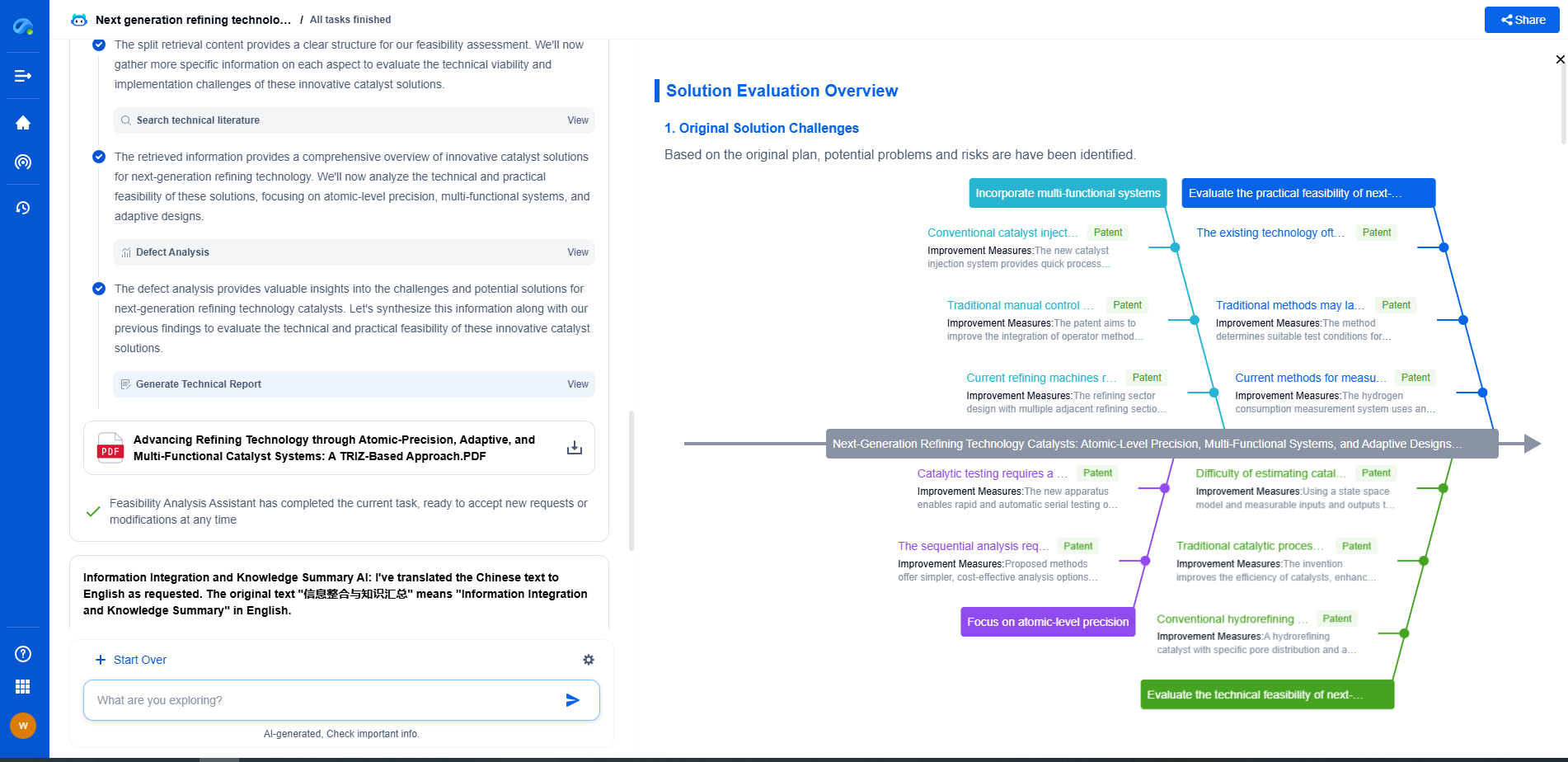

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com