Wafer-Level Capacitor Fabrication: Thin-Film Deposition and Dicing Challenges

JUL 9, 2025 |

Wafer-level fabrication of capacitors is a critical process in the semiconductor industry, particularly for producing components that are increasingly miniaturized and integrated. As the demand for smaller, more efficient electronic devices grows, the challenges associated with thin-film deposition and dicing in wafer-level capacitor fabrication become even more pronounced. This blog explores these challenges and discusses potential solutions to optimize the process.

Thin-Film Deposition Techniques

Thin-film deposition is a core step in the fabrication of wafer-level capacitors. It involves depositing a thin layer of dielectric material onto a substrate to form the capacitor's insulating layer. Several techniques are used, including chemical vapor deposition (CVD), physical vapor deposition (PVD), and atomic layer deposition (ALD). Each method has its advantages and specific applications.

CVD is often preferred for its ability to create uniform layers over large areas, making it ideal for high-throughput production. However, it can be challenging to control the film's thickness precisely, which is critical for capacitors where dielectric properties are highly dependent on film thickness.

PVD, including techniques like sputtering, offers better control over thickness and composition. It's particularly useful for depositing metals or metal oxides used in capacitors. However, achieving uniformity over large wafers can be more complex compared to CVD.

ALD offers atomic-level control of thickness and composition, resulting in highly uniform and conformal films. This makes it ideal for high-precision applications, though it may be slower and more expensive compared to other methods.

Challenges in Thin-Film Deposition

Achieving a balance between film uniformity, deposition rate, and material properties is a significant challenge in thin-film deposition. Variations in film thickness can lead to inconsistent electrical properties, affecting the capacitor's performance. Additionally, deposition methods must be carefully selected based on the specific materials and desired properties of the final capacitor.

Contamination and defects introduced during deposition can also pose significant challenges. These can affect the reliability and longevity of the capacitors. Ensuring a clean environment and using high-purity materials are essential to mitigate these issues.

Dicing Challenges in Wafer-Level Fabrication

Once the thin-film deposition process is complete, the wafer must be diced into individual capacitors. Dicing involves cutting the wafer into separate pieces, and this process is fraught with challenges. Mechanical dicing, which uses a saw to cut through the wafer, can introduce stress and defects, potentially damaging the delicate thin films deposited earlier.

Laser dicing offers a non-contact alternative, reducing mechanical stress but introducing its own set of challenges, such as thermal damage and the need for precise control to avoid altering the material properties of the wafer.

Managing edge chipping and ensuring clean, smooth cuts are critical to maintaining the integrity of the capacitors. Advanced dicing techniques, such as stealth dicing, which uses a laser to create internal modifications followed by mechanical breaking, can help address some of these issues by minimizing surface damage.

Solutions and Innovations

To overcome these challenges, innovations in both deposition and dicing technologies are essential. In deposition, combining different techniques, such as using ALD for a seed layer followed by PVD for bulk deposition, can help achieve the desired properties while maintaining efficiency.

In dicing, integrating real-time monitoring and feedback systems can improve precision and reduce defects. The development of new materials and coatings that enhance the robustness of the wafers during dicing is also an area of active research.

Conclusion

Wafer-level capacitor fabrication is a complex process that requires careful consideration of both thin-film deposition and dicing challenges. As the demand for advanced electronic devices continues to grow, the industry must continually innovate to improve these processes. By understanding and addressing the specific challenges associated with thin-film deposition and dicing, manufacturers can enhance the performance and reliability of their capacitors, helping to drive the next generation of electronic devices.

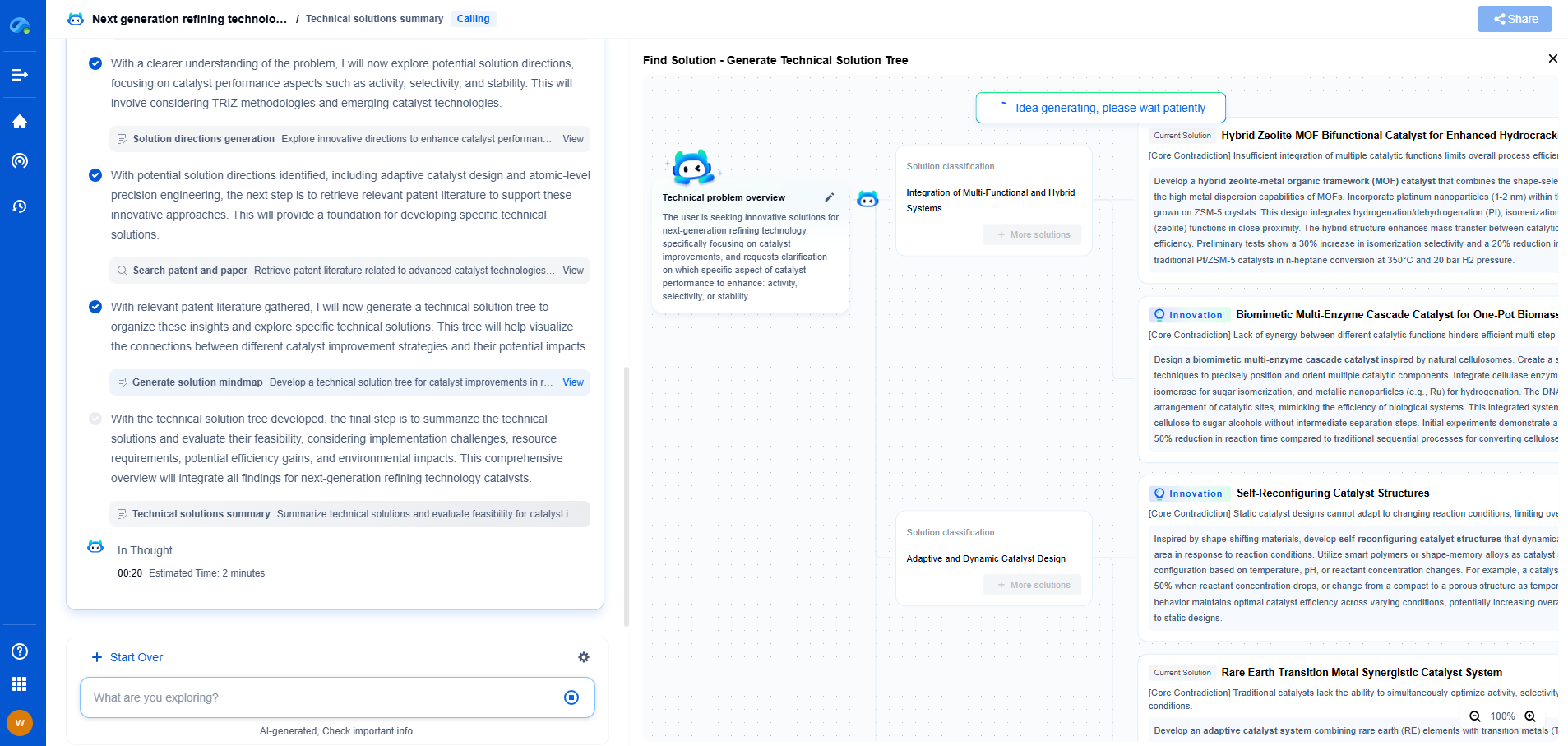

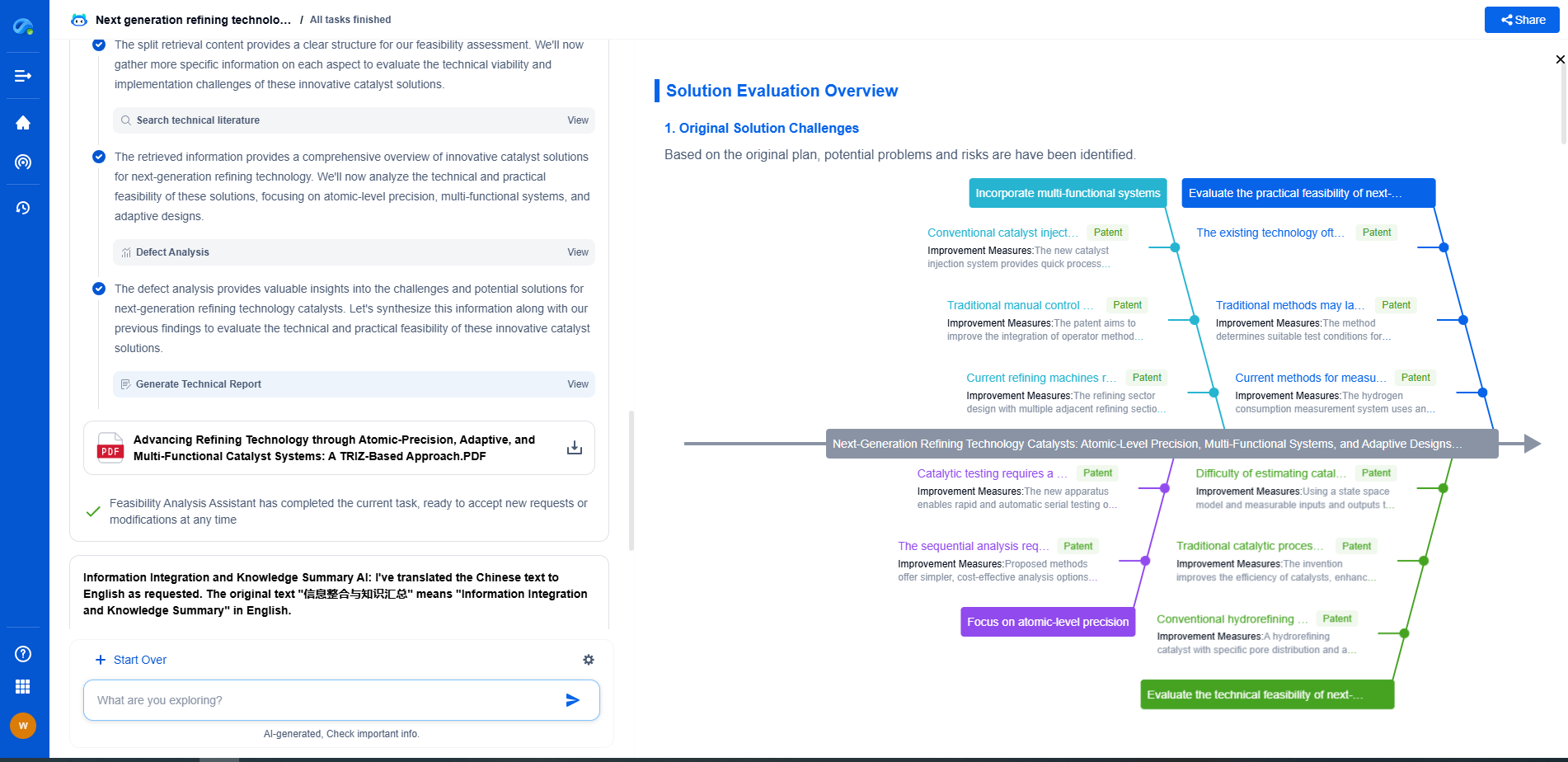

Looking to accelerate your capacitor innovation pipeline?

As capacitor technologies evolve—from miniaturized MLCCs for smartphones to grid-scale energy storage devices—so must the way your team accesses critical knowledge.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Try Patsnap Eureka now and discover a faster, smarter way to research and innovate in capacitor technology.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com