Wafer-Level CSP (WLCSP): Ultra-Miniature Packaging for Wearables

JUN 27, 2025 |

In the rapidly evolving world of wearable technology, the demand for smaller, more efficient components is ever-growing. As consumers seek devices that are not only functional but also discreet and stylish, manufacturers are continually pushed to innovate. One such innovation that has proven crucial in this miniaturization drive is the Wafer-Level Chip Scale Package (WLCSP). Unlike traditional packaging methods that involve multiple steps after wafer fabrication, WLCSP simplifies the process by packaging the die at the wafer level, resulting in a smaller, more efficient product.

The Basics of WLCSP

Wafer-Level Chip Scale Packaging stands out due to its unique ability to package integrated circuits within the dimensions of the die itself. This is achieved by redistributing the I/O pads and adding solder bumps directly to the wafer, which allows for direct mounting onto a printed circuit board (PCB) without the need for additional packaging. This method not only reduces the overall size of the component but also enhances electrical performance by minimizing parasitic inductance and capacitance.

Advantages of WLCSP in Wearables

The primary advantage of WLCSP for wearable devices is its ultra-miniature size. As wearables become more sophisticated, integrating features like biometric sensors, GPS, and wireless capabilities, the space available on PCBs becomes a premium commodity. WLCSP allows for the accommodation of more components in the same space, empowering designers to deliver enhanced functionality without increasing device dimensions.

Moreover, WLCSP offers improved thermal performance. In wearables, where heat dissipation is a key concern, this packaging method allows for better heat distribution across the device's surface. Additionally, WLCSP's reduced lead inductance translates to better signal integrity and fast signal transmission, crucial for devices that rely on real-time data processing and communication.

Challenges and Considerations

Despite its advantages, WLCSP is not without challenges. One significant concern is the mechanical robustness of the solder joints, especially in devices that undergo frequent movement and flexing, as is common with wearables. This can lead to fatigue failures over time. Therefore, engineers must carefully consider materials and design to ensure reliability throughout the device's lifespan.

The thermal expansion mismatch between the silicon die and the PCB material is another challenge. This mismatch can lead to stress during thermal cycling, which may cause reliability issues. Manufacturers often employ underfill materials or adopt flexible substrates to mitigate these risks.

Future Trends and Innovations

The trend towards miniaturization is set to continue, with WLCSP playing a pivotal role in this evolution. Future innovations are likely to focus on enhancing the material properties used in WLCSP to further improve its reliability and performance. As 5G technology and the Internet of Things (IoT) expand, the need for efficient, high-performance packaging like WLCSP will become even more critical.

Furthermore, advancements in materials science may lead to the development of new alloys and polymers that can better withstand the mechanical and thermal stresses associated with wearable technology. This ongoing research and development will ensure that WLCSP remains at the forefront of packaging technology for wearables and other compact electronic devices.

Conclusion

Wafer-Level Chip Scale Packaging represents a significant leap forward in the miniaturization of electronic components, particularly for wearable technology. Its compact size, enhanced performance, and cost-effectiveness make it an attractive option for manufacturers looking to innovate in the competitive wearables market. As technology advances and consumer demands continue to rise, WLCSP will undoubtedly play an essential role in shaping the future of wearable devices, enabling them to become more powerful, versatile, and seamlessly integrated into our daily lives.

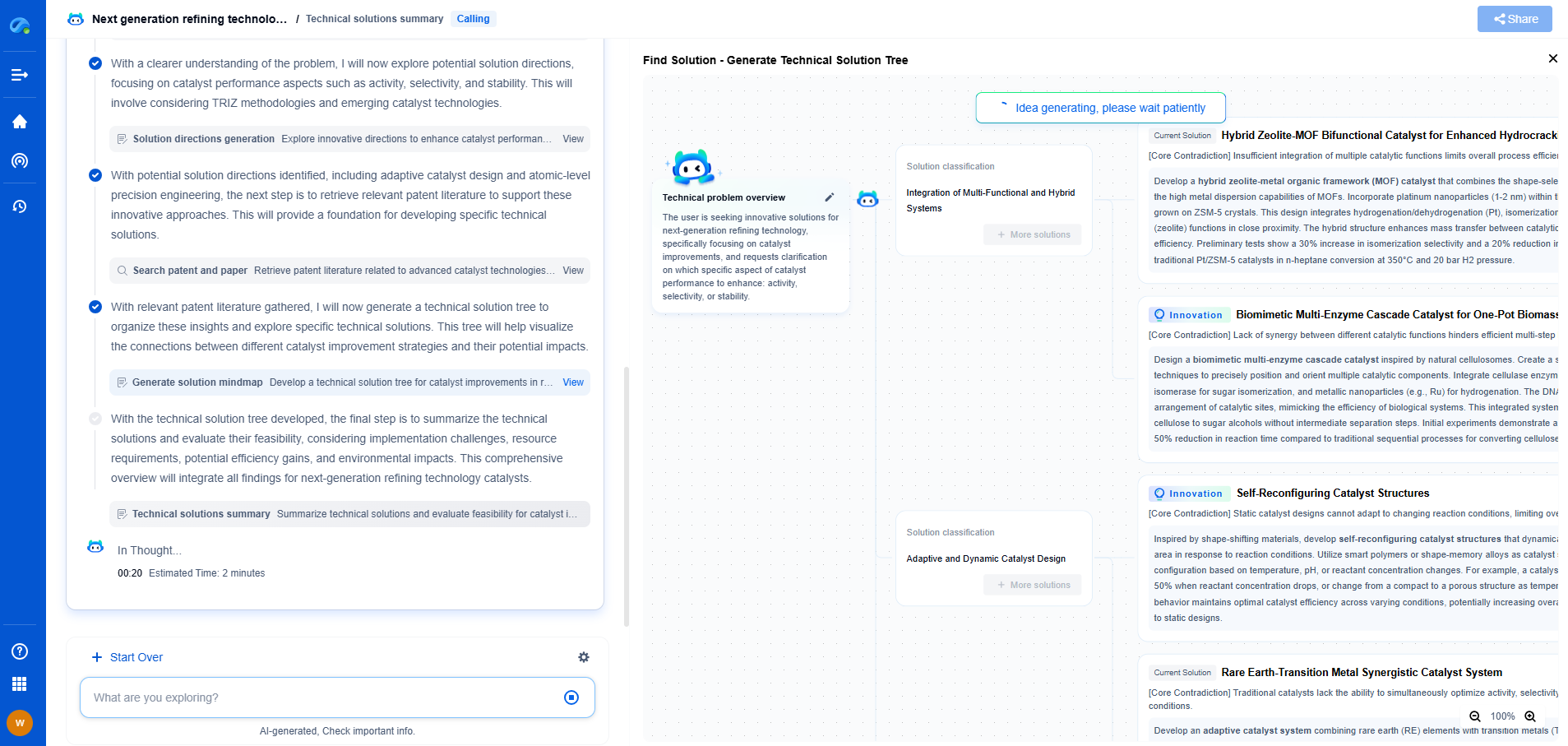

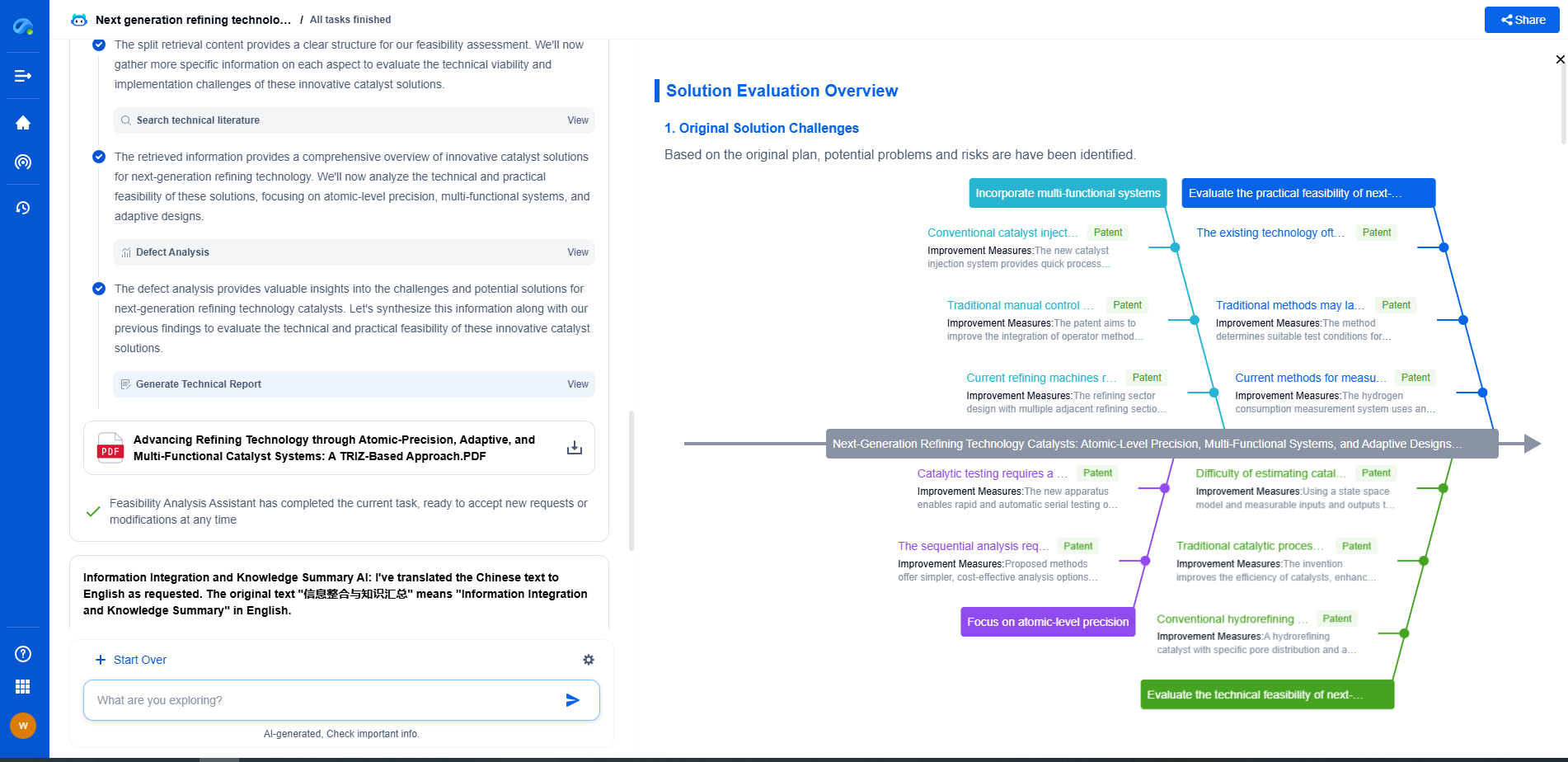

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com