What Is 3D IC Integration and How Does It Differ from 2.5D Packaging?

JUN 27, 2025 |

As technology continues to evolve, the need for more efficient, faster, and compact semiconductor devices has become paramount. Enter 3D Integrated Circuit (IC) integration, a revolutionary approach that stacks multiple layers of active electronic components vertically. This results in a single, compact chip that not only saves space but also improves performance due to shorter interconnects.

3D IC integration involves the use of Through-Silicon Vias (TSVs), which are vertical electrical connections passing through silicon wafers or dies. These TSVs significantly reduce the distance data has to travel, thus lowering latency and power consumption while increasing bandwidth. Such a configuration is beneficial for applications that demand high performance and efficiency, such as advanced computing, mobile devices, and high-frequency trading platforms.

Advantages of 3D IC Integration

The primary advantage of 3D IC integration is the potential for greater performance and energy efficiency. By stacking chips vertically, designers can pack more functionality into a smaller footprint. Additionally, 3D ICs can offer better heat dissipation compared to traditional 2D designs, as heat can be distributed more evenly across the layers of the chip.

Moreover, 3D IC integration provides designers with the flexibility to integrate heterogeneous technologies, allowing for the combination of different types of circuits—such as analog, digital, RF, and even photonic circuits—on a single chip. This versatility can lead to innovative products with enhanced capabilities.

Introduction to 2.5D Packaging

While 3D IC integration is a full-fledged stacking of multiple active layers, 2.5D packaging offers a different approach. In 2.5D packaging, multiple chips or dies are placed side-by-side on an interposer, which is a substrate that acts as a bridge for electrical connections. This setup allows for the integration of multiple chips without them being directly stacked on top of one another.

The interposer typically consists of a silicon wafer with TSVs that facilitate communication between the chips seated on its surface. Though not a true 3D structure, 2.5D packaging offers many benefits, including reducing the complexity of chip-to-chip communication, which can enhance performance and reliability compared to traditional planar designs.

Key Differences Between 3D IC Integration and 2.5D Packaging

Despite their similarities in aiming to boost performance and reduce form factor, 3D IC integration and 2.5D packaging are fundamentally different in their approaches and applications.

1. Structure: The most apparent difference is in their structure. 3D IC integration involves stacking chips vertically with direct connections through TSVs, whereas 2.5D packaging places chips side-by-side on a shared interposer.

2. Complexity and Cost: 3D ICs generally involve more complex manufacturing processes due to the need for precise alignment of the stacked layers and the integration of TSVs. This can make them more expensive compared to 2.5D solutions, which, while still intricate, pose fewer challenges in stacking and alignment.

3. Performance: While both methods aim to improve performance, the vertical stacking in 3D ICs often results in lower latency and power consumption due to shorter interconnects. However, 2.5D packaging still offers significant performance benefits over traditional 2D designs, especially in applications where direct chip-to-chip communication is essential.

4. Applications: 3D IC integration is often favored in high-performance, space-constrained applications such as high-end computing and portable electronics. In contrast, 2.5D packaging is widely used in applications where integrating large numbers of chips is necessary, such as in graphics processing units (GPUs) and high-performance computing accelerators.

Conclusion

Both 3D IC integration and 2.5D packaging represent significant advancements in semiconductor technology, each with its unique approach to packing more power into less space. As the demand for higher performance and lower power consumption continues to rise, both technologies will likely play pivotal roles in shaping the future of electronic devices. Whether through the vertical stacking of 3D ICs or the side-by-side arrangement of 2.5D packaging, these innovations are driving the semiconductor industry forward, making it possible to achieve levels of performance and efficiency previously unimaginable.

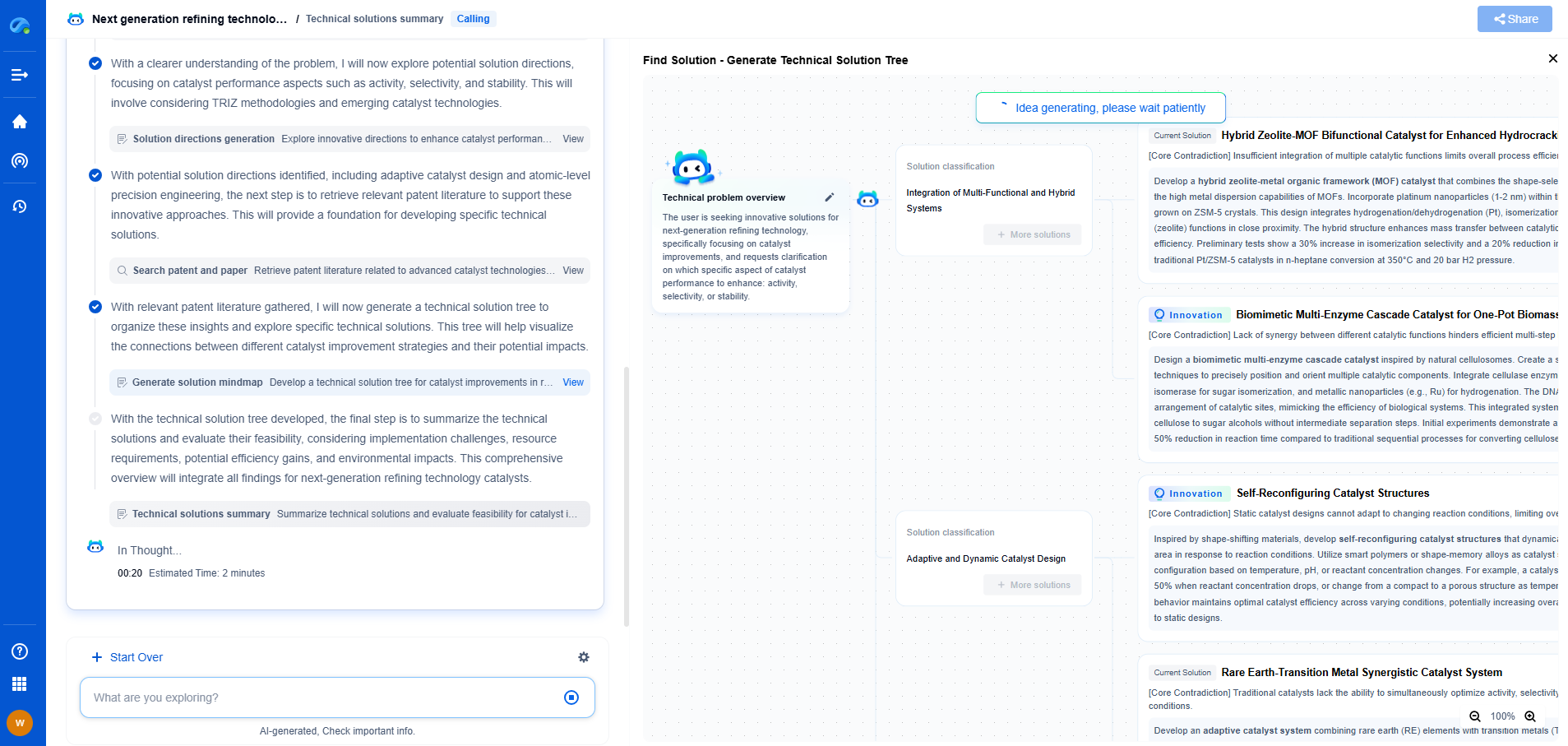

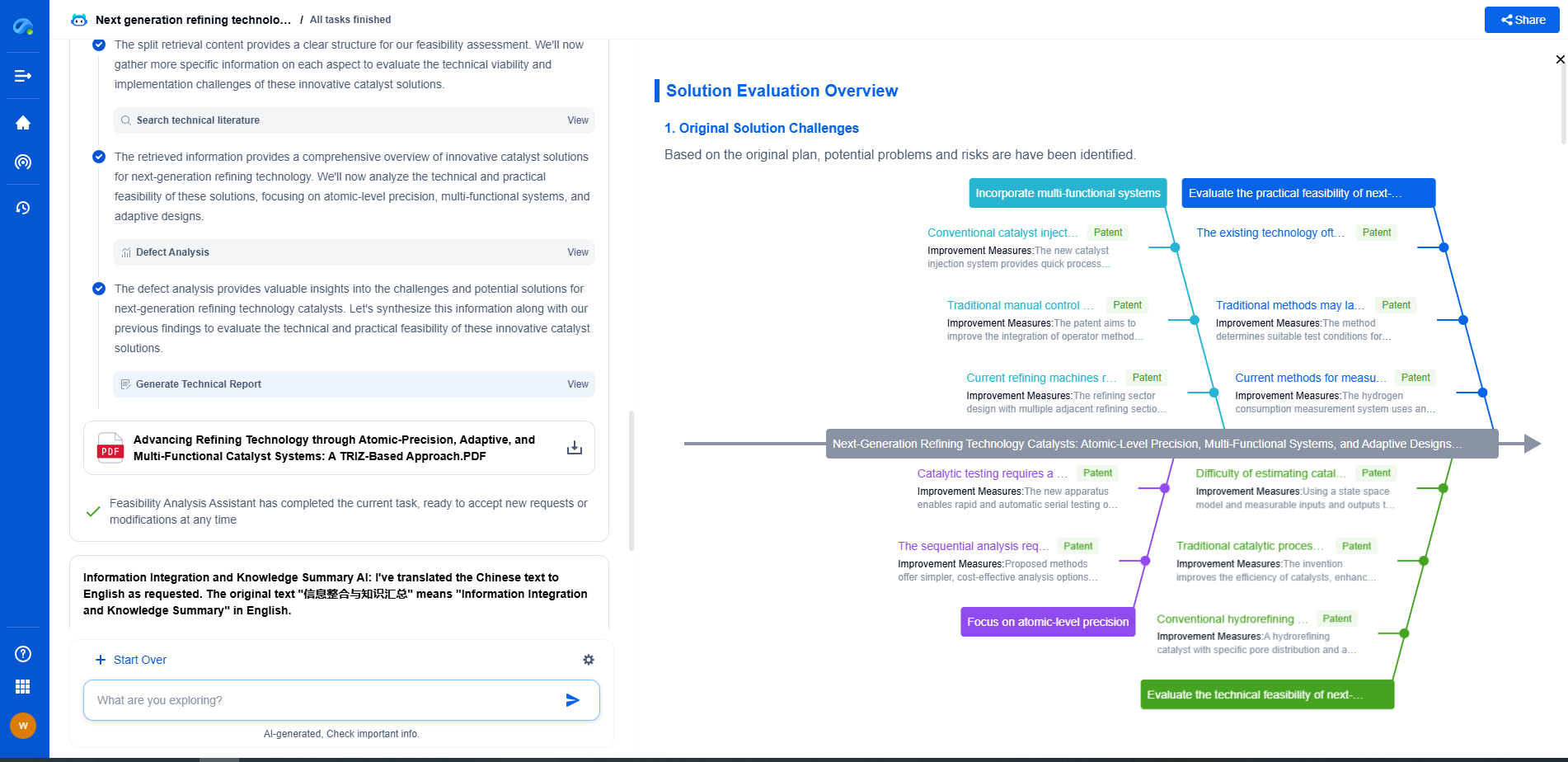

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.