What is line edge roughness (LER) in photolithography and why does it matter?

JUL 28, 2025 |

Photolithography is a pivotal process in semiconductor manufacturing, enabling the creation of intricate patterns on silicon wafers that form the foundation of electronic devices. As the industry moves towards smaller and more advanced nodes, the precision and accuracy of these patterns have become increasingly critical. One of the challenges encountered in photolithography is line edge roughness (LER), a phenomenon that can significantly impact the performance and reliability of semiconductor devices.

Defining Line Edge Roughness

Line edge roughness refers to the variations or deviations seen along the edges of a photoresist pattern after it is developed. Ideally, these edges should be perfectly smooth and straight. However, due to various factors in the photolithography process, these edges often exhibit a degree of roughness, manifesting as small, unintended deviations from the intended path. This roughness is typically measured in nanometers and is a crucial metric in the evaluation of photolithographic quality.

Causes of Line Edge Roughness

Several factors contribute to LER:

1. **Photoresist Material**: The composition and properties of the photoresist material can affect its ability to transfer patterns accurately. Variations in the chemical makeup of the photoresist can lead to non-uniform polymerization, causing rough edges.

2. **Exposure Tool Limitations**: The resolution and precision of the exposure tools, such as photomasks and steppers, play a significant role in pattern accuracy. Limitations in the resolution of these tools can lead to edge roughness.

3. **Post-Exposure Bake and Development**: The conditions under which the photoresist is baked and developed can introduce thermal and chemical noise, contributing to LER. Inconsistent baking temperatures or development times can exacerbate roughness.

4. **Etching Processes**: After development, etching steps remove unwanted material. Variabilities in etching can further increase edge roughness, especially if the etch rate is not consistent across the wafer.

Impact of Line Edge Roughness on Semiconductor Performance

LER is not merely a cosmetic issue; it directly affects the electrical performance of semiconductor devices. Here are some of the implications:

1. **Increased Leakage Currents**: Rough edges can lead to increased leakage currents in transistors. This is because the irregularities create paths for current leakage, reducing the overall efficiency of the device.

2. **Variability in Device Performance**: The presence of LER introduces variability in the critical dimensions of the features, which can result in significant discrepancies in device performance across a wafer or between wafers.

3. **Reduced Reliability**: Over time, the presence of LER can cause wear and defects that reduce the reliability and lifespan of semiconductor devices, especially as nodes continue to shrink.

Strategies to Mitigate Line Edge Roughness

To address the challenges posed by LER, several strategies are employed in the semiconductor industry:

1. **Advanced Photoresists**: Developing photoresists with improved chemical and physical properties can reduce LER. These advanced materials are designed to undergo more uniform polymerization and provide smoother edges.

2. **Optimized Exposure Techniques**: Utilizing exposure tools with higher resolution and precision can minimize LER. Techniques such as extreme ultraviolet (EUV) lithography are being explored to improve edge smoothness.

3. **Controlled Processing Conditions**: Fine-tuning the post-exposure bake and development processes ensures more consistent results, minimizing roughness. This includes precise control over temperature, time, and chemical concentrations.

4. **Refined Etching Technologies**: Implementing more advanced etching techniques with better uniformity and control can help in maintaining smoother line edges.

Conclusion: The Importance of Controlling LER

As the demand for smaller, faster, and more efficient electronic devices grows, controlling LER has become a significant focus in photolithography. Addressing LER not only enhances the performance and reliability of semiconductor devices but also supports the continued advancement of technology. By understanding and mitigating the factors contributing to LER, the semiconductor industry can continue to innovate and meet the ever-increasing demands of modern technology.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

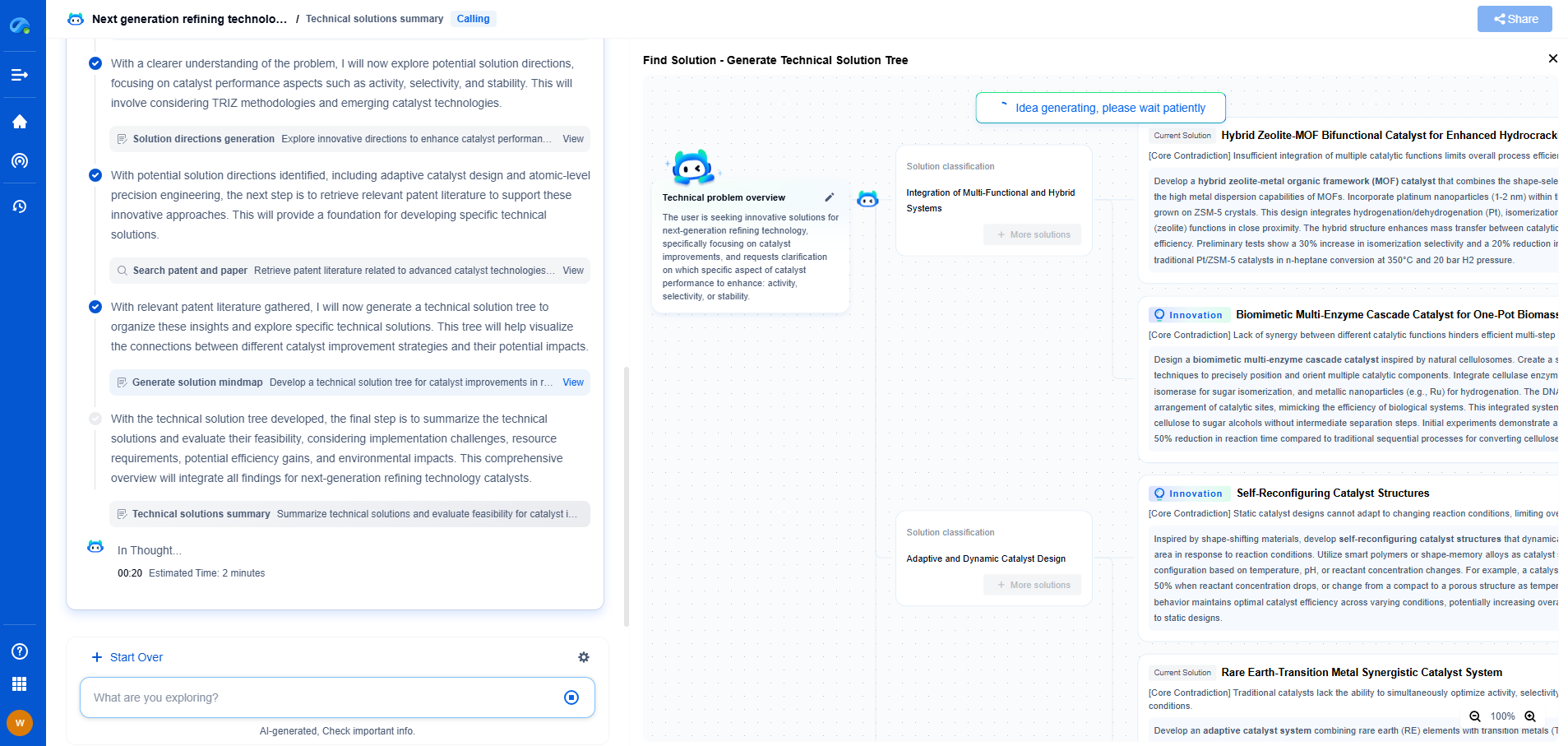

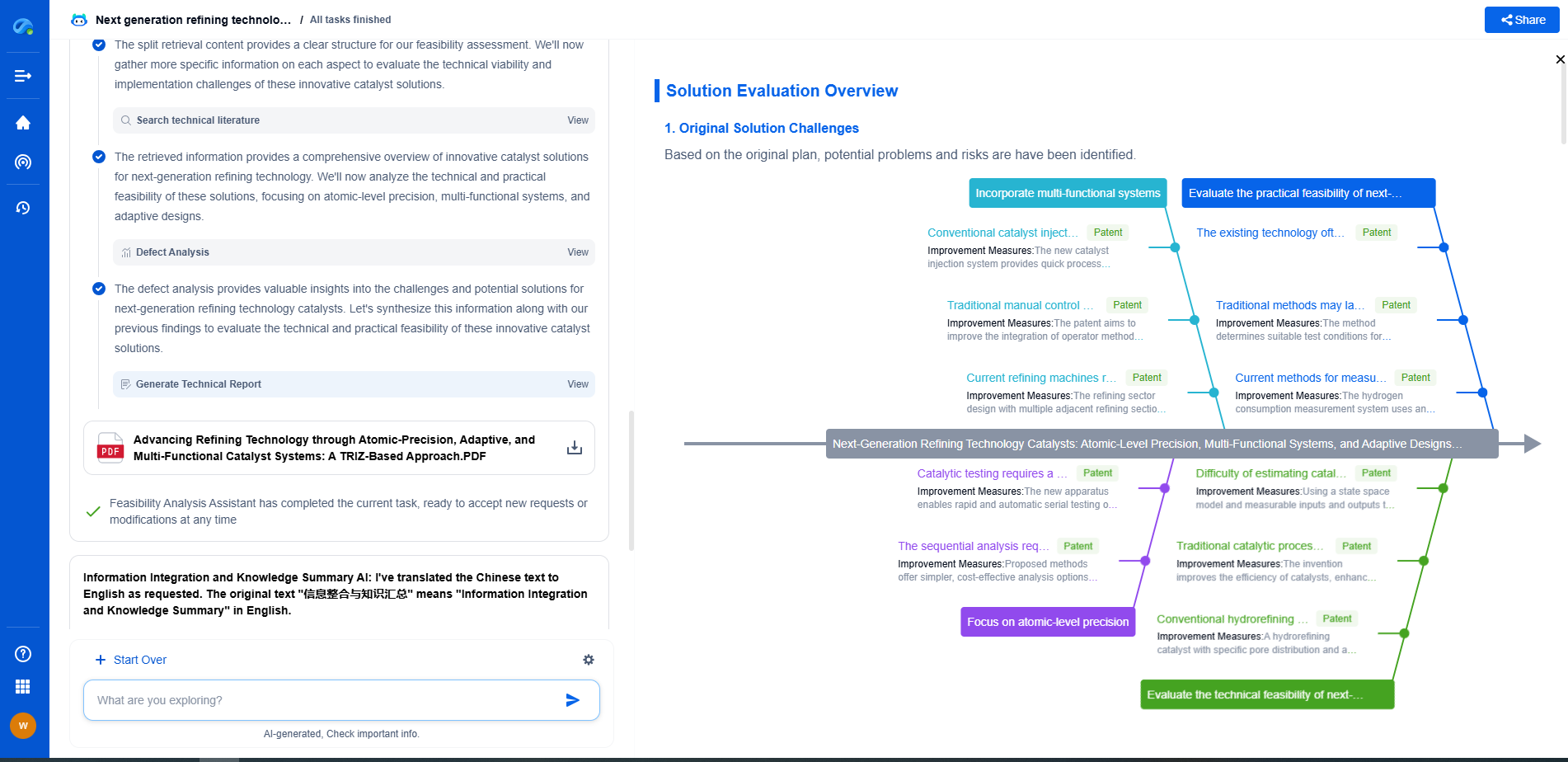

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com