What is OPC (Optical Proximity Correction) modeling in semiconductor manufacturing?

JUL 28, 2025 |

In the intricate world of semiconductor manufacturing, Optical Proximity Correction (OPC) plays a pivotal role. As devices shrink to nanometer scales, the challenges of accurately transferring circuit patterns onto silicon wafers grow exponentially. This is where OPC comes into play, ensuring that the photolithography process can accurately reproduce the intricate patterns required for modern integrated circuits.

Understanding the Basics of Photolithography

To comprehend OPC, it’s essential to first understand the basics of photolithography. Photolithography is the process used to project circuit patterns onto a semiconductor wafer. This involves coating the wafer with a light-sensitive material called photoresist, which is then exposed to ultraviolet light shaped by a photomask. The exposed areas are developed, and the pattern is etched onto the wafer.

The Need for Optical Proximity Correction

As we push the limits of Moore's Law, the wavelengths of light used in photolithography do not easily align with the minuscule dimensions of today’s circuit features. This mismatch leads to distortions, known as optical proximity effects, which can cause significant deviations from the intended pattern. These distortions include line width variations, corner rounding, and pattern displacement, which can critically affect the functionality and performance of semiconductor devices.

The Role of OPC in Semiconductor Manufacturing

OPC is a critical solution to address the aforementioned distortions. It adjusts the photomask design to compensate for these optical proximity effects. By pre-distorting the mask pattern, OPC ensures that the final printed features on the wafer match the desired design as closely as possible.

How OPC Modeling Works

OPC modeling involves sophisticated computational techniques. Engineers use simulations to predict how light will travel through the photolithographic system and interact with the photoresist. These simulations take into account various factors, including the properties of the light source, the photoresist, and the underlying substrate. The OPC software then adjusts the mask design, making minute alterations to ensure that the printed features on the wafer are faithful to the original design.

Types of OPC Techniques

There are two primary types of OPC techniques: rule-based OPC and model-based OPC. Rule-based OPC uses a set of predetermined rules to modify the mask pattern. It is simpler and faster but may not be as precise. Model-based OPC, on the other hand, uses detailed simulations and is more accurate, making it suitable for advanced nodes. It can account for more complex interactions and is essential for fabricating state-of-the-art semiconductor devices.

Challenges and Future Directions

Despite its effectiveness, OPC faces several challenges. As feature sizes continue to shrink, the margin for error becomes even smaller, requiring more sophisticated models and increased computational resources. Additionally, the introduction of new technologies, such as extreme ultraviolet (EUV) lithography, poses fresh challenges and opportunities for OPC development.

The future of OPC is intertwined with advancements in computational power and artificial intelligence. Machine learning techniques are being explored to enhance OPC accuracy and efficiency, potentially leading to breakthroughs in how patterns are corrected and optimized.

Conclusion

In conclusion, Optical Proximity Correction modeling is indispensable in the realm of semiconductor manufacturing. It bridges the gap between the limitations of photolithography and the ever-decreasing feature sizes of modern electronics. As technology advances, OPC will continue to evolve, playing a crucial role in the ongoing pursuit of smaller, faster, and more efficient semiconductor devices.

As photolithography continues to push the boundaries of nanoscale patterning, from EUV and DUV advancements to multi-patterning and maskless lithography, innovation cycles are accelerating—and the IP landscape is becoming more complex than ever.

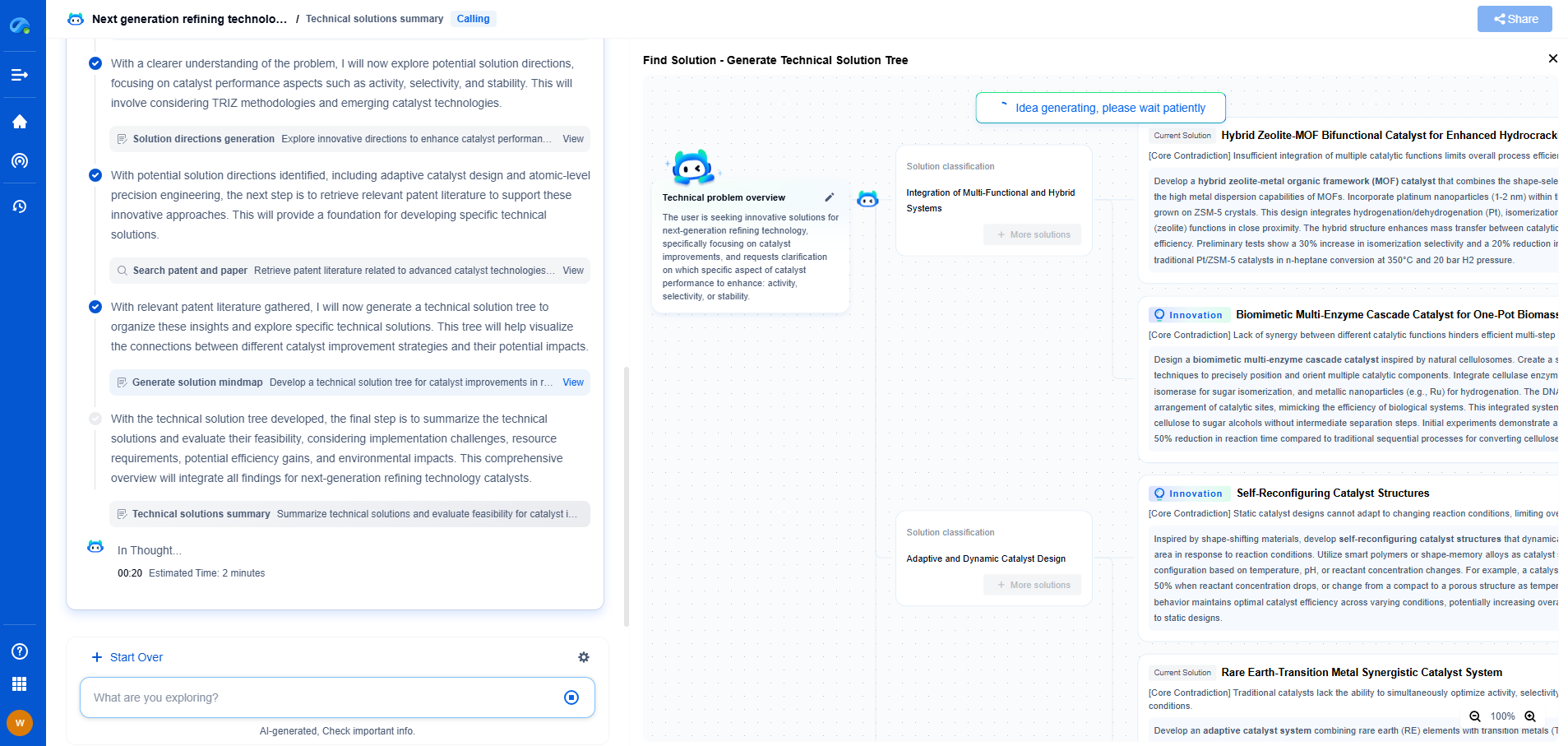

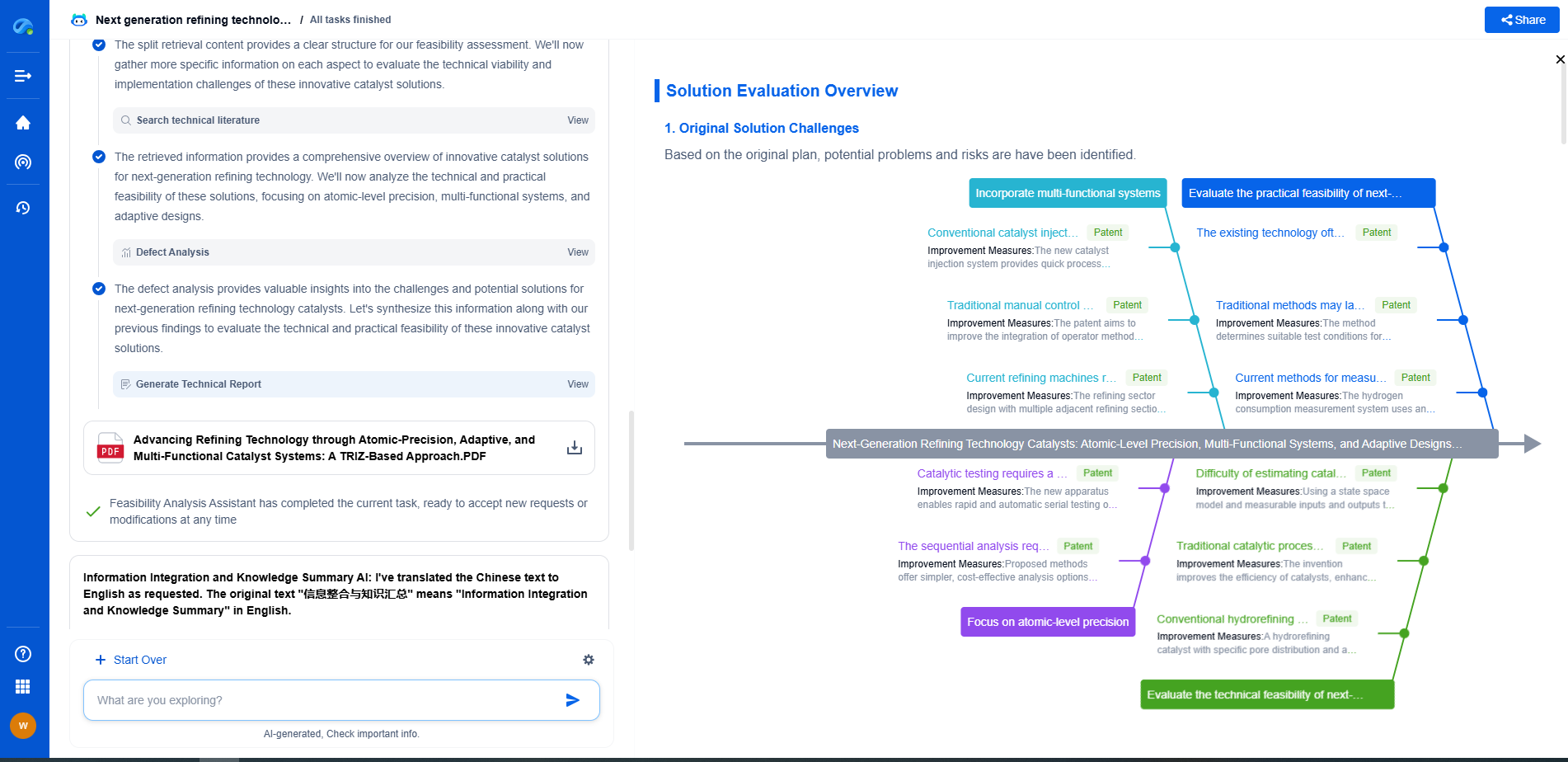

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

Whether you're optimizing lithography depth of focus or exploring new materials for sub-3nm nodes, Patsnap Eureka empowers you to make smarter decisions, faster—combining AI efficiency with domain-specific insight.

💡 Start your free trial today and see how Eureka transforms how you discover, evaluate, and act on innovation in photolithography—from idea to impact.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com