What Is Parasitic Capacitance and How to Reduce It in High-Speed Circuits

JUN 27, 2025 |

Parasitic capacitance is an unintended and often overlooked factor in high-speed electronic circuits. It arises when the conductors in a circuit exhibit capacitive behavior, storing and transferring electric charge between each other. This capacitance is not designed into the circuit; rather, it is an inherent characteristic of the physical layout and materials used. As electronic devices become smaller and faster, the effects of parasitic capacitance become increasingly significant, leading to potential circuit malfunction, decreased performance, and higher power consumption.

Causes of Parasitic Capacitance

Parasitic capacitance is primarily caused by the proximity of conductive elements such as traces, pads, and vias on a printed circuit board (PCB). When these conductive elements are close to each other, an electric field is formed, allowing charge to build up and affecting the signal integrity. Another contributor is the dielectric material between the conductors, which can exacerbate capacitive coupling. Moreover, parasitic capacitance can arise from the internal structure of components themselves or from the leads connecting these components to the circuit.

Impact on High-Speed Circuits

In high-speed circuits, parasitic capacitance can severely impact performance by causing signal distortion and timing errors. It can increase the rise and fall times of signals, leading to slower data rates and potential signal integrity issues. Additionally, it can cause unwanted feedback and crosstalk between circuit elements, further degrading performance. In RF and microwave circuits, parasitic capacitance can detune desired frequencies and introduce losses, affecting the overall efficiency and reliability of the circuit.

Strategies to Reduce Parasitic Capacitance

1. Optimizing PCB Layout

One of the most effective strategies to mitigate parasitic capacitance is to optimize the PCB layout. This involves minimizing the area of conductive traces and ensuring adequate spacing between them. Careful routing of traces and strategic placement of components can significantly reduce capacitive coupling. Using ground planes can also help shield signals and reduce unwanted capacitance.

2. Selecting Appropriate Materials

Choosing the right materials for PCBs is crucial in managing parasitic capacitance. Low dielectric constant materials can reduce the capacitance between traces. Materials with low loss tangents are also beneficial as they minimize energy dissipation and help maintain signal integrity in high-frequency applications.

3. Implementing Guard Traces

Guard traces are additional traces placed parallel to signal traces and connected to a low impedance point such as ground. These traces can help shield the signal traces from each other, reducing capacitive coupling and improving signal integrity. However, the placement and width of guard traces must be carefully considered to be effective.

4. Utilizing Differential Signaling

Differential signaling can help mitigate the effects of parasitic capacitance by using pairs of signals that are equal and opposite. This configuration inherently cancels out noise and reduces the impact of parasitic capacitance on signal performance. It is particularly useful in environments with significant electromagnetic interference.

5. Applying Termination Techniques

Proper termination of signal lines can prevent reflections that exacerbate the effects of parasitic capacitance. Techniques such as series and parallel termination can be employed to match the impedance of the transmission line, ensuring signal integrity and reducing the influence of parasitic elements.

Conclusion

Parasitic capacitance is an inevitable aspect of high-speed circuit design that can have significant adverse effects on performance. Understanding its causes and impacts is crucial for engineers looking to optimize their circuits. Through careful design practices, including PCB optimization, material selection, and effective signal routing, the negative effects of parasitic capacitance can be minimized, leading to more reliable and efficient electronic systems. As technology continues to advance, addressing these challenges will be essential in developing the next generation of high-speed electronic devices.

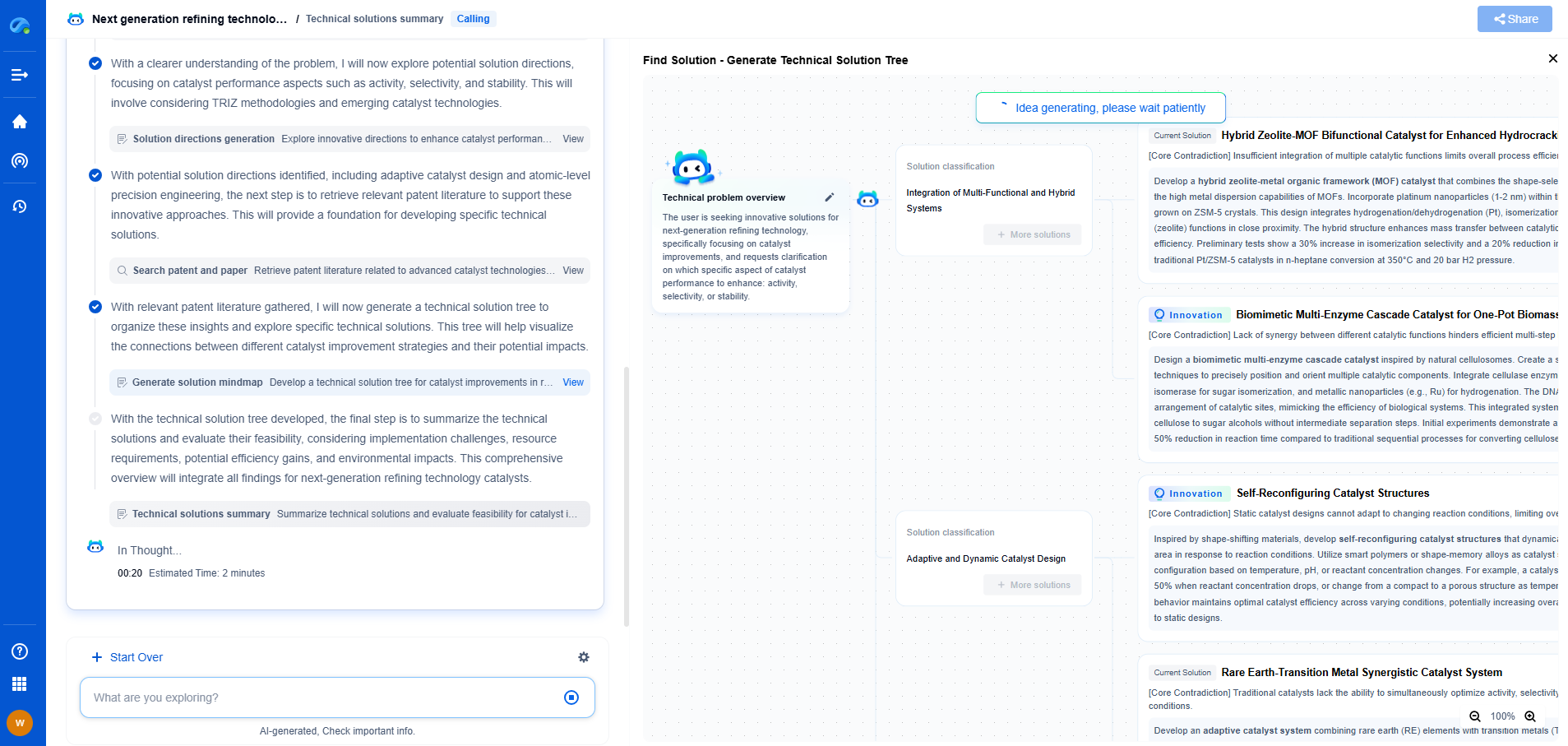

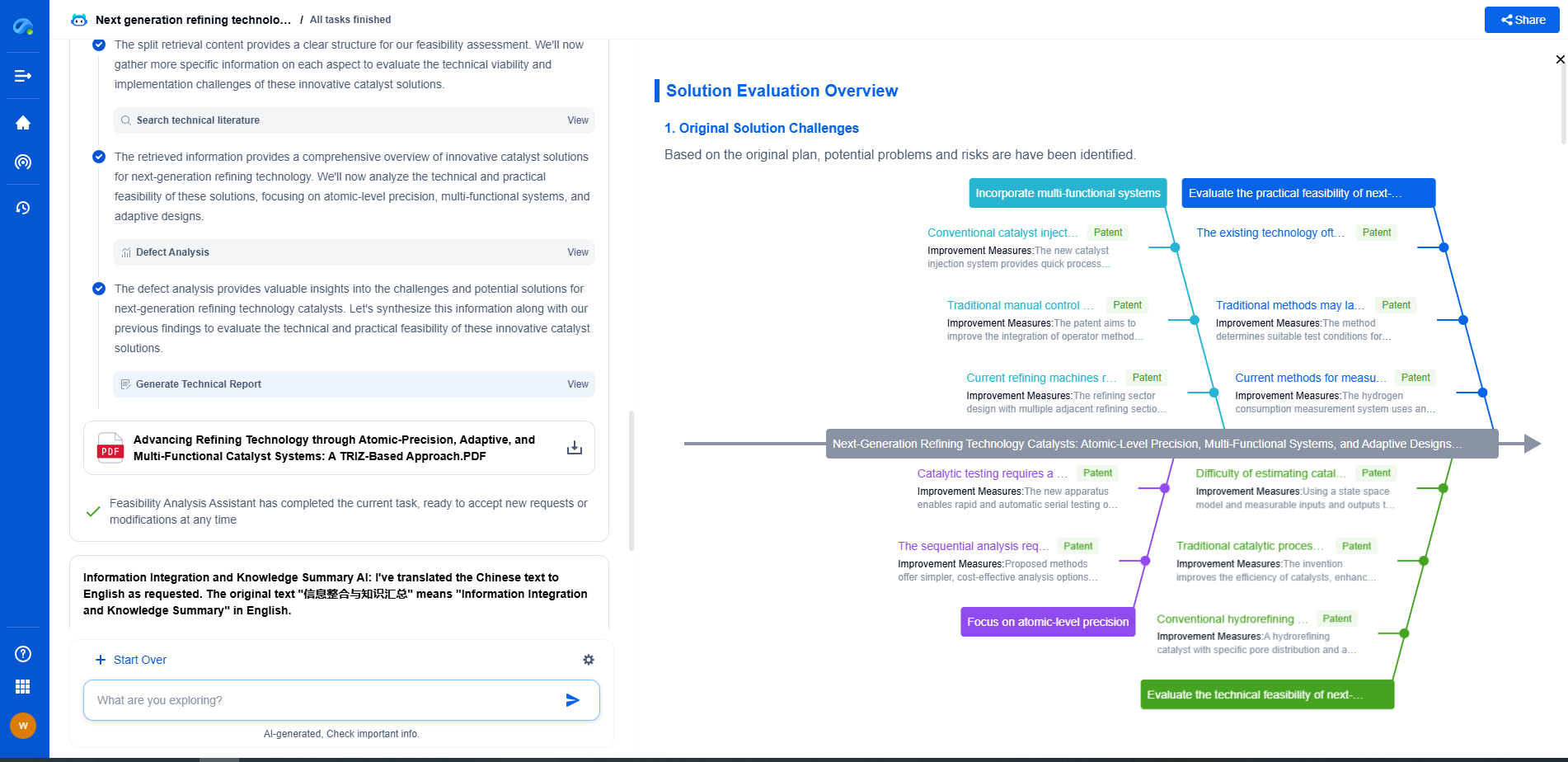

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com