Wafer-Level Packaging (WLP) represents a groundbreaking advancement in the semiconductor industry. As the demand for more compact, powerful, and cost-effective electronic devices continues to rise, WLP has emerged as a key solution that enables the miniaturization of electronic components without compromising performance. This innovative packaging technology involves packaging integrated circuits (ICs) at the wafer level, rather than the traditional method of packaging each die individually after wafer dicing. By doing so, WLP improves efficiency, reduces costs, and enhances the overall performance of electronic products.

The Basics of Wafer-Level Packaging

Wafer-Level Packaging refers to the process of creating an integrated circuit package directly on the wafer before it is diced into individual chips. This method contrasts with traditional packaging techniques, where each chip is packaged separately after being cut from the wafer. By packaging at the wafer level, manufacturers can streamline the process, leading to significant cost savings and improved quality control. Additionally, WLP allows for the integration of more complex structures and features directly onto the chip, such as redistribution layers (RDL) and bumping for electrical connections.

Types of Wafer-Level Packaging

There are several types of wafer-level packaging, each designed to meet specific requirements and applications. Some of the most common types include:

1. Fan-In Wafer-Level Packaging: This type of packaging involves redistributing the input/output connections within the footprint of the die. It is most suitable for applications with a limited number of I/O connections and smaller chip sizes.

2. Fan-Out Wafer-Level Packaging: Unlike Fan-In WLP, Fan-Out packaging redistributes the I/O connections beyond the boundaries of the die, allowing for more connections and better thermal performance. This method is ideal for applications that require a higher number of I/O connections and enhanced thermal management.

3. Wafer-Level Chip-Scale Packaging (WLCSP): WLCSP is a type of Fan-In WLP that results in a chip-scale package, which is nearly the same size as the die itself. This packaging is widely used in mobile devices due to its compact size and cost-effectiveness.

Advantages of Wafer-Level Packaging

WLP offers several advantages over traditional packaging methods, making it a preferred choice for many modern electronic applications. Some of the key benefits include:

1. Miniaturization: WLP enables the production of smaller and thinner packages, which are essential for modern portable and wearable devices.

2. Cost Efficiency: By packaging the entire wafer in a single process, manufacturers can reduce production costs significantly, as there is less material waste and fewer processing steps.

3. Enhanced Performance: WLP provides better electrical performance due to shorter interconnects and improved thermal characteristics, which is crucial for high-performance applications.

4. Improved Reliability: The packaging technique eliminates the need for wire bonding, reducing failure points and enhancing the overall reliability of the device.

Challenges and Considerations

Despite its advantages, WLP also presents some challenges that manufacturers must address. One of the primary challenges is the complexity of the process, which requires advanced equipment and precise control. Additionally, the thermal management of WLP can be more challenging due to the compact size of the packages, necessitating innovative thermal solutions. Furthermore, as the number of I/O connections increases, ensuring mechanical reliability becomes critical, necessitating rigorous testing and quality assurance procedures.

Applications of Wafer-Level Packaging

The versatility of WLP makes it suitable for a wide range of applications across various industries. Some notable applications include:

1. Mobile Devices: WLP is extensively used in smartphones, tablets, and wearables, where compact size, cost-effectiveness, and high performance are critical.

2. Automotive Electronics: In the automotive industry, WLP is utilized for advanced driver-assistance systems (ADAS), infotainment systems, and other electronic components that require reliability and performance.

3. Internet of Things (IoT): As IoT devices continue to proliferate, WLP provides the necessary miniaturization and performance needed for sensors, smart home devices, and industrial IoT applications.

Conclusion

Wafer-Level Packaging is a transformative technology that addresses the growing demand for smaller, more efficient, and higher-performing electronic components. By packaging at the wafer level, manufacturers can achieve significant cost savings, enhanced performance, and greater reliability. As the semiconductor industry continues to evolve, WLP is poised to play a crucial role in enabling the next generation of electronic devices, making it an indispensable tool for innovation and advancement.

What Is Wafer-Level Packaging (WLP) and How Does It Work?

JUN 27, 2025 |

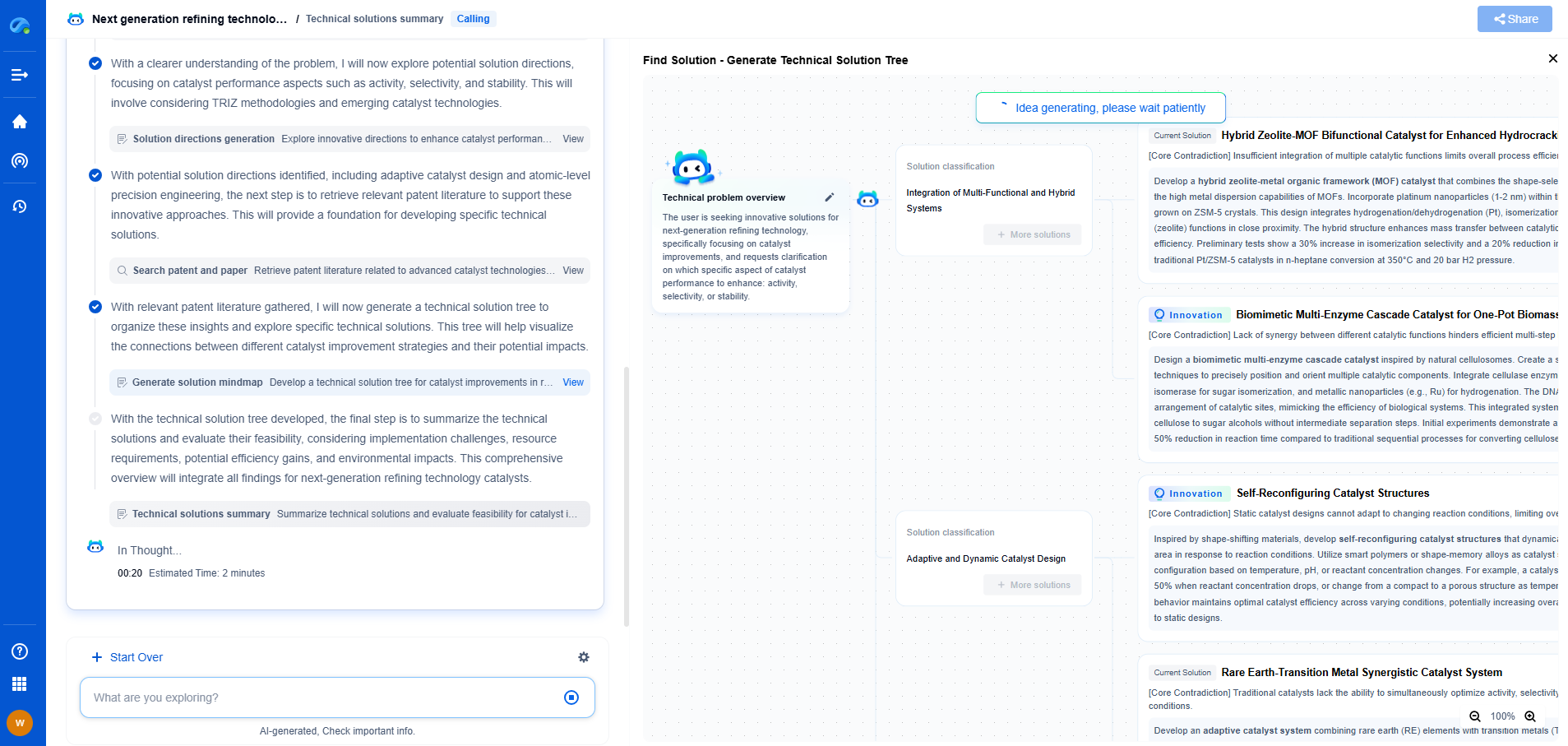

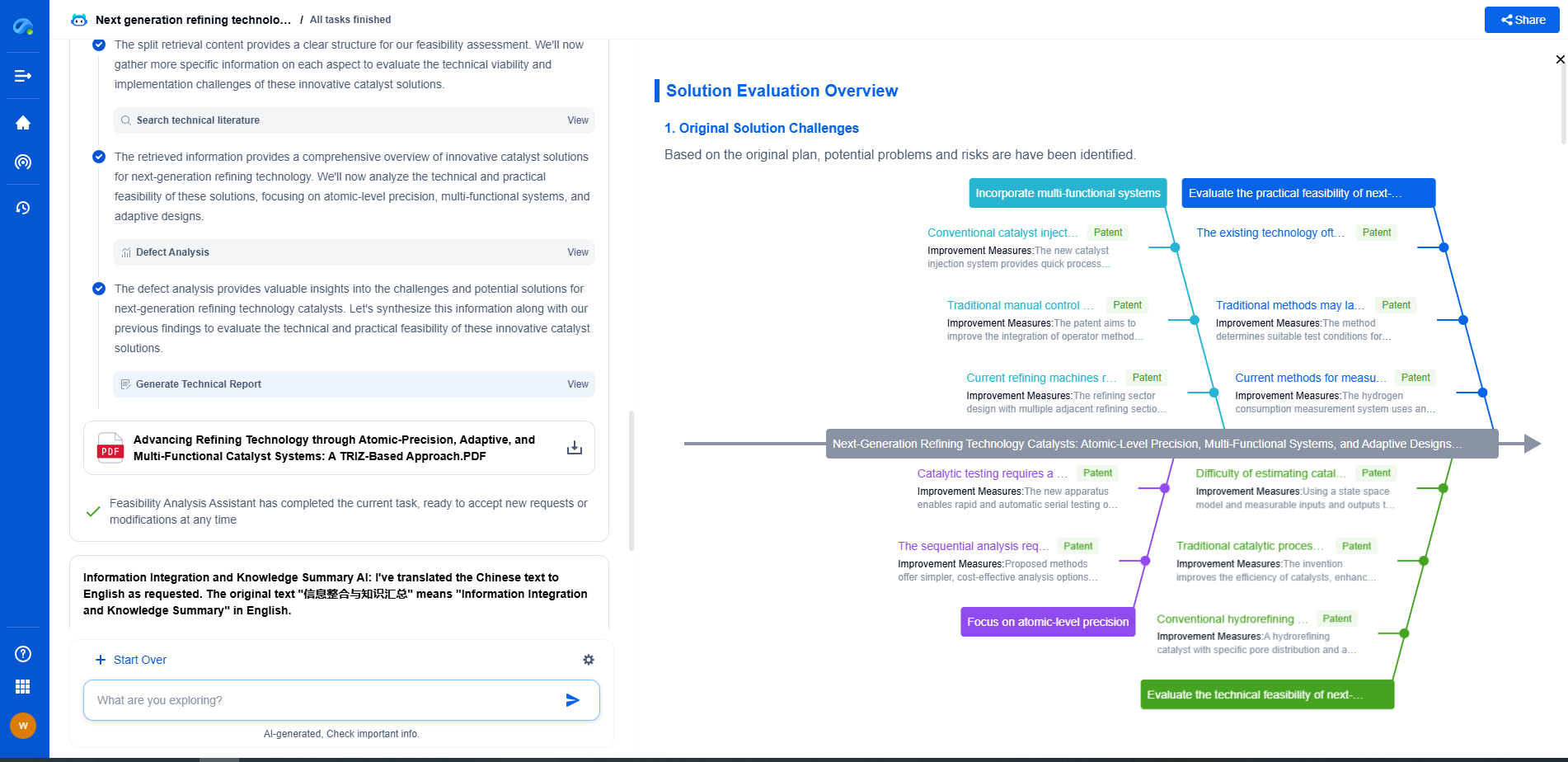

Empower Your Breakthroughs in Basic Electric Components with Patsnap Eureka

From resistors, capacitors, and inductors to fuses, connectors, superconductors, and nano-scale materials—basic electric elements may be the building blocks of modern electronics, but the innovation behind them is anything but simple. As device miniaturization accelerates and materials science pushes new frontiers, R&D and IP teams face increasing complexity in staying on top of technical advancements, patent activity, and competitive landscapes.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

🔧 Whether you’re optimizing energy storage, improving thermal resistance, or creating the next leap in circuit efficiency, Patsnap Eureka is your AI copilot for high-efficiency, high-precision R&D and IP strategy.

👉 Experience how Patsnap Eureka can revolutionize your R&D and IP strategy. Request a demo today and power up your next breakthrough.