What to Do When Your Watchdog Timer Causes Unintended Resets

JUL 2, 2025 |

A watchdog timer is a crucial component in embedded systems, designed to monitor and ensure that the system is functioning correctly. It serves as a safety net, resetting the processor if it becomes unresponsive or stuck in an infinite loop. However, unintended resets triggered by the watchdog can be frustrating and may indicate underlying issues that need to be addressed. Let's explore how to handle these unexpected resets effectively.

Identifying the Cause of Resets

The first step in addressing unintended watchdog timer resets is to identify the root cause. Start by checking the system logs, as they may provide insights into what the processor was doing before the reset occurred. Look for patterns or specific operations that consistently precede the reset. Common causes include software bugs, resource conflicts, or incorrect timer settings.

Analyzing and Debugging the Code

Once you have some clues about the potential cause, dive into analyzing and debugging your code. Ensure that the code adheres to best practices and does not contain infinite loops or deadlocks. Use debugging tools and methods such as breakpoints and step-through debugging to pinpoint where the problem lies. Pay special attention to areas where the system might become unresponsive, such as during complex computations or while waiting for input/output operations to complete.

Evaluating Timer Settings

The configuration of the watchdog timer itself can also be a source of unintended resets. Review the timer settings to ensure they are appropriate for your system's needs. The timeout period must be long enough to accommodate the longest expected operation, yet short enough to detect genuine failures. Adjust the timeout as necessary, balancing the need for responsiveness with the risk of false resets. Additionally, ensure that the timer is being reset (or "kicked") at appropriate intervals in the program flow.

Improving Resource Management

Poor resource management can lead to situations where the system becomes unresponsive, triggering the watchdog timer. Check for resource leaks or contention issues, such as memory leaks or improper handling of file descriptors and network connections. Implement robust error handling and recovery mechanisms to ensure that the system can gracefully manage and recover from unexpected conditions.

Implementing Robust System Design

A robust system design is essential for preventing unintended watchdog timer resets. Consider implementing redundancy and fail-safe mechanisms that allow the system to continue operating or recover gracefully in the event of failures. Design your software architecture to be modular, enabling easier isolation and resolution of issues. Implement regular system monitoring and diagnostics to detect and address potential problems before they cause a reset.

Testing and Validation

Thorough testing and validation are crucial steps in ensuring the stability of your system. Conduct comprehensive testing under various conditions, including load testing and stress testing, to assess how the system behaves under different scenarios. Simulate failure conditions to verify that the system can recover without triggering unintended resets. Validate that the watchdog timer settings and code changes effectively prevent false resets.

Continuous Monitoring and Maintenance

Even after addressing the immediate issues causing unintended resets, continuous monitoring and maintenance are vital. Implement logging and monitoring tools that can alert you to unusual behaviors or potential problems in real-time. Regularly review and update your system to incorporate the latest best practices and security patches. Stay informed about updates to the hardware and software components of your system that might affect the watchdog timer's behavior.

Conclusion

Dealing with unintended watchdog timer resets involves a systematic approach to identifying and resolving underlying issues. By understanding the causes of resets, debugging the code, evaluating timer settings, improving resource management, and implementing robust system design, you can minimize the occurrence of these resets. Testing, validation, and continuous monitoring further ensure the stability and reliability of your system. With careful attention to these areas, you can effectively manage watchdog timer resets and maintain a smoothly operating embedded system.

Ready to Reinvent How You Work on Control Systems?

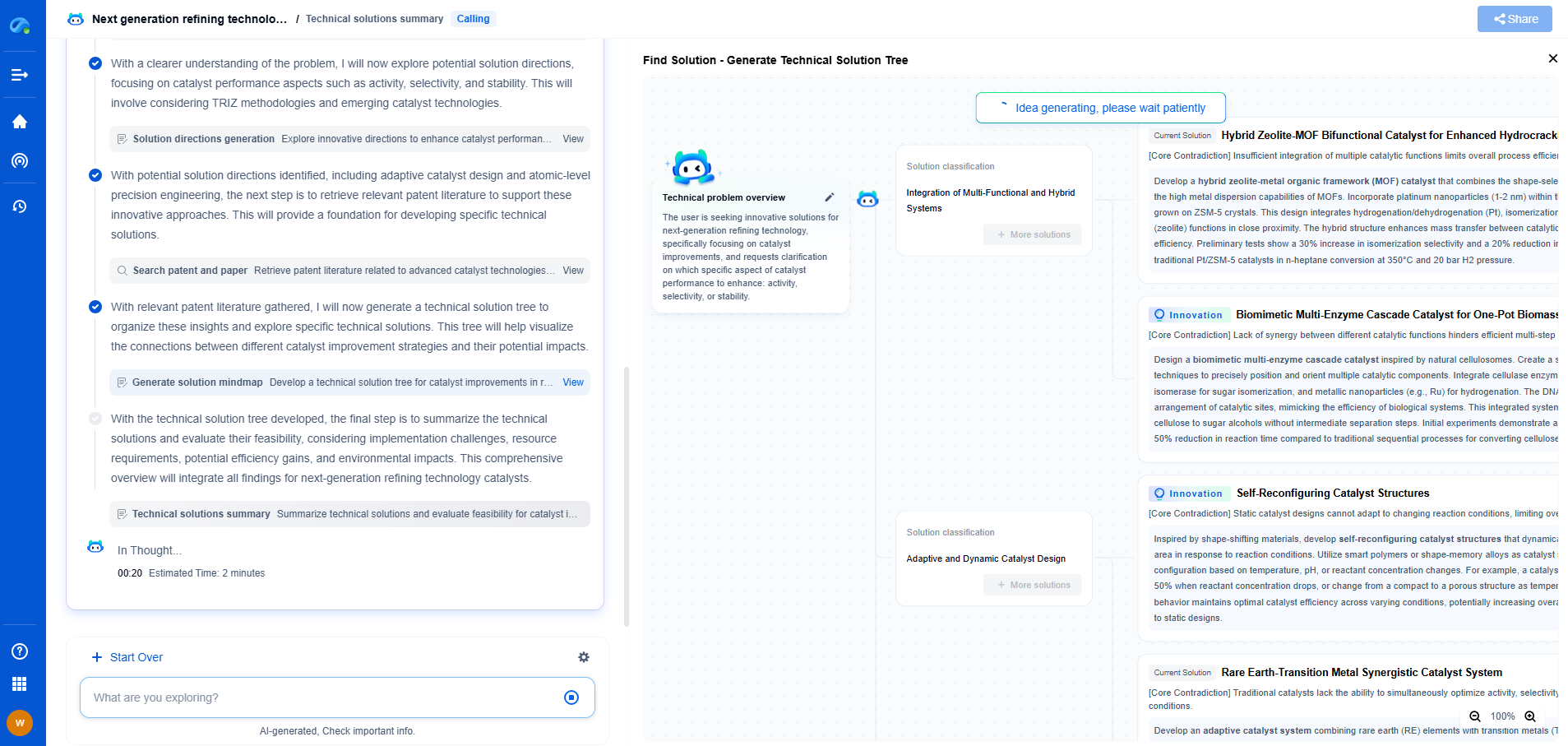

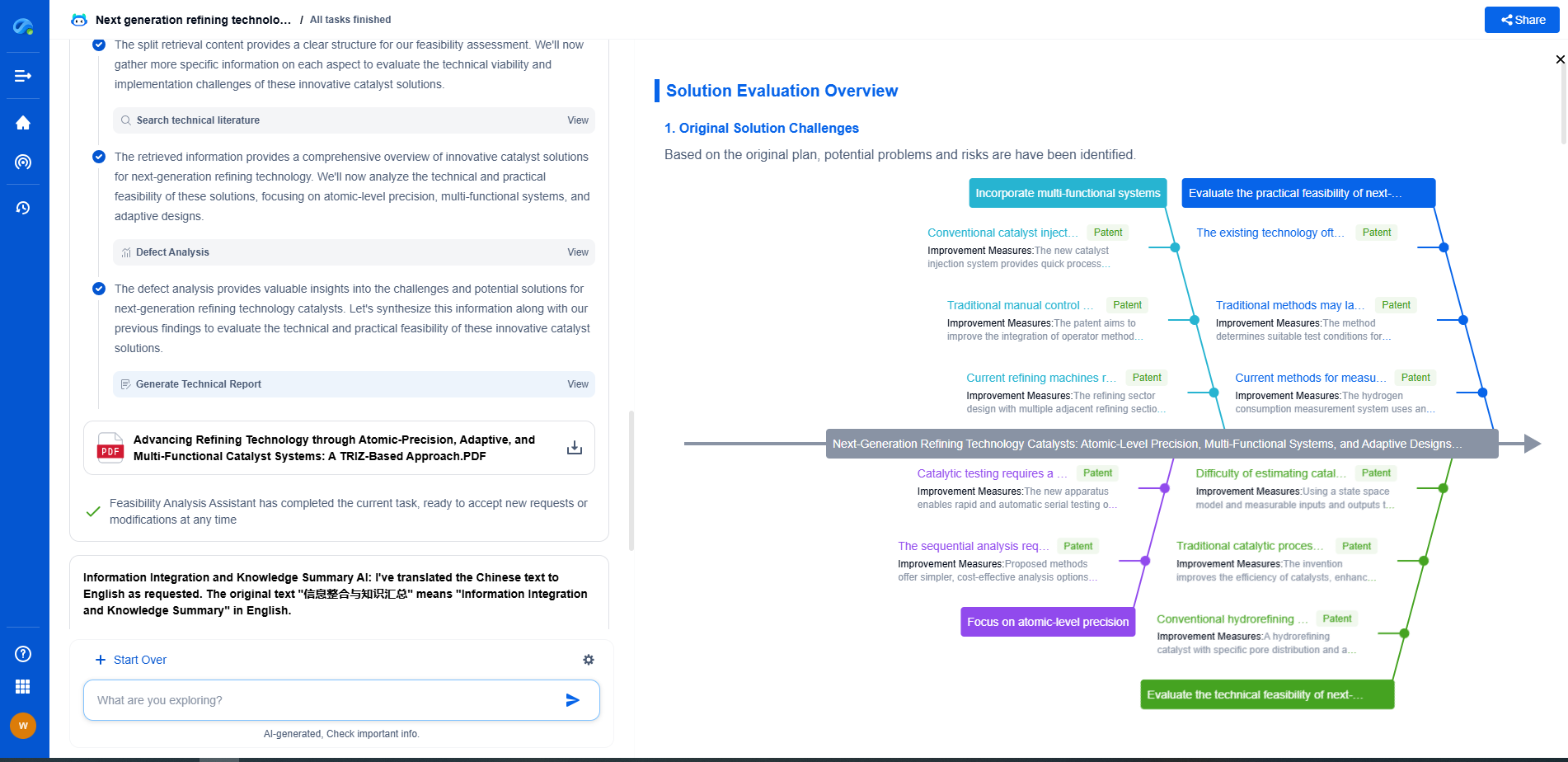

Designing, analyzing, and optimizing control systems involves complex decision-making, from selecting the right sensor configurations to ensuring robust fault tolerance and interoperability. If you’re spending countless hours digging through documentation, standards, patents, or simulation results — it's time for a smarter way to work.

Patsnap Eureka is your intelligent AI Agent, purpose-built for R&D and IP professionals in high-tech industries. Whether you're developing next-gen motion controllers, debugging signal integrity issues, or navigating complex regulatory and patent landscapes in industrial automation, Eureka helps you cut through technical noise and surface the insights that matter—faster.

👉 Experience Patsnap Eureka today — Power up your Control Systems innovation with AI intelligence built for engineers and IP minds.

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com