From smartphones to automobiles, from home appliances to aerospace, and even into extreme environments such as outer space vacuum, aircraft engines, industrial automation, and electrified drive systems, chips are everywhere. In these harsh scenarios, chips must not only withstand challenges such as extreme temperature fluctuations, corrosive gases, mechanical vibrations, radiation, and irregular power cycles, but also deliver increasingly complex functionalities.

Why are these chips able to operate stably under such extreme conditions? How can they guarantee consistent, decade-long reliability? The answer lies in process reliability. Indeed, process reliability is the cornerstone of chip performance and the foundation for long-term stability. As reliability requirements continue to escalate, semiconductor testing and metrology technologies are rapidly evolving to ensure continuous breakthroughs beyond performance limits.

The Dual Challenges of Chip Reliability

In the field of chip reliability, two forces converge to form a dual challenge: external environmental stress and internal architectural complexity. Harsh environments impose rigorous demands on chip reliability, primarily through extreme temperatures, radiation effects, mechanical stress, and chemical corrosion. In the era of heterogeneous integration (Chiplet/3D IC), these issues become further compounded, requiring entirely new solutions.

1. Extreme Temperature Effects

·Performance degradation mechanisms: High temperatures increase reverse leakage current, cause transistor operating point drift, shrink dynamic range, and lower maximum allowable power dissipation; low temperatures lead to material embrittlement and thermal stress mismatch.

·Material failure cases: Coefficient of Thermal Expansion (CTE) mismatch can induce delamination of packaging layers and solder joint cracking, necessitating rapid thermal cycling tests (-65℃ to 150℃) to validate interfacial reliability.

·Aerospace-grade requirements: Operating temperature must cover -184℃ to +149℃, far exceeding the 0℃ to +70℃ range of commercial chips.

2. Radiation Effects

·Single-Event Effects (SEE): Space radiation induces Single-Event Upsets (SEU), Latchup (SEL), and Total Dose Ionization (TDI). Among 39 recorded satellite failures, 71% were radiation-related.

·Hardening technologies: At the process level, Silicon-On-Insulator (SOI) is used to suppress parasitic transistor activation. At the design level, Triple Modular Redundancy (TMR) and Error Detection and Correction (EDAC) mechanisms are implemented.

3. Mechanical Stress and Chemical Corrosion

·Vibration/shock failures: MEMS devices are prone to cantilever beam fracture and wire bond detachment under shock. Military-grade chips must endure ejection acceleration and salt spray corrosion.

·Humidity-induced degradation: 85℃/85%RH environments lead to decreased molding compound impedance, resulting in leakage currents.

4. Heterogeneous Packaging

·Chip-level (Chiplet) testing: Each die must independently verify Known Good Die (KGD) status, as process variations introduce diverse failure modes.

·System-level (2.5D/3D) testing: Thermal coupling in silicon interposers may induce timing shifts, requiring cross-die boundary scan chains (IEEE 1838 standard).

Evolving Test Strategies:

To tackle these challenges, test strategies are undergoing continuous evolution.

·Shift Left emphasizes moving testing earlier into the design phase, such as intercepting defects through unit testing.

·Shift Right simulates real-world conditions in production environments (e.g., fault injection, deployment ring tests) to validate chip behavior under extreme workloads.

In reliability testing, the integration of both approaches is critical:

·Front-end (Shift Left): Wafer-level testing incorporates three-temperature CP tests (-40℃ / 25℃ / 125℃) to identify thermally sensitive defects, while radiation-hardened designs embed TMR structures.

·Back-end (Shift Right): Automotive-grade chips undergo SLT testing to simulate engine compartment vibration spectra, while aerospace chips require in-orbit verification of radiation resistance.

Collaborative Optimization of System-Level Test (SLT) and Burn-In

Traditional approaches to System-Level Test (SLT) and Burn-In each have strengths and limitations.

Burn-In

·Advantage: Accelerates early-life failures (infant mortality phase of the bathtub curve)

·Limitation: Only triggers defects related to electrical stress

SLT

·Advantage: Simulates real functional failures

·Limitation: Longer test duration (minutes vs. seconds)

Through an innovative parallel execution architecture—integrating SLT controllers into Burn-In ovens—temperature/voltage stress and functional testing can be applied simultaneously. For example, after adopting this combined approach for automotive SoCs, STMicroelectronics achieved a 40% improvement in screening efficiency and a 28% cost reduction.

Advanced Reliability Verification Technologies

1.Predictive Analytics Framework

·Data foundation: Field failure data collected via FRACAS, with lifetime distribution modeled using Weibull analysis.

·AI enablement: LSTM networks analyze sensor time-series data to predict metal migration failures; reinforcement learning optimizes accelerated stress test profiles (e.g., temperature ramp rates in PCT chambers).

2.Innovations in Accelerated Aging Tests

·PCT chamber: 130 °C / 85% RH / 2.3 atm pressure-cooking for 72 hours equates to 5 years of natural aging.

·Dynamic thermal cycling: Rapid temperature variation at 25 °C/min exposes solder joint fatigue and cracks (critical for automotive electronics validation).

Industry-Specific Reliability Requirements

1.Aerospace & Defense

·Space-grade certification: 1000 Gy radiation exposure + 1000 hours of HTOL aging.

·Radiation-hardened design: GaAs-based devices replacing conventional silicon.

2.Automotive Electronics

·Three-temperature SLT: -40 °C to 150 °C cycles while running ADAS algorithms.

·Redundancy: Dual-channel verification mechanisms in braking systems.

3.Industrial Automation

·Corrosion protection: Ceramic packaging to resist sulfur-rich gas environments.

·Vibration isolation: Damping structures in MEMS accelerometers to enhance durability.

Evolution Path of Reliability Technologies

·Design dimension: Transition from standard processes to SOI/HARDSIL radiation-hardened technologies.

·Test dimension: SLT + Burn-In combinations replacing standalone screening, covering full lifecycle failure modes.

·Predictive dimension: Digital twin–based failure simulation to reduce physical verification costs.

·Standards dimension: Development of heterogeneous multi-die test protocols (e.g., IEEE 1838).

Through these synergistic advances, chip failure rates in extreme environments such as jet engines (>200 °C) and deep-earth drilling (>150 MPa) can be reduced from parts-per-thousand to parts-per-million levels, driving a reliability revolution for semiconductors in frontier applications.

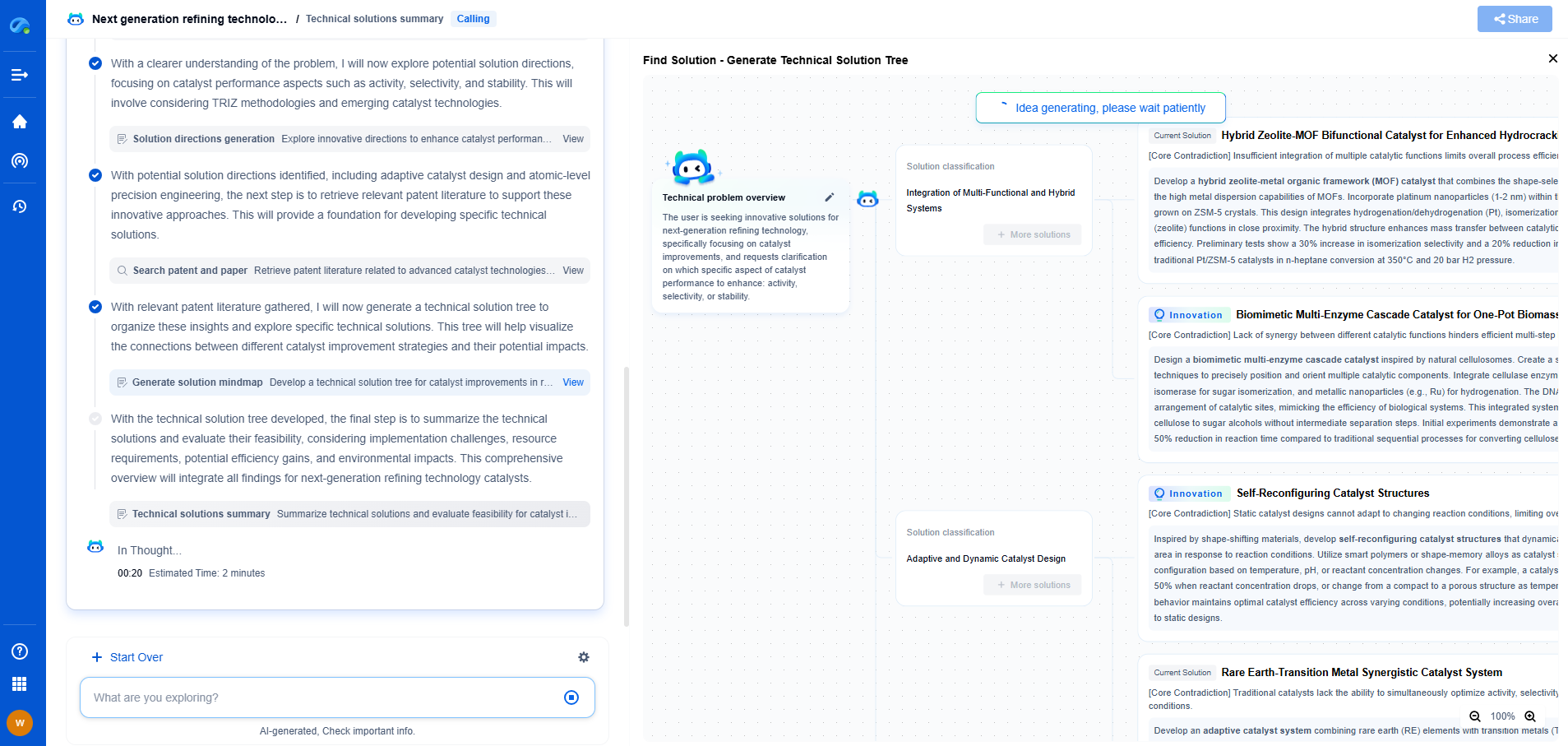

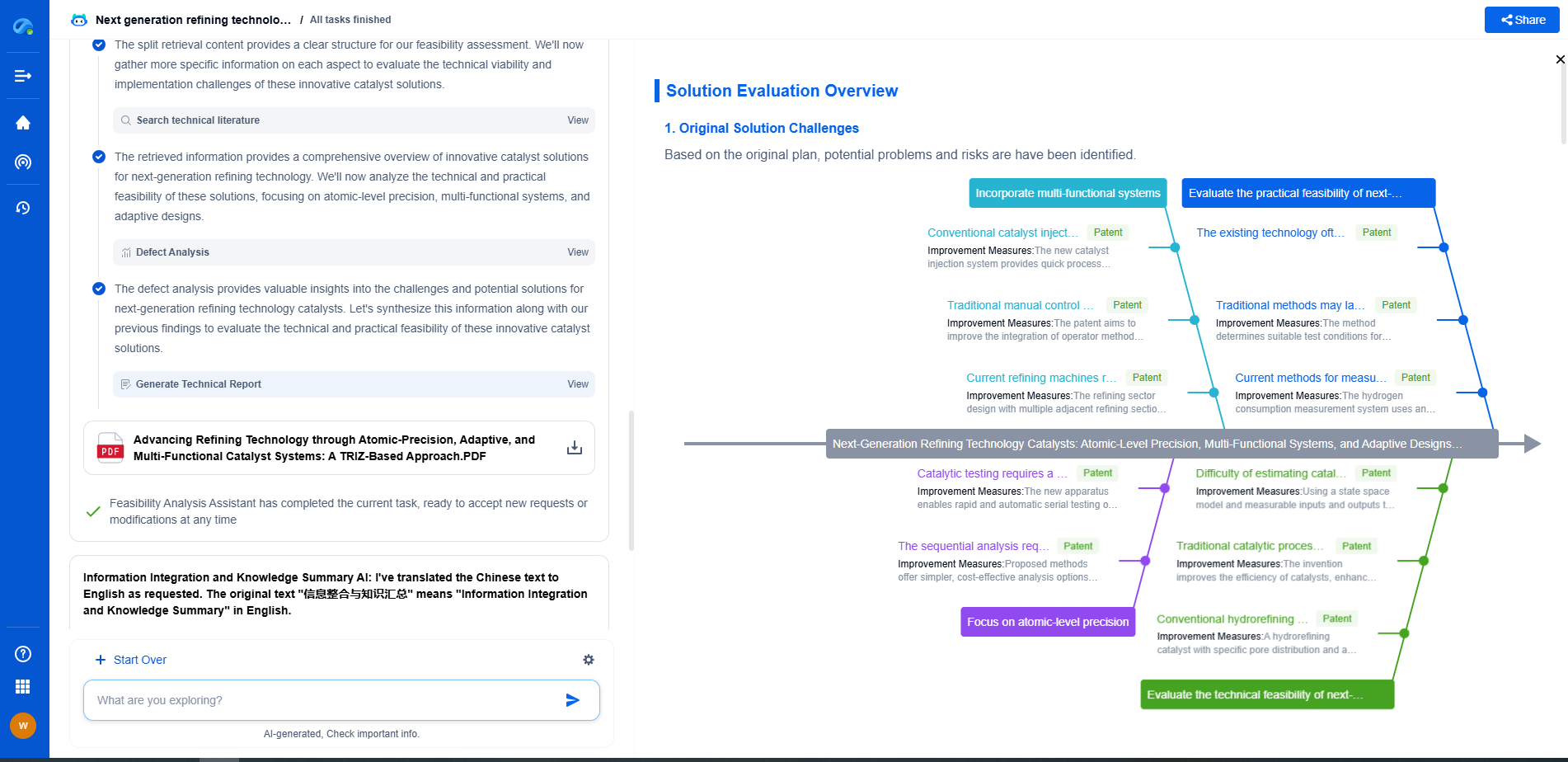

Infuse Insights into Chip R&D with PatSnap Eureka

Whether you're exploring novel transistor architectures, monitoring global IP filings in advanced packaging, or optimizing your semiconductor innovation roadmap—Patsnap Eureka empowers you with AI-driven insights tailored to the pace and complexity of modern chip development.

Patsnap Eureka, our intelligent AI assistant built for R&D professionals in high-tech sectors, empowers you with real-time expert-level analysis, technology roadmap exploration, and strategic mapping of core patents—all within a seamless, user-friendly interface.

👉 Join the new era of semiconductor R&D. Try Patsnap Eureka today and experience the future of innovation intelligence.