Characterizing TSV Performance in Signal Dense Environments

APR 15, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

TSV Signal Integrity Background and Performance Goals

Through-Silicon Vias (TSVs) have emerged as a critical enabling technology for three-dimensional integrated circuits, fundamentally transforming the landscape of semiconductor packaging and system integration. The evolution of TSV technology traces back to the early 2000s when the semiconductor industry began exploring vertical interconnect solutions to overcome the limitations of traditional wire bonding and flip-chip technologies. Initially developed for memory stacking applications, TSVs have progressively expanded into high-performance computing, mobile processors, and advanced packaging solutions.

The technological progression of TSVs has been driven by the relentless pursuit of higher bandwidth, reduced form factors, and improved electrical performance. Early implementations focused primarily on basic connectivity, but modern TSV applications demand sophisticated signal integrity management in increasingly complex electromagnetic environments. The transition from simple power and ground connections to high-speed signal transmission has introduced unprecedented challenges in maintaining signal quality and minimizing interference.

Contemporary TSV implementations face mounting pressure to support multi-gigabit data rates while operating in signal-dense environments where electromagnetic coupling and crosstalk become dominant performance limiters. The miniaturization trends in semiconductor packaging have resulted in TSV pitches shrinking below 50 micrometers, creating scenarios where traditional signal integrity design rules become inadequate. This evolution has necessitated a fundamental shift from empirical design approaches to physics-based modeling and characterization methodologies.

The primary performance objectives for TSVs in signal-dense environments center on maintaining signal integrity across multiple frequency domains while minimizing power consumption and electromagnetic interference. Key targets include achieving insertion loss below 0.5 dB per TSV at frequencies up to 20 GHz, maintaining return loss better than -15 dB across the operational bandwidth, and limiting near-end and far-end crosstalk to levels below -40 dB. Additionally, TSV designs must demonstrate robust performance under varying temperature conditions and manufacturing tolerances.

Power delivery integrity represents another critical performance dimension, requiring TSVs to maintain stable voltage levels with minimal noise coupling between power and signal domains. The target specifications typically demand power delivery network impedance below 1 milliohm at frequencies up to 1 GHz, while simultaneously ensuring that switching noise does not degrade signal quality beyond acceptable thresholds.

Thermal management objectives have become increasingly important as TSV density increases, with performance goals focusing on maintaining junction temperatures below critical thresholds while ensuring uniform heat distribution across the three-dimensional structure. These thermal considerations directly impact electrical performance, creating interdependent optimization challenges that require holistic design approaches.

The technological progression of TSVs has been driven by the relentless pursuit of higher bandwidth, reduced form factors, and improved electrical performance. Early implementations focused primarily on basic connectivity, but modern TSV applications demand sophisticated signal integrity management in increasingly complex electromagnetic environments. The transition from simple power and ground connections to high-speed signal transmission has introduced unprecedented challenges in maintaining signal quality and minimizing interference.

Contemporary TSV implementations face mounting pressure to support multi-gigabit data rates while operating in signal-dense environments where electromagnetic coupling and crosstalk become dominant performance limiters. The miniaturization trends in semiconductor packaging have resulted in TSV pitches shrinking below 50 micrometers, creating scenarios where traditional signal integrity design rules become inadequate. This evolution has necessitated a fundamental shift from empirical design approaches to physics-based modeling and characterization methodologies.

The primary performance objectives for TSVs in signal-dense environments center on maintaining signal integrity across multiple frequency domains while minimizing power consumption and electromagnetic interference. Key targets include achieving insertion loss below 0.5 dB per TSV at frequencies up to 20 GHz, maintaining return loss better than -15 dB across the operational bandwidth, and limiting near-end and far-end crosstalk to levels below -40 dB. Additionally, TSV designs must demonstrate robust performance under varying temperature conditions and manufacturing tolerances.

Power delivery integrity represents another critical performance dimension, requiring TSVs to maintain stable voltage levels with minimal noise coupling between power and signal domains. The target specifications typically demand power delivery network impedance below 1 milliohm at frequencies up to 1 GHz, while simultaneously ensuring that switching noise does not degrade signal quality beyond acceptable thresholds.

Thermal management objectives have become increasingly important as TSV density increases, with performance goals focusing on maintaining junction temperatures below critical thresholds while ensuring uniform heat distribution across the three-dimensional structure. These thermal considerations directly impact electrical performance, creating interdependent optimization challenges that require holistic design approaches.

Market Demand for High-Density TSV Applications

The semiconductor industry's relentless pursuit of miniaturization and performance enhancement has created unprecedented demand for high-density Through-Silicon Via (TSV) applications. This demand stems from the fundamental limitations of traditional wire bonding and flip-chip technologies in meeting the stringent requirements of modern electronic systems. As device geometries continue to shrink and functional complexity increases, TSV technology has emerged as a critical enabler for three-dimensional integrated circuits and advanced packaging solutions.

Consumer electronics represent the largest market segment driving TSV adoption, particularly in smartphones, tablets, and wearable devices. These applications require ultra-compact form factors while maintaining high performance and low power consumption. Memory stacking applications, including DRAM and NAND flash configurations, have become primary beneficiaries of high-density TSV implementations. The ability to vertically integrate multiple memory dies significantly reduces footprint while improving bandwidth and reducing latency compared to conventional planar architectures.

Data center and high-performance computing applications constitute another major demand driver for advanced TSV solutions. Server processors, graphics processing units, and artificial intelligence accelerators increasingly rely on TSV-enabled architectures to achieve the necessary memory bandwidth and computational density. The growing adoption of machine learning and artificial intelligence workloads has intensified requirements for memory-processor integration, making TSV technology indispensable for next-generation computing platforms.

Automotive electronics present an emerging but rapidly expanding market for high-density TSV applications. Advanced driver assistance systems, autonomous vehicle platforms, and electric vehicle power management systems require robust, high-performance semiconductor solutions capable of operating in harsh environments. TSV technology enables the integration of multiple sensor interfaces, processing units, and power management functions within compact, reliable packages suitable for automotive deployment.

The telecommunications infrastructure sector, particularly with the deployment of fifth-generation wireless networks, has generated substantial demand for TSV-enabled radio frequency and mixed-signal integrated circuits. Base station equipment, network processors, and optical communication modules increasingly incorporate TSV technology to achieve the performance and integration levels required for modern communication systems.

Market growth is further accelerated by the Internet of Things ecosystem, where miniaturization and power efficiency are paramount. Edge computing devices, sensor nodes, and wireless communication modules benefit significantly from TSV-enabled integration, allowing manufacturers to deliver enhanced functionality within severely constrained form factors while maintaining cost competitiveness in high-volume applications.

Consumer electronics represent the largest market segment driving TSV adoption, particularly in smartphones, tablets, and wearable devices. These applications require ultra-compact form factors while maintaining high performance and low power consumption. Memory stacking applications, including DRAM and NAND flash configurations, have become primary beneficiaries of high-density TSV implementations. The ability to vertically integrate multiple memory dies significantly reduces footprint while improving bandwidth and reducing latency compared to conventional planar architectures.

Data center and high-performance computing applications constitute another major demand driver for advanced TSV solutions. Server processors, graphics processing units, and artificial intelligence accelerators increasingly rely on TSV-enabled architectures to achieve the necessary memory bandwidth and computational density. The growing adoption of machine learning and artificial intelligence workloads has intensified requirements for memory-processor integration, making TSV technology indispensable for next-generation computing platforms.

Automotive electronics present an emerging but rapidly expanding market for high-density TSV applications. Advanced driver assistance systems, autonomous vehicle platforms, and electric vehicle power management systems require robust, high-performance semiconductor solutions capable of operating in harsh environments. TSV technology enables the integration of multiple sensor interfaces, processing units, and power management functions within compact, reliable packages suitable for automotive deployment.

The telecommunications infrastructure sector, particularly with the deployment of fifth-generation wireless networks, has generated substantial demand for TSV-enabled radio frequency and mixed-signal integrated circuits. Base station equipment, network processors, and optical communication modules increasingly incorporate TSV technology to achieve the performance and integration levels required for modern communication systems.

Market growth is further accelerated by the Internet of Things ecosystem, where miniaturization and power efficiency are paramount. Edge computing devices, sensor nodes, and wireless communication modules benefit significantly from TSV-enabled integration, allowing manufacturers to deliver enhanced functionality within severely constrained form factors while maintaining cost competitiveness in high-volume applications.

Current TSV Performance Challenges in Dense Environments

Through-Silicon Via (TSV) technology faces significant performance degradation when deployed in signal-dense environments, where multiple high-frequency signals traverse closely packed vertical interconnects. The primary challenge stems from electromagnetic interference and crosstalk between adjacent TSVs, which becomes exponentially more problematic as signal density increases. This interference manifests as signal integrity issues, including increased jitter, reduced signal-to-noise ratios, and timing uncertainties that can compromise overall system reliability.

Thermal management represents another critical challenge in dense TSV configurations. The concentrated heat generation from multiple active signal paths creates localized hot spots that affect electrical characteristics and mechanical stability. Temperature variations across the silicon substrate lead to differential thermal expansion, potentially causing stress-induced failures and performance variations. The thermal resistance of TSV structures becomes particularly problematic when multiple vias operate simultaneously at high frequencies.

Power delivery integrity suffers considerably in dense environments due to simultaneous switching noise and ground bounce effects. When numerous TSVs switch concurrently, the resulting current transients create voltage fluctuations across power distribution networks. This phenomenon is amplified by the parasitic inductance and resistance inherent in TSV structures, leading to power supply noise that can propagate throughout the system and affect sensitive analog circuits.

Manufacturing variability poses additional constraints on TSV performance in dense configurations. Process variations in via diameter, sidewall roughness, and fill quality become more critical when multiple TSVs must maintain consistent electrical characteristics. These variations create performance mismatches that can lead to timing skew and signal quality degradation across parallel data paths.

Electromagnetic coupling between TSVs intensifies with reduced pitch spacing, creating complex interaction patterns that are difficult to predict and control. The coupling mechanisms include capacitive, inductive, and substrate-mediated interference, each contributing to performance degradation through different frequency-dependent mechanisms. These effects are particularly pronounced in mixed-signal applications where digital switching noise can interfere with sensitive analog signal paths.

Current design methodologies struggle to adequately model and predict TSV behavior in dense environments, creating gaps between simulated and actual performance. The computational complexity of full-wave electromagnetic simulations for large TSV arrays often necessitates simplified models that may not capture critical interaction effects, leading to suboptimal design decisions and unexpected performance issues in production systems.

Thermal management represents another critical challenge in dense TSV configurations. The concentrated heat generation from multiple active signal paths creates localized hot spots that affect electrical characteristics and mechanical stability. Temperature variations across the silicon substrate lead to differential thermal expansion, potentially causing stress-induced failures and performance variations. The thermal resistance of TSV structures becomes particularly problematic when multiple vias operate simultaneously at high frequencies.

Power delivery integrity suffers considerably in dense environments due to simultaneous switching noise and ground bounce effects. When numerous TSVs switch concurrently, the resulting current transients create voltage fluctuations across power distribution networks. This phenomenon is amplified by the parasitic inductance and resistance inherent in TSV structures, leading to power supply noise that can propagate throughout the system and affect sensitive analog circuits.

Manufacturing variability poses additional constraints on TSV performance in dense configurations. Process variations in via diameter, sidewall roughness, and fill quality become more critical when multiple TSVs must maintain consistent electrical characteristics. These variations create performance mismatches that can lead to timing skew and signal quality degradation across parallel data paths.

Electromagnetic coupling between TSVs intensifies with reduced pitch spacing, creating complex interaction patterns that are difficult to predict and control. The coupling mechanisms include capacitive, inductive, and substrate-mediated interference, each contributing to performance degradation through different frequency-dependent mechanisms. These effects are particularly pronounced in mixed-signal applications where digital switching noise can interfere with sensitive analog signal paths.

Current design methodologies struggle to adequately model and predict TSV behavior in dense environments, creating gaps between simulated and actual performance. The computational complexity of full-wave electromagnetic simulations for large TSV arrays often necessitates simplified models that may not capture critical interaction effects, leading to suboptimal design decisions and unexpected performance issues in production systems.

Existing TSV Performance Analysis Solutions

01 TSV structure design and manufacturing process optimization

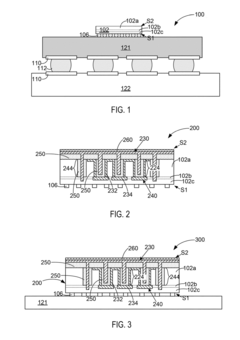

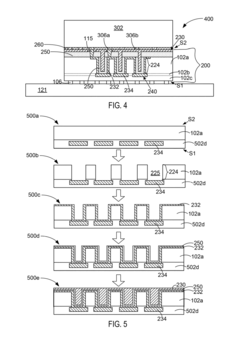

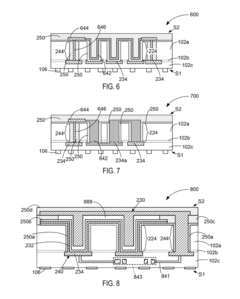

Through-silicon via (TSV) technology involves optimizing the structural design and manufacturing process to improve performance. This includes controlling the diameter, depth, aspect ratio, and sidewall profile of TSVs. Advanced etching techniques, deposition methods, and filling processes are employed to create high-quality TSVs with minimal defects. Process parameters such as temperature, pressure, and material selection are carefully controlled to enhance electrical performance and mechanical reliability.- TSV structure design and formation methods: Through-silicon vias (TSVs) can be formed using various structural designs and fabrication methods to improve performance. Key aspects include via formation techniques, filling materials, and dimensional optimization. Different approaches to creating the via holes and subsequent processing steps can significantly impact the electrical and thermal performance of the TSV interconnects.

- TSV electrical performance optimization: The electrical characteristics of TSVs can be enhanced through various techniques including impedance matching, capacitance reduction, and signal integrity improvements. Methods involve optimizing the conductive fill material, insulation layers, and geometric parameters to reduce parasitic effects and improve signal transmission quality. These approaches help minimize signal loss and crosstalk in high-speed applications.

- TSV thermal management and reliability: Thermal performance and reliability of TSV structures can be improved through proper material selection and structural design. Techniques include managing thermal expansion mismatches, preventing void formation, and ensuring mechanical stability under thermal cycling. Enhanced thermal dissipation paths and stress management strategies contribute to improved long-term reliability and performance stability.

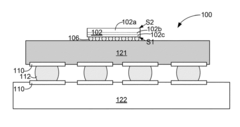

- TSV integration in 3D packaging: TSV technology enables three-dimensional integrated circuit packaging with improved performance characteristics. Integration methods focus on die stacking, interconnection schemes, and manufacturing processes that leverage TSVs for vertical electrical connections. These approaches facilitate higher density packaging, shorter interconnect lengths, and improved overall system performance.

- TSV testing and characterization methods: Various testing and characterization techniques are employed to evaluate TSV performance metrics including electrical continuity, resistance measurements, and defect detection. Advanced inspection methods and measurement systems enable quality control and performance validation during manufacturing. These approaches ensure TSVs meet specified performance requirements for high-reliability applications.

02 TSV electrical performance enhancement through material selection

The electrical performance of TSVs can be significantly improved through careful selection of conductive materials, barrier layers, and dielectric materials. Advanced metallization schemes using copper, tungsten, or other conductive materials with optimized resistivity are implemented. Barrier layers prevent diffusion and reduce parasitic capacitance. The choice of insulating materials and their deposition methods directly impacts signal integrity, power delivery, and overall electrical characteristics of the TSV interconnects.Expand Specific Solutions03 Thermal management and stress reduction in TSV structures

Managing thermal effects and mechanical stress is critical for TSV performance. Techniques include optimizing the coefficient of thermal expansion matching between different materials, implementing stress-relief structures, and designing thermal dissipation pathways. Advanced modeling and simulation methods predict thermal behavior and stress distribution. Material selection and structural modifications help minimize warpage, cracking, and delamination caused by thermal cycling and mechanical stress during manufacturing and operation.Expand Specific Solutions04 TSV interconnect reliability and testing methodologies

Ensuring long-term reliability of TSV interconnects requires comprehensive testing and qualification methods. This includes electrical testing for resistance, capacitance, and signal integrity, as well as reliability testing under various stress conditions. Advanced inspection techniques such as X-ray imaging, acoustic microscopy, and electrical probing are used to detect defects. Accelerated life testing and failure analysis help identify potential failure mechanisms and improve design robustness.Expand Specific Solutions05 Advanced TSV integration for 3D packaging applications

TSV technology enables advanced three-dimensional integrated circuit packaging with improved performance density and reduced footprint. Integration strategies include die stacking, wafer-level packaging, and heterogeneous integration of different chip technologies. Design considerations address signal routing, power distribution networks, and thermal pathways across multiple stacked layers. Advanced bonding techniques and alignment methods ensure precise interconnection between layers while maintaining high yield and performance.Expand Specific Solutions

Key Players in TSV and 3D IC Industry

The TSV (Through-Silicon Via) performance characterization in signal-dense environments represents a mature yet rapidly evolving technological domain driven by increasing demand for high-density 3D integrated circuits. The industry is experiencing significant growth, with the market expanding due to advanced packaging requirements in mobile devices, AI processors, and high-performance computing applications. Technology maturity varies across players, with established semiconductor giants like Samsung Electronics, Sony Group, and Qualcomm leading in commercial TSV implementations, while memory specialists like Micron Technology and ChangXin Memory Technologies focus on DRAM applications. Research institutions including Xidian University, Tianjin University, and Beijing University of Technology contribute fundamental research, while companies like IBM and Huawei Technologies drive innovation in enterprise and telecommunications applications. The competitive landscape shows a clear division between volume manufacturers achieving production-scale TSV integration and specialized players developing next-generation solutions for emerging signal integrity challenges.

Sony Group Corp.

Technical Solution: Sony has developed TSV characterization techniques for advanced image sensor and mixed-signal applications, particularly focusing on maintaining signal quality in dense pixel arrays and analog processing circuits. Their methodology addresses the unique challenges of characterizing TSV performance in environments with mixed digital and analog signals, including noise coupling analysis and signal isolation techniques. Sony's approach incorporates specialized measurement setups for evaluating TSV impact on sensitive analog circuits and high-resolution imaging systems. The company has developed proprietary modeling techniques to predict TSV behavior in signal-dense environments typical of advanced CMOS image sensors and related processing circuits.

Strengths: Specialized expertise in mixed-signal TSV applications with focus on high-performance imaging systems. Weaknesses: Characterization methods may be specialized for imaging applications with limited general applicability.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced TSV technology for 3D memory stacking and high-density packaging solutions. Their approach focuses on optimizing TSV diameter, pitch, and aspect ratio to minimize signal interference in dense environments. The company employs sophisticated electromagnetic modeling and simulation tools to characterize TSV performance, particularly addressing crosstalk mitigation through optimized ground shielding structures and differential signaling techniques. Samsung's TSV implementation includes advanced materials engineering for better conductivity and reduced parasitic effects, enabling high-speed signal transmission in their 3D NAND and DRAM products.

Strengths: Industry-leading 3D memory technology with proven TSV manufacturing capabilities at scale. Weaknesses: High manufacturing complexity and cost for advanced TSV processes.

Core Innovations in TSV Signal Integrity Modeling

Through-silicon via detecting circuit, method and integrated circuit having the same

PatentActiveUS11408929B2

Innovation

- A through-silicon via (TSV) detecting circuit and method that includes an input circuit with a switching mechanism to transmit a power signal and a comparison circuit to assess signal integrity, allowing for the detection of TSV connectivity by comparing signals across TSVs and a reference signal, suitable for large-scale integrated circuits.

Through-silicon via (TSV)-based devices and associated techniques and configurations

PatentActiveUS20150255372A1

Innovation

- The implementation of through-silicon via (TSV)-based devices, including capacitors, resistors, and resonators, which utilize TSV structures extending through the bulk semiconductor material, electrically insulative materials, and electrode or resistor materials within these structures to provide enhanced capacitance and resistance while reducing footprint and inductance.

Thermal Management in High-Density TSV Arrays

Thermal management in high-density TSV arrays represents one of the most critical challenges in advanced 3D integrated circuit design, particularly when operating in signal-dense environments. As TSV pitch continues to shrink and integration density increases, the thermal coupling between adjacent vias creates complex heat dissipation patterns that significantly impact both electrical performance and reliability. The concentrated power density in these arrays can reach levels exceeding 100 W/cm², creating localized hotspots that degrade signal integrity and accelerate device aging.

The fundamental thermal challenge stems from the inherent material properties mismatch between TSVs and the surrounding silicon substrate. Copper TSVs, with their high thermal conductivity of approximately 400 W/m·K, create preferential heat conduction paths that can lead to non-uniform temperature distributions across the die. This thermal gradient becomes more pronounced in high-density configurations where the spacing between TSVs approaches the thermal diffusion length, typically in the range of 10-50 micrometers for silicon at operating frequencies.

Current thermal management approaches focus on both passive and active cooling strategies. Passive techniques include optimized TSV placement algorithms that distribute thermal loads more evenly, implementation of thermal vias specifically designed for heat extraction, and integration of high-thermal-conductivity materials such as diamond-like carbon coatings. These methods can reduce peak temperatures by 15-25% compared to conventional uniform TSV distributions.

Active thermal management solutions involve dynamic thermal monitoring and adaptive power management systems. Real-time temperature sensing through embedded thermal diodes enables closed-loop control of power distribution, allowing systems to throttle performance in thermally constrained regions while maintaining overall functionality. Advanced packaging solutions incorporating microfluidic cooling channels and thermoelectric coolers are being developed for extreme high-density applications.

The interaction between thermal effects and signal performance creates additional complexity in TSV characterization. Elevated temperatures increase resistivity in copper conductors by approximately 0.4% per degree Celsius, while simultaneously affecting the dielectric properties of surrounding materials. This temperature-dependent behavior necessitates comprehensive thermal-electrical co-simulation methodologies to accurately predict system performance under realistic operating conditions.

Emerging solutions include novel TSV architectures with integrated thermal management features, such as hollow TSVs for coolant circulation and composite TSV structures that optimize both electrical and thermal performance simultaneously.

The fundamental thermal challenge stems from the inherent material properties mismatch between TSVs and the surrounding silicon substrate. Copper TSVs, with their high thermal conductivity of approximately 400 W/m·K, create preferential heat conduction paths that can lead to non-uniform temperature distributions across the die. This thermal gradient becomes more pronounced in high-density configurations where the spacing between TSVs approaches the thermal diffusion length, typically in the range of 10-50 micrometers for silicon at operating frequencies.

Current thermal management approaches focus on both passive and active cooling strategies. Passive techniques include optimized TSV placement algorithms that distribute thermal loads more evenly, implementation of thermal vias specifically designed for heat extraction, and integration of high-thermal-conductivity materials such as diamond-like carbon coatings. These methods can reduce peak temperatures by 15-25% compared to conventional uniform TSV distributions.

Active thermal management solutions involve dynamic thermal monitoring and adaptive power management systems. Real-time temperature sensing through embedded thermal diodes enables closed-loop control of power distribution, allowing systems to throttle performance in thermally constrained regions while maintaining overall functionality. Advanced packaging solutions incorporating microfluidic cooling channels and thermoelectric coolers are being developed for extreme high-density applications.

The interaction between thermal effects and signal performance creates additional complexity in TSV characterization. Elevated temperatures increase resistivity in copper conductors by approximately 0.4% per degree Celsius, while simultaneously affecting the dielectric properties of surrounding materials. This temperature-dependent behavior necessitates comprehensive thermal-electrical co-simulation methodologies to accurately predict system performance under realistic operating conditions.

Emerging solutions include novel TSV architectures with integrated thermal management features, such as hollow TSVs for coolant circulation and composite TSV structures that optimize both electrical and thermal performance simultaneously.

Electromagnetic Compatibility Standards for TSV Systems

Electromagnetic compatibility (EMC) standards for Through-Silicon Via (TSV) systems represent a critical regulatory framework that governs the electromagnetic behavior of three-dimensional integrated circuits in signal-dense environments. These standards establish mandatory requirements for electromagnetic emissions, susceptibility thresholds, and interference mitigation protocols that TSV-enabled devices must satisfy before market deployment.

The primary EMC standards applicable to TSV systems include IEC 61967 series for integrated circuit emissions measurement, IEC 62132 series for immunity testing, and CISPR 25 for automotive electronic components. These standards define specific test methodologies, measurement procedures, and compliance criteria that address the unique electromagnetic characteristics of vertically stacked semiconductor architectures. The standards particularly emphasize near-field coupling effects and substrate-mediated interference propagation mechanisms inherent in TSV structures.

Compliance testing protocols under these standards require specialized measurement setups capable of characterizing electromagnetic fields in three-dimensional space around TSV packages. The standards mandate evaluation of conducted and radiated emissions across frequency ranges from 150 kHz to 6 GHz, with extended coverage up to 18 GHz for high-speed digital applications. Critical parameters include common-mode and differential-mode emissions, power supply rejection ratios, and substrate noise coupling coefficients.

Recent amendments to EMC standards have incorporated TSV-specific test conditions, including multi-die switching scenarios and through-silicon current path evaluations. These updates address the electromagnetic coupling between vertically adjacent functional blocks and establish limits for inter-die interference levels. The standards now include provisions for characterizing electromagnetic field distributions within TSV arrays and quantifying the shielding effectiveness of through-silicon interconnects.

Regulatory bodies across different regions have begun harmonizing EMC requirements for TSV systems, with particular focus on automotive and telecommunications applications where electromagnetic reliability is paramount. These evolving standards continue to adapt to emerging TSV technologies and increasingly complex three-dimensional integration schemes.

The primary EMC standards applicable to TSV systems include IEC 61967 series for integrated circuit emissions measurement, IEC 62132 series for immunity testing, and CISPR 25 for automotive electronic components. These standards define specific test methodologies, measurement procedures, and compliance criteria that address the unique electromagnetic characteristics of vertically stacked semiconductor architectures. The standards particularly emphasize near-field coupling effects and substrate-mediated interference propagation mechanisms inherent in TSV structures.

Compliance testing protocols under these standards require specialized measurement setups capable of characterizing electromagnetic fields in three-dimensional space around TSV packages. The standards mandate evaluation of conducted and radiated emissions across frequency ranges from 150 kHz to 6 GHz, with extended coverage up to 18 GHz for high-speed digital applications. Critical parameters include common-mode and differential-mode emissions, power supply rejection ratios, and substrate noise coupling coefficients.

Recent amendments to EMC standards have incorporated TSV-specific test conditions, including multi-die switching scenarios and through-silicon current path evaluations. These updates address the electromagnetic coupling between vertically adjacent functional blocks and establish limits for inter-die interference levels. The standards now include provisions for characterizing electromagnetic field distributions within TSV arrays and quantifying the shielding effectiveness of through-silicon interconnects.

Regulatory bodies across different regions have begun harmonizing EMC requirements for TSV systems, with particular focus on automotive and telecommunications applications where electromagnetic reliability is paramount. These evolving standards continue to adapt to emerging TSV technologies and increasingly complex three-dimensional integration schemes.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!