Comparing DSP and CPLD: Use Cases and Adaptability

FEB 26, 20268 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DSP and CPLD Technology Background and Objectives

Digital Signal Processors (DSPs) and Complex Programmable Logic Devices (CPLDs) represent two distinct yet complementary approaches to digital signal processing and control applications. Both technologies emerged from the need to bridge the gap between general-purpose processors and dedicated hardware solutions, offering programmable alternatives to fixed-function integrated circuits.

DSP technology originated in the 1980s as a specialized microprocessor architecture optimized for mathematical operations commonly used in signal processing. These processors feature dedicated multiply-accumulate units, specialized addressing modes, and optimized instruction sets designed to efficiently execute algorithms such as digital filtering, Fast Fourier Transforms, and correlation functions. The evolution of DSP architecture has consistently focused on maximizing computational throughput while maintaining programming flexibility.

CPLD technology developed as an extension of Programmable Logic Arrays (PLAs) and Programmable Array Logic (PAL) devices. CPLDs provide a matrix of programmable logic blocks interconnected through a global routing architecture, enabling the implementation of complex digital logic functions. Unlike their predecessors, CPLDs offer non-volatile configuration memory and significantly higher gate counts, making them suitable for more sophisticated applications.

The fundamental objective driving DSP development centers on achieving optimal performance for computationally intensive signal processing tasks while maintaining software programmability. This includes minimizing instruction cycle counts for common operations, reducing memory access latencies, and providing specialized peripherals for real-time data acquisition and output.

CPLD development objectives focus on delivering flexible digital logic implementation capabilities with predictable timing characteristics and instant-on functionality. The emphasis lies on providing sufficient logic resources, flexible I/O configurations, and deterministic propagation delays essential for control and interface applications.

The convergence of these technologies addresses the growing demand for adaptable solutions that can handle both signal processing algorithms and digital control functions within single-chip implementations. Modern applications increasingly require hybrid approaches that leverage the computational strengths of DSPs alongside the logic flexibility and timing predictability of CPLDs.

Contemporary development trends emphasize integration and optimization, with manufacturers exploring architectures that combine DSP cores with programmable logic fabrics, creating platforms capable of addressing diverse application requirements while maintaining the distinct advantages of each technology approach.

DSP technology originated in the 1980s as a specialized microprocessor architecture optimized for mathematical operations commonly used in signal processing. These processors feature dedicated multiply-accumulate units, specialized addressing modes, and optimized instruction sets designed to efficiently execute algorithms such as digital filtering, Fast Fourier Transforms, and correlation functions. The evolution of DSP architecture has consistently focused on maximizing computational throughput while maintaining programming flexibility.

CPLD technology developed as an extension of Programmable Logic Arrays (PLAs) and Programmable Array Logic (PAL) devices. CPLDs provide a matrix of programmable logic blocks interconnected through a global routing architecture, enabling the implementation of complex digital logic functions. Unlike their predecessors, CPLDs offer non-volatile configuration memory and significantly higher gate counts, making them suitable for more sophisticated applications.

The fundamental objective driving DSP development centers on achieving optimal performance for computationally intensive signal processing tasks while maintaining software programmability. This includes minimizing instruction cycle counts for common operations, reducing memory access latencies, and providing specialized peripherals for real-time data acquisition and output.

CPLD development objectives focus on delivering flexible digital logic implementation capabilities with predictable timing characteristics and instant-on functionality. The emphasis lies on providing sufficient logic resources, flexible I/O configurations, and deterministic propagation delays essential for control and interface applications.

The convergence of these technologies addresses the growing demand for adaptable solutions that can handle both signal processing algorithms and digital control functions within single-chip implementations. Modern applications increasingly require hybrid approaches that leverage the computational strengths of DSPs alongside the logic flexibility and timing predictability of CPLDs.

Contemporary development trends emphasize integration and optimization, with manufacturers exploring architectures that combine DSP cores with programmable logic fabrics, creating platforms capable of addressing diverse application requirements while maintaining the distinct advantages of each technology approach.

Market Demand Analysis for DSP and CPLD Solutions

The global market for DSP and CPLD solutions demonstrates robust growth driven by increasing digitization across multiple industries. DSP processors find substantial demand in telecommunications infrastructure, where 5G network deployment requires advanced signal processing capabilities for beamforming, channel estimation, and interference mitigation. The automotive sector represents another significant growth area, with DSPs essential for advanced driver assistance systems, radar processing, and electric vehicle motor control applications.

CPLD solutions experience strong market traction in industrial automation and control systems, where their deterministic timing characteristics and instant-on capabilities provide critical advantages. The aerospace and defense sectors maintain consistent demand for both technologies, with DSPs handling complex radar and communication signal processing while CPLDs manage system control and interface functions in mission-critical applications.

Consumer electronics markets drive substantial volume demand for DSP solutions, particularly in audio processing, image enhancement, and wireless communication devices. Smart home devices, wearables, and IoT endpoints increasingly integrate DSP capabilities for voice recognition, sensor fusion, and edge computing applications. The proliferation of artificial intelligence at the edge creates new opportunities for specialized DSP architectures optimized for machine learning inference.

Medical device markets present growing opportunities for both technologies, with DSPs enabling advanced imaging systems, patient monitoring equipment, and diagnostic instruments. CPLDs serve critical roles in medical device control systems where safety, reliability, and real-time response requirements are paramount.

Regional market dynamics show strong growth in Asia-Pacific regions, driven by manufacturing expansion and infrastructure development. North American and European markets focus increasingly on high-value applications in automotive, industrial, and defense sectors. The shift toward edge computing and distributed intelligence creates new market segments where the complementary strengths of DSP and CPLD technologies address different aspects of system requirements.

Market consolidation trends indicate increasing integration of DSP and CPLD functionalities within system-on-chip solutions, while specialized applications continue to drive demand for discrete implementations where performance optimization and flexibility remain critical factors.

CPLD solutions experience strong market traction in industrial automation and control systems, where their deterministic timing characteristics and instant-on capabilities provide critical advantages. The aerospace and defense sectors maintain consistent demand for both technologies, with DSPs handling complex radar and communication signal processing while CPLDs manage system control and interface functions in mission-critical applications.

Consumer electronics markets drive substantial volume demand for DSP solutions, particularly in audio processing, image enhancement, and wireless communication devices. Smart home devices, wearables, and IoT endpoints increasingly integrate DSP capabilities for voice recognition, sensor fusion, and edge computing applications. The proliferation of artificial intelligence at the edge creates new opportunities for specialized DSP architectures optimized for machine learning inference.

Medical device markets present growing opportunities for both technologies, with DSPs enabling advanced imaging systems, patient monitoring equipment, and diagnostic instruments. CPLDs serve critical roles in medical device control systems where safety, reliability, and real-time response requirements are paramount.

Regional market dynamics show strong growth in Asia-Pacific regions, driven by manufacturing expansion and infrastructure development. North American and European markets focus increasingly on high-value applications in automotive, industrial, and defense sectors. The shift toward edge computing and distributed intelligence creates new market segments where the complementary strengths of DSP and CPLD technologies address different aspects of system requirements.

Market consolidation trends indicate increasing integration of DSP and CPLD functionalities within system-on-chip solutions, while specialized applications continue to drive demand for discrete implementations where performance optimization and flexibility remain critical factors.

Current State and Challenges of DSP vs CPLD Technologies

Digital Signal Processors (DSPs) and Complex Programmable Logic Devices (CPLDs) represent two distinct technological paradigms, each with unique architectural foundations and operational characteristics. DSPs are specialized microprocessors optimized for mathematical operations, featuring dedicated multiply-accumulate units, specialized instruction sets, and Harvard architecture for simultaneous data and instruction access. In contrast, CPLDs are programmable logic devices built on sum-of-products architecture, offering immediate combinational logic implementation and deterministic timing characteristics.

The current technological landscape reveals significant performance disparities between these platforms. Modern DSPs, such as Texas Instruments' C6000 series and Analog Devices' SHARC processors, deliver exceptional computational throughput for sequential processing tasks, achieving clock speeds exceeding 1 GHz with optimized floating-point operations. However, they face inherent limitations in parallel processing scenarios and real-time deterministic response requirements. CPLDs, including Intel's MAX series and Xilinx's CoolRunner devices, excel in providing predictable timing behavior and parallel logic implementation but are constrained by limited gate counts and reduced computational complexity compared to their FPGA counterparts.

Power consumption remains a critical differentiator, with CPLDs demonstrating superior energy efficiency in low-complexity applications due to their non-volatile configuration memory and simplified architecture. DSPs typically consume more power during intensive computational tasks but offer better performance-per-watt ratios for algorithm-heavy applications. Geographic distribution of expertise shows concentrated development in North America and Asia, with established semiconductor companies maintaining technological leadership in both domains.

Integration challenges persist as system designers increasingly require hybrid solutions combining DSP computational power with CPLD's deterministic logic capabilities. The emergence of heterogeneous architectures and system-on-chip solutions reflects industry efforts to bridge these technological gaps, though optimal integration methodologies remain under active development across major semiconductor manufacturers.

The current technological landscape reveals significant performance disparities between these platforms. Modern DSPs, such as Texas Instruments' C6000 series and Analog Devices' SHARC processors, deliver exceptional computational throughput for sequential processing tasks, achieving clock speeds exceeding 1 GHz with optimized floating-point operations. However, they face inherent limitations in parallel processing scenarios and real-time deterministic response requirements. CPLDs, including Intel's MAX series and Xilinx's CoolRunner devices, excel in providing predictable timing behavior and parallel logic implementation but are constrained by limited gate counts and reduced computational complexity compared to their FPGA counterparts.

Power consumption remains a critical differentiator, with CPLDs demonstrating superior energy efficiency in low-complexity applications due to their non-volatile configuration memory and simplified architecture. DSPs typically consume more power during intensive computational tasks but offer better performance-per-watt ratios for algorithm-heavy applications. Geographic distribution of expertise shows concentrated development in North America and Asia, with established semiconductor companies maintaining technological leadership in both domains.

Integration challenges persist as system designers increasingly require hybrid solutions combining DSP computational power with CPLD's deterministic logic capabilities. The emergence of heterogeneous architectures and system-on-chip solutions reflects industry efforts to bridge these technological gaps, though optimal integration methodologies remain under active development across major semiconductor manufacturers.

Current DSP and CPLD Implementation Solutions

01 DSP and CPLD collaborative signal processing architecture

Digital Signal Processors (DSP) and Complex Programmable Logic Devices (CPLD) can be integrated in a collaborative architecture where DSP handles complex computational tasks while CPLD manages high-speed logic control and interface timing. This combination leverages the computational power of DSP for algorithm implementation and the flexibility of CPLD for custom logic design, enabling efficient signal processing systems with improved performance and adaptability.- DSP and CPLD collaborative signal processing architecture: Digital Signal Processors (DSP) and Complex Programmable Logic Devices (CPLD) can be integrated in a collaborative architecture where DSP handles complex computational tasks while CPLD manages high-speed logic control and interface timing. This architecture leverages the computational strength of DSP for algorithm implementation and the flexibility of CPLD for custom logic design, enabling efficient signal processing and control in various applications.

- CPLD-based DSP peripheral interface expansion: CPLD devices can be utilized to expand the peripheral interfaces of DSP systems, providing additional I/O capabilities and custom interface protocols. This approach allows for flexible connection of multiple external devices and sensors to the DSP core, while the CPLD handles protocol conversion, timing control, and data buffering, thereby reducing the burden on the DSP and improving system scalability.

- DSP and CPLD based real-time control systems: The combination of DSP and CPLD enables the development of high-performance real-time control systems. The DSP executes control algorithms and performs numerical computations, while the CPLD implements time-critical logic functions, generates precise timing signals, and manages interrupt handling. This division of labor ensures deterministic response times and reliable system operation in demanding control applications.

- CPLD-assisted DSP data acquisition and preprocessing: CPLD devices can serve as front-end processors for DSP-based data acquisition systems, handling tasks such as analog-to-digital conversion control, data formatting, and preliminary filtering. The CPLD preprocesses incoming data streams before passing them to the DSP for advanced processing, optimizing data flow and reducing latency in high-speed acquisition applications.

- Reconfigurable DSP-CPLD hybrid processing platform: A reconfigurable platform combining DSP and CPLD technologies provides adaptability for various signal processing tasks. The CPLD's reprogrammable nature allows for dynamic modification of hardware logic to accommodate different processing requirements, while the DSP maintains software-based algorithm flexibility. This hybrid approach enables system optimization for specific applications without hardware redesign.

02 CPLD-based DSP control and configuration interface

CPLD can serve as a control and configuration interface for DSP systems, managing peripheral device connections, data routing, and system initialization. The CPLD provides flexible logic implementation for address decoding, chip select generation, and timing control, allowing the DSP to focus on core processing tasks while the CPLD handles hardware-level interfacing and coordination between multiple components.Expand Specific Solutions03 High-speed data acquisition systems using DSP-CPLD integration

In high-speed data acquisition applications, CPLD can be utilized for front-end data buffering, format conversion, and preprocessing, while DSP performs advanced signal analysis and processing. This architecture enables real-time data capture and processing with minimal latency, as CPLD handles time-critical operations and DSP executes complex algorithms for data interpretation and feature extraction.Expand Specific Solutions04 Reconfigurable DSP-CPLD systems for adaptive applications

The combination of DSP and CPLD enables reconfigurable systems that can adapt to different operational requirements. CPLD's reprogrammable nature allows for dynamic modification of hardware logic and interface protocols, while DSP software can be updated for different processing algorithms. This adaptability is particularly valuable in applications requiring field upgrades or multi-mode operation capabilities.Expand Specific Solutions05 Power management and resource optimization in DSP-CPLD systems

Effective power management and resource allocation strategies can be implemented in DSP-CPLD hybrid systems by distributing tasks according to power efficiency and processing requirements. CPLD can handle low-power state management, clock gating, and power sequencing, while DSP operates in optimized power modes based on computational load. This approach maximizes system efficiency and extends operational lifetime in power-constrained applications.Expand Specific Solutions

Major Players in DSP and CPLD Market Landscape

The DSP and CPLD technology landscape represents a mature market in the growth-to-consolidation phase, with established market segments exceeding $15 billion globally. The competitive environment is dominated by semiconductor giants like Texas Instruments and Intel leading DSP innovations, while Xilinx pioneered programmable logic solutions including CPLDs before its acquisition. Technology maturity varies significantly - DSPs have reached optimization phases with advanced architectures, whereas CPLDs maintain steady evolution focusing on power efficiency and integration. Key players like Ericsson and Huawei drive telecommunications applications, while emerging companies such as HyperX Logic explore specialized implementations. The adaptability comparison favors DSPs for signal-intensive applications and CPLDs for control logic, creating distinct but sometimes overlapping market niches with different technological trajectories.

Xilinx, Inc.

Technical Solution: Xilinx provides comprehensive FPGA and CPLD solutions with their CoolRunner-II CPLD family offering ultra-low power consumption (as low as 27µA) and fast propagation delays under 5ns. Their Zynq UltraScale+ MPSoCs integrate ARM processors with FPGA fabric, enabling hybrid DSP-CPLD functionality. The company's Vivado Design Suite provides unified development environment supporting both simple glue logic implementations typical of CPLDs and complex signal processing algorithms. Their adaptive computing approach allows runtime reconfiguration, making their solutions suitable for applications requiring both deterministic control logic and intensive mathematical computations. Xilinx's architecture supports seamless integration between processing systems and programmable logic, offering flexibility in partitioning DSP and control functions.

Strengths: Market leader in programmable logic with comprehensive toolchain and extensive IP library. Weaknesses: Higher cost compared to discrete DSP and CPLD solutions, steeper learning curve for complex designs.

Telefonaktiebolaget LM Ericsson

Technical Solution: Ericsson leverages both DSP and CPLD technologies in their radio access network solutions, utilizing DSP processors for baseband signal processing achieving throughput up to 20 Gbps in 5G applications, while employing CPLDs for timing-critical control functions and interface management with sub-microsecond response times. Their Radio System portfolio demonstrates hybrid architecture where DSP handles computationally intensive tasks like channel coding and modulation, while CPLDs manage deterministic control plane functions and hardware abstraction layers. Ericsson's software-defined radio approach allows dynamic reconfiguration of processing resources, adapting between DSP-intensive and control-logic-intensive operations based on network conditions. Their ASIC development includes custom solutions that integrate both DSP cores and programmable logic fabric, optimizing for telecommunications-specific requirements like low latency and high reliability.

Strengths: Extensive telecommunications expertise, proven scalability in carrier-grade deployments, strong focus on reliability and real-time performance. Weaknesses: Solutions primarily optimized for telecommunications applications, limited applicability to other market segments.

Core Technical Innovations in DSP-CPLD Integration

High-speed real-time band rejection filter based on CPLD (complex programmable logic device)

PatentInactiveCN201854251U

Innovation

- Design a real-time band stop filter based on CPLD, using the serial A/D module to collect analog signals, processing them through the digital band stop filter operation circuit, and outputting them through the serial D/A module, using IIR filters and elliptical filters The converter realizes high-speed real-time filtering, combines the fast conversion of A/D and D/A converters, and uses fixed-point calculation and floating-point quantification processing to improve the computing speed.

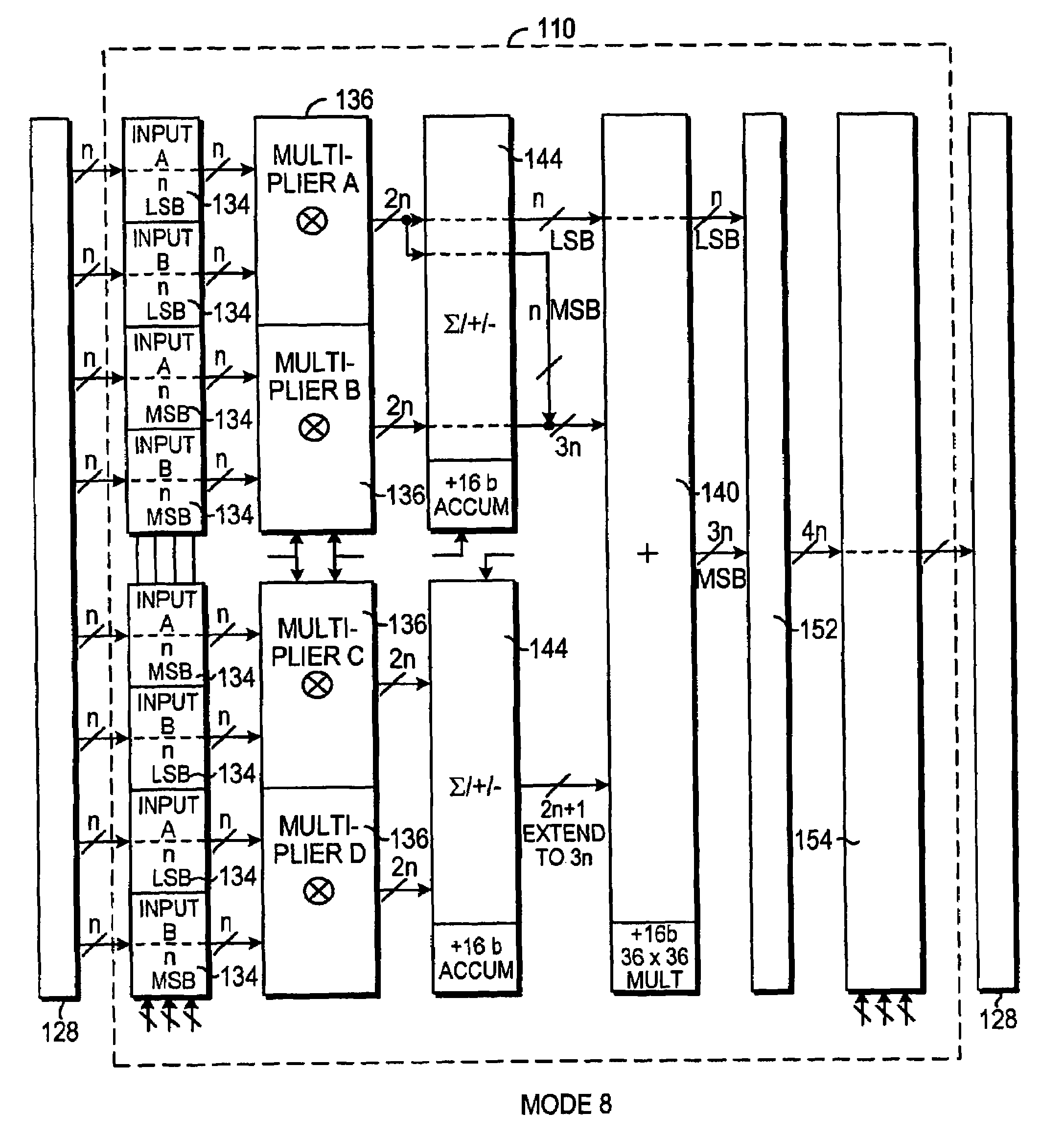

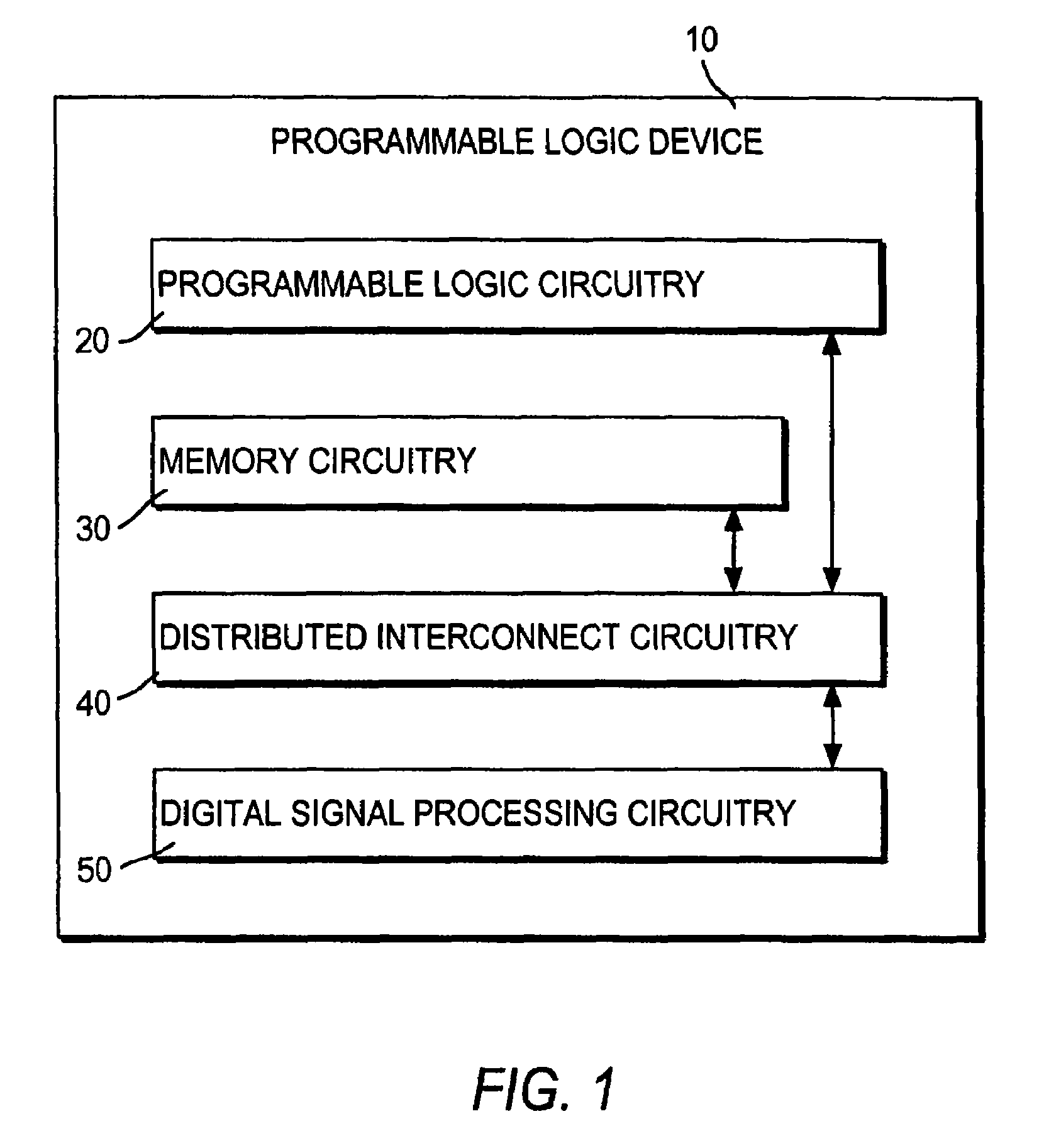

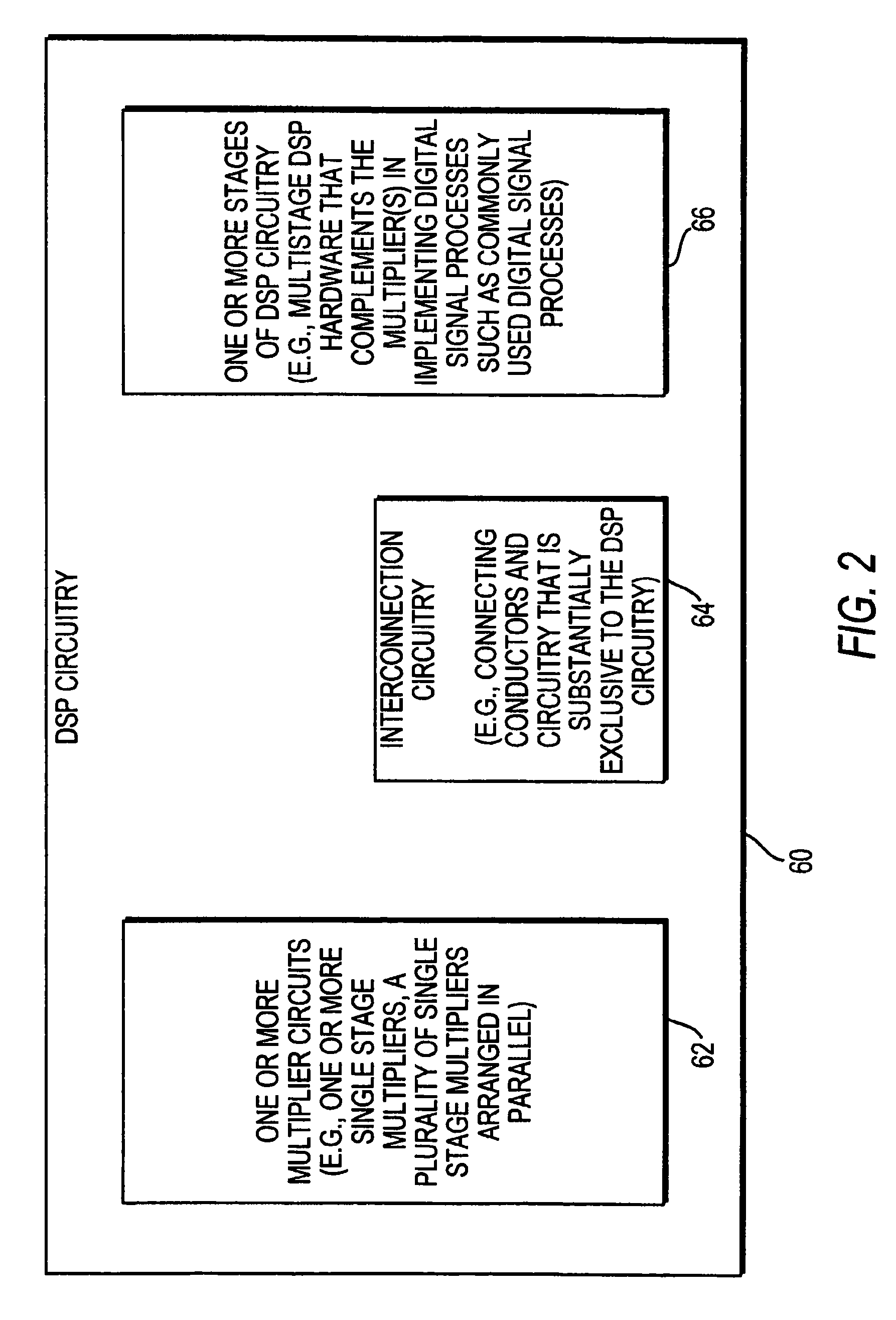

Devices and methods with programmable logic and digital signal processing regions

PatentInactiveUS7346644B1

Innovation

- Incorporating digital signal processing regions within programmable logic devices, which include programmable logic super-regions with dedicated circuitry for memory, logic, and interconnect resources, allowing for multistage digital signal processing operations and efficient use of existing resources.

Power Efficiency Considerations in DSP-CPLD Design

Power efficiency represents a critical design parameter when implementing DSP-CPLD hybrid architectures, as it directly impacts system performance, thermal management, and operational costs. The fundamental power consumption characteristics of DSPs and CPLDs differ significantly due to their architectural distinctions and operational methodologies.

DSP processors typically exhibit dynamic power consumption patterns that correlate with computational workload intensity. Modern DSP architectures incorporate sophisticated power management features including dynamic voltage and frequency scaling, clock gating, and power islands that can be selectively activated based on processing requirements. The power efficiency of DSPs is particularly advantageous in applications with variable computational demands, where idle or low-activity periods can leverage sleep modes to reduce overall energy consumption.

CPLDs demonstrate relatively static power consumption profiles that remain consistent regardless of logic utilization levels. The power draw primarily depends on the number of active logic elements and I/O operations rather than computational complexity. This characteristic makes CPLDs predictable in power budgeting but potentially less efficient in scenarios with intermittent processing requirements.

Hybrid DSP-CPLD designs must carefully balance power distribution between components to optimize overall system efficiency. Strategic partitioning of functions can significantly impact power consumption, where time-critical control logic implemented in CPLDs operates continuously while DSP cores handle intensive computations during specific intervals. This approach enables selective power management where DSP sections can enter low-power states while maintaining essential system functions through CPLD logic.

Advanced power optimization techniques in DSP-CPLD systems include intelligent task scheduling that maximizes DSP utilization periods while minimizing idle time, implementation of shared voltage domains to reduce power conversion losses, and utilization of CPLD-based power sequencing to manage DSP startup and shutdown cycles efficiently. Temperature-aware power management becomes crucial in these hybrid systems, as thermal coupling between components can affect overall system reliability and performance sustainability.

DSP processors typically exhibit dynamic power consumption patterns that correlate with computational workload intensity. Modern DSP architectures incorporate sophisticated power management features including dynamic voltage and frequency scaling, clock gating, and power islands that can be selectively activated based on processing requirements. The power efficiency of DSPs is particularly advantageous in applications with variable computational demands, where idle or low-activity periods can leverage sleep modes to reduce overall energy consumption.

CPLDs demonstrate relatively static power consumption profiles that remain consistent regardless of logic utilization levels. The power draw primarily depends on the number of active logic elements and I/O operations rather than computational complexity. This characteristic makes CPLDs predictable in power budgeting but potentially less efficient in scenarios with intermittent processing requirements.

Hybrid DSP-CPLD designs must carefully balance power distribution between components to optimize overall system efficiency. Strategic partitioning of functions can significantly impact power consumption, where time-critical control logic implemented in CPLDs operates continuously while DSP cores handle intensive computations during specific intervals. This approach enables selective power management where DSP sections can enter low-power states while maintaining essential system functions through CPLD logic.

Advanced power optimization techniques in DSP-CPLD systems include intelligent task scheduling that maximizes DSP utilization periods while minimizing idle time, implementation of shared voltage domains to reduce power conversion losses, and utilization of CPLD-based power sequencing to manage DSP startup and shutdown cycles efficiently. Temperature-aware power management becomes crucial in these hybrid systems, as thermal coupling between components can affect overall system reliability and performance sustainability.

Cost-Performance Trade-offs in Processing Architecture Selection

When evaluating DSP versus CPLD architectures, cost-performance considerations fundamentally shape selection decisions across different application domains. The economic implications extend beyond initial procurement costs to encompass development time, power consumption, scalability requirements, and long-term maintenance expenses.

DSP processors typically demonstrate superior cost-effectiveness in applications requiring intensive mathematical computations and signal processing algorithms. Their optimized instruction sets and dedicated multiply-accumulate units deliver exceptional performance per dollar for tasks such as digital filtering, FFT operations, and audio processing. However, this advantage diminishes when applications demand extensive parallel processing or real-time deterministic responses with minimal latency variations.

CPLD architectures present compelling cost-performance ratios for applications requiring custom logic implementation and parallel processing capabilities. While initial development costs may exceed DSP-based solutions due to hardware description language programming requirements, CPLDs offer significant advantages in applications demanding multiple simultaneous operations or specialized interface protocols. The reconfigurable nature of CPLDs provides long-term cost benefits through field upgrades and functionality extensions without hardware replacement.

Power consumption represents a critical cost factor, particularly in battery-powered or thermally constrained environments. Modern DSPs incorporate advanced power management features and can achieve remarkable efficiency in computational tasks through optimized silicon design. Conversely, CPLDs offer granular power control through selective logic block activation, potentially reducing overall system power consumption in applications with variable processing loads.

Development and deployment costs vary significantly between architectures. DSP solutions benefit from mature development ecosystems, extensive software libraries, and standardized debugging tools, reducing time-to-market and engineering costs. CPLD development requires specialized expertise in digital design methodologies, potentially increasing initial development expenses but offering greater customization flexibility and intellectual property protection.

The scalability dimension introduces additional cost-performance considerations. DSP architectures provide straightforward performance scaling through clock frequency adjustments or multi-core implementations, while CPLDs offer scalability through logic density increases and distributed processing architectures. Each approach presents distinct cost implications depending on application requirements and production volumes.

DSP processors typically demonstrate superior cost-effectiveness in applications requiring intensive mathematical computations and signal processing algorithms. Their optimized instruction sets and dedicated multiply-accumulate units deliver exceptional performance per dollar for tasks such as digital filtering, FFT operations, and audio processing. However, this advantage diminishes when applications demand extensive parallel processing or real-time deterministic responses with minimal latency variations.

CPLD architectures present compelling cost-performance ratios for applications requiring custom logic implementation and parallel processing capabilities. While initial development costs may exceed DSP-based solutions due to hardware description language programming requirements, CPLDs offer significant advantages in applications demanding multiple simultaneous operations or specialized interface protocols. The reconfigurable nature of CPLDs provides long-term cost benefits through field upgrades and functionality extensions without hardware replacement.

Power consumption represents a critical cost factor, particularly in battery-powered or thermally constrained environments. Modern DSPs incorporate advanced power management features and can achieve remarkable efficiency in computational tasks through optimized silicon design. Conversely, CPLDs offer granular power control through selective logic block activation, potentially reducing overall system power consumption in applications with variable processing loads.

Development and deployment costs vary significantly between architectures. DSP solutions benefit from mature development ecosystems, extensive software libraries, and standardized debugging tools, reducing time-to-market and engineering costs. CPLD development requires specialized expertise in digital design methodologies, potentially increasing initial development expenses but offering greater customization flexibility and intellectual property protection.

The scalability dimension introduces additional cost-performance considerations. DSP architectures provide straightforward performance scaling through clock frequency adjustments or multi-core implementations, while CPLDs offer scalability through logic density increases and distributed processing architectures. Each approach presents distinct cost implications depending on application requirements and production volumes.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!