Developing Analog-Memristor Platforms for Scalable Networks

APR 17, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Analog-Memristor Platform Development Background and Objectives

The evolution of computing architectures has reached a critical juncture where traditional von Neumann systems face fundamental limitations in addressing the exponential growth of data processing demands. The physical separation between memory and processing units creates bottlenecks that severely constrain performance and energy efficiency, particularly in applications requiring massive parallel computations such as artificial intelligence, machine learning, and real-time data analytics.

Memristive devices have emerged as a revolutionary solution to these challenges, offering the unique capability to perform both memory storage and computation within the same physical structure. These devices exhibit variable resistance states that can be modulated and retained, enabling in-memory computing paradigms that fundamentally eliminate the traditional memory-processor bottleneck. The analog nature of memristors provides additional advantages by supporting continuous resistance states rather than discrete digital values.

The development of analog-memristor platforms represents a paradigm shift toward neuromorphic computing architectures that mimic the efficiency and adaptability of biological neural networks. Unlike digital implementations, analog memristor systems can process information in a massively parallel manner while consuming significantly less power, making them ideal candidates for edge computing applications and large-scale network deployments.

Current technological trends indicate an urgent need for scalable computing solutions that can handle the increasing complexity of interconnected systems, Internet of Things deployments, and distributed processing networks. Traditional scaling approaches based on Moore's Law are approaching physical limits, necessitating alternative computing paradigms that can deliver exponential improvements in performance per watt.

The primary objective of developing analog-memristor platforms focuses on creating scalable network architectures capable of adaptive learning, real-time processing, and energy-efficient operation. These platforms aim to integrate seamlessly into existing infrastructure while providing unprecedented computational capabilities for emerging applications including autonomous systems, smart cities, and advanced robotics.

Key technical goals encompass achieving high-density integration, ensuring reliable analog operation across varying environmental conditions, and establishing standardized interfaces for network connectivity. The development process must address critical challenges including device variability, long-term stability, and the creation of robust programming algorithms that can effectively utilize the analog properties of memristive elements.

Memristive devices have emerged as a revolutionary solution to these challenges, offering the unique capability to perform both memory storage and computation within the same physical structure. These devices exhibit variable resistance states that can be modulated and retained, enabling in-memory computing paradigms that fundamentally eliminate the traditional memory-processor bottleneck. The analog nature of memristors provides additional advantages by supporting continuous resistance states rather than discrete digital values.

The development of analog-memristor platforms represents a paradigm shift toward neuromorphic computing architectures that mimic the efficiency and adaptability of biological neural networks. Unlike digital implementations, analog memristor systems can process information in a massively parallel manner while consuming significantly less power, making them ideal candidates for edge computing applications and large-scale network deployments.

Current technological trends indicate an urgent need for scalable computing solutions that can handle the increasing complexity of interconnected systems, Internet of Things deployments, and distributed processing networks. Traditional scaling approaches based on Moore's Law are approaching physical limits, necessitating alternative computing paradigms that can deliver exponential improvements in performance per watt.

The primary objective of developing analog-memristor platforms focuses on creating scalable network architectures capable of adaptive learning, real-time processing, and energy-efficient operation. These platforms aim to integrate seamlessly into existing infrastructure while providing unprecedented computational capabilities for emerging applications including autonomous systems, smart cities, and advanced robotics.

Key technical goals encompass achieving high-density integration, ensuring reliable analog operation across varying environmental conditions, and establishing standardized interfaces for network connectivity. The development process must address critical challenges including device variability, long-term stability, and the creation of robust programming algorithms that can effectively utilize the analog properties of memristive elements.

Market Demand for Scalable Neuromorphic Computing Solutions

The global neuromorphic computing market is experiencing unprecedented growth driven by the increasing demand for energy-efficient artificial intelligence solutions. Traditional von Neumann architectures face significant limitations in handling the massive parallel processing requirements of modern AI applications, creating substantial market opportunities for brain-inspired computing paradigms. Analog-memristor platforms represent a particularly promising segment within this landscape, offering the potential to revolutionize how neural networks are implemented in hardware.

Enterprise applications constitute the largest demand segment for scalable neuromorphic computing solutions. Data centers and cloud computing providers are actively seeking alternatives to conventional GPU-based AI accelerators due to escalating power consumption costs and thermal management challenges. The ability of analog-memristor networks to perform in-memory computing with dramatically reduced energy requirements addresses these critical pain points, making them highly attractive for large-scale deployment scenarios.

Edge computing applications represent another rapidly expanding market segment driving demand for neuromorphic solutions. Internet of Things devices, autonomous vehicles, and mobile computing platforms require AI processing capabilities within strict power and size constraints. Analog-memristor platforms offer the unique advantage of combining high computational density with ultra-low power operation, enabling sophisticated AI functionality in resource-constrained environments where traditional digital processors prove inadequate.

The automotive industry has emerged as a significant demand driver, particularly for advanced driver assistance systems and autonomous vehicle applications. Real-time sensor fusion, object recognition, and decision-making processes require massive parallel processing capabilities that align well with the inherent characteristics of memristive neural networks. The industry's emphasis on functional safety and reliability creates additional requirements for robust, scalable neuromorphic computing platforms.

Healthcare and biomedical applications represent an emerging but rapidly growing market segment. Brain-computer interfaces, neural prosthetics, and real-time medical imaging analysis require computing architectures that can efficiently process complex neural signals and patterns. The biological similarity between memristive devices and synaptic behavior makes analog-memristor platforms particularly well-suited for these applications, driving increasing interest from medical device manufacturers and research institutions.

Defense and aerospace sectors are also contributing to market demand, seeking neuromorphic solutions for autonomous systems, signal processing, and adaptive control applications. The ability to operate reliably in harsh environments while maintaining low power consumption makes analog-memristor platforms attractive for military and space applications where traditional computing systems may prove inadequate.

Enterprise applications constitute the largest demand segment for scalable neuromorphic computing solutions. Data centers and cloud computing providers are actively seeking alternatives to conventional GPU-based AI accelerators due to escalating power consumption costs and thermal management challenges. The ability of analog-memristor networks to perform in-memory computing with dramatically reduced energy requirements addresses these critical pain points, making them highly attractive for large-scale deployment scenarios.

Edge computing applications represent another rapidly expanding market segment driving demand for neuromorphic solutions. Internet of Things devices, autonomous vehicles, and mobile computing platforms require AI processing capabilities within strict power and size constraints. Analog-memristor platforms offer the unique advantage of combining high computational density with ultra-low power operation, enabling sophisticated AI functionality in resource-constrained environments where traditional digital processors prove inadequate.

The automotive industry has emerged as a significant demand driver, particularly for advanced driver assistance systems and autonomous vehicle applications. Real-time sensor fusion, object recognition, and decision-making processes require massive parallel processing capabilities that align well with the inherent characteristics of memristive neural networks. The industry's emphasis on functional safety and reliability creates additional requirements for robust, scalable neuromorphic computing platforms.

Healthcare and biomedical applications represent an emerging but rapidly growing market segment. Brain-computer interfaces, neural prosthetics, and real-time medical imaging analysis require computing architectures that can efficiently process complex neural signals and patterns. The biological similarity between memristive devices and synaptic behavior makes analog-memristor platforms particularly well-suited for these applications, driving increasing interest from medical device manufacturers and research institutions.

Defense and aerospace sectors are also contributing to market demand, seeking neuromorphic solutions for autonomous systems, signal processing, and adaptive control applications. The ability to operate reliably in harsh environments while maintaining low power consumption makes analog-memristor platforms attractive for military and space applications where traditional computing systems may prove inadequate.

Current State and Challenges of Memristor-Based Analog Platforms

Memristor-based analog platforms have emerged as promising solutions for neuromorphic computing and artificial intelligence applications, yet their current development status reveals significant technological and implementation challenges. The field has progressed from proof-of-concept demonstrations to prototype systems, but scalability remains a fundamental bottleneck limiting widespread adoption.

Current memristor technologies primarily utilize metal oxide materials such as titanium dioxide, hafnium oxide, and tantalum oxide, which exhibit variable resistance properties essential for analog computation. However, these materials suffer from device-to-device variability, with resistance variations often exceeding 20-30% across fabricated arrays. This variability severely impacts the precision required for analog neural network implementations, where weight accuracy directly correlates with computational performance.

Manufacturing consistency represents another critical challenge facing the industry. Existing fabrication processes struggle to maintain uniform switching characteristics across large-scale arrays, particularly when scaling beyond 1000x1000 crossbar configurations. The lack of standardized fabrication protocols has resulted in inconsistent performance metrics across different research institutions and commercial entities, hindering technology transfer and commercialization efforts.

Endurance limitations pose significant operational constraints for memristor-based platforms. Current devices typically demonstrate switching cycles ranging from 10^6 to 10^9 operations before degradation, which falls short of requirements for continuous learning applications. Additionally, retention characteristics vary substantially with temperature and environmental conditions, creating reliability concerns for deployment in diverse operational environments.

Integration challenges with conventional CMOS technology further complicate platform development. The peripheral circuitry required for memristor array control often occupies substantial silicon area, reducing the density advantages that memristors theoretically provide. Current selector devices used to prevent sneak path currents introduce additional complexity and power consumption, particularly in large-scale implementations.

Power efficiency, while generally superior to digital alternatives, remains inconsistent across different operating modes. Write operations typically consume significantly more energy than read operations, creating optimization challenges for training versus inference scenarios. The development of low-power programming schemes continues to be an active area of research with limited standardized solutions.

Geographically, memristor research concentrates primarily in the United States, South Korea, and China, with limited industrial-scale manufacturing capabilities currently available. This concentration creates supply chain vulnerabilities and limits global accessibility to advanced memristor technologies for platform development initiatives.

Current memristor technologies primarily utilize metal oxide materials such as titanium dioxide, hafnium oxide, and tantalum oxide, which exhibit variable resistance properties essential for analog computation. However, these materials suffer from device-to-device variability, with resistance variations often exceeding 20-30% across fabricated arrays. This variability severely impacts the precision required for analog neural network implementations, where weight accuracy directly correlates with computational performance.

Manufacturing consistency represents another critical challenge facing the industry. Existing fabrication processes struggle to maintain uniform switching characteristics across large-scale arrays, particularly when scaling beyond 1000x1000 crossbar configurations. The lack of standardized fabrication protocols has resulted in inconsistent performance metrics across different research institutions and commercial entities, hindering technology transfer and commercialization efforts.

Endurance limitations pose significant operational constraints for memristor-based platforms. Current devices typically demonstrate switching cycles ranging from 10^6 to 10^9 operations before degradation, which falls short of requirements for continuous learning applications. Additionally, retention characteristics vary substantially with temperature and environmental conditions, creating reliability concerns for deployment in diverse operational environments.

Integration challenges with conventional CMOS technology further complicate platform development. The peripheral circuitry required for memristor array control often occupies substantial silicon area, reducing the density advantages that memristors theoretically provide. Current selector devices used to prevent sneak path currents introduce additional complexity and power consumption, particularly in large-scale implementations.

Power efficiency, while generally superior to digital alternatives, remains inconsistent across different operating modes. Write operations typically consume significantly more energy than read operations, creating optimization challenges for training versus inference scenarios. The development of low-power programming schemes continues to be an active area of research with limited standardized solutions.

Geographically, memristor research concentrates primarily in the United States, South Korea, and China, with limited industrial-scale manufacturing capabilities currently available. This concentration creates supply chain vulnerabilities and limits global accessibility to advanced memristor technologies for platform development initiatives.

Existing Analog-Memristor Platform Architectures

01 Crossbar array architectures for memristor scalability

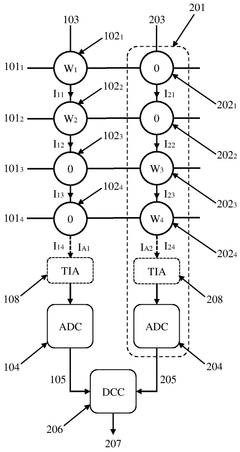

Crossbar array architectures enable high-density integration of memristor devices by organizing them in grid-like structures with perpendicular word lines and bit lines. This configuration allows for efficient addressing and access to individual memristor cells while minimizing the footprint. The architecture supports large-scale integration by reducing the number of required connections and enabling parallel operations across multiple cells, which is essential for building scalable analog computing platforms.- Crossbar array architectures for memristor scalability: Crossbar array architectures enable high-density integration of memristor devices by organizing them in grid-like structures with perpendicular word lines and bit lines. This configuration allows for efficient addressing and access to individual memristor cells while minimizing the footprint. The architecture supports large-scale integration by reducing the number of required connections and enabling parallel operations across multiple devices, making it suitable for analog computing applications requiring massive parallelism.

- Multi-layer stacking techniques for three-dimensional memristor integration: Three-dimensional stacking approaches enable vertical integration of multiple memristor layers to increase device density beyond planar limitations. These techniques involve fabricating memristor arrays in multiple vertical layers with interlayer connections, allowing for significant increases in storage capacity and computational throughput within the same chip area. The vertical architecture addresses scalability challenges by expanding in the third dimension while maintaining compatibility with existing fabrication processes.

- Selector devices and access transistors for reducing sneak path currents: Integration of selector devices or access transistors with memristor cells addresses the sneak path problem that becomes critical in large-scale arrays. These components provide nonlinear current-voltage characteristics or switching functionality to isolate unselected cells during read and write operations. By minimizing parasitic currents through unintended paths, these solutions enable larger array sizes while maintaining signal integrity and reducing power consumption in analog memristor platforms.

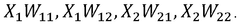

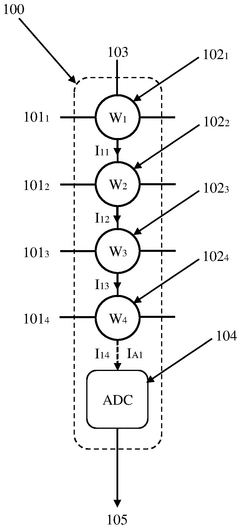

- Peripheral circuit design for large-scale memristor array control: Specialized peripheral circuitry including row and column decoders, sense amplifiers, and voltage drivers are essential for controlling and reading large memristor arrays. These circuits must handle the unique requirements of analog memristor operations, including precise voltage control for programming and accurate current sensing for reading resistance states. Efficient peripheral circuit design minimizes area overhead while providing the necessary functionality to scale memristor platforms to commercially viable sizes.

- Material engineering and device optimization for uniform switching characteristics: Achieving uniform and reliable switching behavior across large arrays requires careful material selection and device structure optimization. This includes engineering the active switching layer composition, electrode materials, and interface properties to ensure consistent resistance switching characteristics with minimal device-to-device variation. Improved uniformity enables predictable analog operations across scaled platforms and reduces the need for extensive calibration or compensation circuits in large arrays.

02 Multi-layer stacking techniques for three-dimensional memristor integration

Three-dimensional stacking approaches enable vertical integration of multiple memristor layers to increase device density without expanding the horizontal footprint. This technique involves fabricating memristor arrays in multiple tiers with vertical interconnects, allowing for significantly higher storage capacity and computational capability per unit area. The multi-layer approach addresses scalability challenges by utilizing the third dimension and enables more compact analog computing platforms with enhanced performance characteristics.Expand Specific Solutions03 Selector devices and access transistors for reducing sneak path currents

Integration of selector devices or access transistors with memristor cells helps mitigate sneak path currents that can interfere with accurate reading and writing operations in large arrays. These components act as switches to isolate individual memristor cells during operation, preventing unintended current flow through neighboring cells. This approach is critical for maintaining signal integrity and enabling reliable operation in scaled-up memristor platforms, particularly in analog applications requiring precise resistance state control.Expand Specific Solutions04 Peripheral circuit integration and interface design for analog operations

Efficient peripheral circuitry including sense amplifiers, write drivers, and analog-to-digital converters is essential for interfacing with memristor arrays in analog computing applications. These circuits must be designed to handle the continuous range of resistance states characteristic of analog memristors while maintaining low power consumption and high speed. Proper integration of peripheral circuits with the memristor array enables scalable platforms that can perform complex analog computations such as vector-matrix multiplication and neural network operations.Expand Specific Solutions05 Programming and control schemes for large-scale memristor arrays

Advanced programming algorithms and control schemes are necessary to manage the operation of large-scale memristor arrays efficiently. These include techniques for precise resistance tuning, compensation for device variability, and methods for parallel programming of multiple cells. Effective control schemes must address challenges such as voltage drops across long interconnects, temperature variations, and device-to-device variations to ensure uniform performance across the entire array. Such schemes are fundamental to achieving practical scalability in analog memristor platforms.Expand Specific Solutions

Key Players in Memristor and Neuromorphic Computing Industry

The analog-memristor platform technology for scalable networks represents an emerging field in the early development stage, with significant growth potential driven by increasing demand for neuromorphic computing and edge AI applications. The market remains nascent but shows promise for exponential expansion as AI workloads require more efficient, brain-inspired computing architectures. Technology maturity varies significantly across players, with established semiconductor giants like Intel, IBM, Apple, and Qualcomm leveraging their extensive R&D capabilities and manufacturing infrastructure to advance memristor integration into existing platforms. Specialized companies such as Polyn Technology and Unifabrix are pioneering novel approaches with neuromorphic analog processing and memory fabric solutions respectively. Academic institutions including University of California, Peking University, and Xi'an Jiaotong University contribute fundamental research breakthroughs, while companies like Synaptics and Cirrus Logic focus on practical implementations for consumer electronics, creating a diverse ecosystem spanning from basic research to commercial deployment.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive analog memristor platforms focusing on phase-change memory (PCM) and resistive RAM technologies for neuromorphic computing applications. Their approach integrates crossbar arrays with CMOS circuits to enable in-memory computing capabilities. The platform supports synaptic weight storage and neural network acceleration through analog computation, achieving significant energy efficiency improvements over traditional digital approaches. IBM's memristor technology demonstrates multi-level cell programming with precise conductance control, enabling scalable neural network implementations for AI workloads.

Strengths: Mature fabrication processes, strong research foundation, enterprise-grade reliability. Weaknesses: Higher manufacturing costs, limited commercial availability of memristor products.

Intel Corp.

Technical Solution: Intel's analog memristor platform leverages their advanced semiconductor manufacturing capabilities to develop crossbar architectures for neuromorphic computing. Their solution integrates memristive devices with conventional CMOS technology, creating hybrid systems that can perform both storage and computation functions. The platform focuses on scalable network implementations through hierarchical memory architectures, supporting both training and inference operations. Intel's approach emphasizes compatibility with existing computing infrastructures while providing the benefits of analog computation for specific AI workloads.

Strengths: Advanced manufacturing capabilities, strong ecosystem integration, scalable production potential. Weaknesses: Early development stage, competition from specialized neuromorphic chip companies.

Core Patents in Scalable Memristor Network Design

In-memory computing crossbar and optimization method

PatentWO2024245532A1

Innovation

- A crossbar structure with a plurality of input and output lines and cross-point devices, where at least one column has a zero weight to mitigate noise variations, and analog-to-digital converters with adjustable resolution to reduce power consumption, allowing for optimal trade-offs between reliability and complexity.

Memristor structures with analog switching characteristics and method for fabricating the same

PatentPendingUS20250378318A1

Innovation

- A memristor structure based on a Ti/CrOx/TiOy/Cr junction is fabricated using a simple and non-hazardous process, exhibiting self-rectifying behavior, analog switching, and large hysteresis area, mimicking biological synapses.

Manufacturing Standards for Memristor Device Production

The establishment of comprehensive manufacturing standards for memristor device production represents a critical foundation for the successful deployment of analog-memristor platforms in scalable networks. Current industry practices reveal significant variations in fabrication processes, material specifications, and quality control measures across different manufacturers, creating substantial barriers to widespread adoption and system integration.

Material purity and composition standards constitute the primary concern in memristor manufacturing. The switching layer materials, typically metal oxides such as titanium dioxide, hafnium oxide, or tantalum oxide, require precise stoichiometric control and minimal contamination levels. Industry consensus suggests that impurity concentrations should not exceed 0.1% for critical dopants and 0.01% for metallic contaminants to ensure consistent switching behavior and device longevity.

Dimensional tolerances and geometric specifications demand rigorous standardization to enable reliable network scalability. Device thickness variations must be controlled within ±2% for the switching layer and ±5% for electrode layers. Cross-sectional area uniformity becomes particularly crucial for analog applications, where resistance variations directly impact computational accuracy. Standard specifications recommend maintaining area variations below ±3% across individual devices and ±5% across production batches.

Electrical characterization protocols require standardized testing methodologies to ensure device compatibility across different network architectures. Key parameters include switching threshold voltages, resistance ratio specifications, endurance cycling requirements, and retention characteristics. Industry standards propose minimum resistance ratios of 10:1 for digital applications and continuous analog resistance ranges spanning at least two orders of magnitude for neuromorphic computing applications.

Process control and environmental standards address fabrication consistency and reliability concerns. Temperature control during deposition and annealing processes must maintain variations within ±2°C, while ambient humidity levels should remain below 1% during critical manufacturing steps. Cleanroom classifications of ISO Class 4 or better are recommended for device fabrication areas to minimize particulate contamination.

Quality assurance frameworks encompass statistical sampling protocols, failure analysis procedures, and traceability requirements. Manufacturing standards mandate 100% electrical testing for critical parameters, with statistical sampling for extended characterization. Batch documentation must include complete process histories, material certifications, and performance distributions to enable effective yield optimization and reliability prediction for large-scale network deployments.

Material purity and composition standards constitute the primary concern in memristor manufacturing. The switching layer materials, typically metal oxides such as titanium dioxide, hafnium oxide, or tantalum oxide, require precise stoichiometric control and minimal contamination levels. Industry consensus suggests that impurity concentrations should not exceed 0.1% for critical dopants and 0.01% for metallic contaminants to ensure consistent switching behavior and device longevity.

Dimensional tolerances and geometric specifications demand rigorous standardization to enable reliable network scalability. Device thickness variations must be controlled within ±2% for the switching layer and ±5% for electrode layers. Cross-sectional area uniformity becomes particularly crucial for analog applications, where resistance variations directly impact computational accuracy. Standard specifications recommend maintaining area variations below ±3% across individual devices and ±5% across production batches.

Electrical characterization protocols require standardized testing methodologies to ensure device compatibility across different network architectures. Key parameters include switching threshold voltages, resistance ratio specifications, endurance cycling requirements, and retention characteristics. Industry standards propose minimum resistance ratios of 10:1 for digital applications and continuous analog resistance ranges spanning at least two orders of magnitude for neuromorphic computing applications.

Process control and environmental standards address fabrication consistency and reliability concerns. Temperature control during deposition and annealing processes must maintain variations within ±2°C, while ambient humidity levels should remain below 1% during critical manufacturing steps. Cleanroom classifications of ISO Class 4 or better are recommended for device fabrication areas to minimize particulate contamination.

Quality assurance frameworks encompass statistical sampling protocols, failure analysis procedures, and traceability requirements. Manufacturing standards mandate 100% electrical testing for critical parameters, with statistical sampling for extended characterization. Batch documentation must include complete process histories, material certifications, and performance distributions to enable effective yield optimization and reliability prediction for large-scale network deployments.

Energy Efficiency Considerations in Analog Computing Platforms

Energy efficiency represents a critical design consideration for analog-memristor platforms targeting scalable network applications. Unlike traditional digital computing architectures that rely on discrete voltage levels and frequent data movement between memory and processing units, analog memristor platforms offer inherent advantages through in-memory computing capabilities. These devices can perform multiply-accumulate operations directly within the memory array, significantly reducing the energy overhead associated with data transfer operations that typically dominate power consumption in conventional von Neumann architectures.

The energy efficiency of analog memristor platforms stems from their ability to exploit the physical properties of memristive devices for computation. When configured in crossbar arrays, memristors can execute matrix-vector multiplications through Ohm's law and Kirchhoff's current law, consuming energy proportional to the actual computation rather than maintaining constant power draw. This approach enables substantial energy savings, particularly for sparse network operations where many weights approach zero values, as the corresponding memristors contribute minimal current to the overall power consumption.

Power management strategies for scalable analog memristor networks must address several key challenges. Dynamic range limitations inherent to analog devices require careful consideration of signal scaling and amplification, which can introduce additional energy overhead. Peripheral circuitry, including analog-to-digital converters, sense amplifiers, and voltage drivers, often dominates the total system power consumption. Advanced circuit techniques such as time-multiplexed sensing, shared peripheral resources, and adaptive voltage scaling can significantly improve overall energy efficiency while maintaining computational accuracy.

Thermal management emerges as another crucial factor affecting energy efficiency in large-scale analog memristor platforms. Heat generation from resistive switching operations and peripheral circuits can lead to temperature-dependent variations in device characteristics, potentially requiring additional cooling infrastructure or compensation circuits. Implementing hierarchical network architectures with distributed processing capabilities can help mitigate thermal hotspots while optimizing energy distribution across the platform.

The scalability of energy-efficient analog memristor platforms depends on architectural innovations that minimize parasitic effects and optimize signal integrity. Techniques such as differential signaling, local feedback mechanisms, and adaptive calibration systems can maintain energy efficiency as network sizes increase, ensuring that the fundamental advantages of analog in-memory computing are preserved at scale.

The energy efficiency of analog memristor platforms stems from their ability to exploit the physical properties of memristive devices for computation. When configured in crossbar arrays, memristors can execute matrix-vector multiplications through Ohm's law and Kirchhoff's current law, consuming energy proportional to the actual computation rather than maintaining constant power draw. This approach enables substantial energy savings, particularly for sparse network operations where many weights approach zero values, as the corresponding memristors contribute minimal current to the overall power consumption.

Power management strategies for scalable analog memristor networks must address several key challenges. Dynamic range limitations inherent to analog devices require careful consideration of signal scaling and amplification, which can introduce additional energy overhead. Peripheral circuitry, including analog-to-digital converters, sense amplifiers, and voltage drivers, often dominates the total system power consumption. Advanced circuit techniques such as time-multiplexed sensing, shared peripheral resources, and adaptive voltage scaling can significantly improve overall energy efficiency while maintaining computational accuracy.

Thermal management emerges as another crucial factor affecting energy efficiency in large-scale analog memristor platforms. Heat generation from resistive switching operations and peripheral circuits can lead to temperature-dependent variations in device characteristics, potentially requiring additional cooling infrastructure or compensation circuits. Implementing hierarchical network architectures with distributed processing capabilities can help mitigate thermal hotspots while optimizing energy distribution across the platform.

The scalability of energy-efficient analog memristor platforms depends on architectural innovations that minimize parasitic effects and optimize signal integrity. Techniques such as differential signaling, local feedback mechanisms, and adaptive calibration systems can maintain energy efficiency as network sizes increase, ensuring that the fundamental advantages of analog in-memory computing are preserved at scale.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!