Innovations in Variable Memristor State Determination

APR 17, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Memristor Technology Background and Research Objectives

Memristor technology represents a paradigm shift in non-volatile memory and neuromorphic computing, emerging as the fourth fundamental passive circuit element alongside resistors, capacitors, and inductors. First theorized by Leon Chua in 1971 and physically realized by HP Labs in 2008, memristors exhibit resistance that changes based on the history of applied voltage and current, creating a memory effect that persists even when power is removed.

The evolution of memristor technology has progressed through distinct phases, beginning with theoretical foundations in the 1970s, followed by material science breakthroughs in the 2000s, and advancing toward practical applications in the 2010s. Current development focuses on addressing fundamental challenges in state determination and switching reliability, which are critical for commercial viability.

Variable memristor state determination has emerged as a pivotal research area due to the inherent complexity of memristive switching mechanisms. Unlike traditional binary memory devices, memristors can exhibit multiple intermediate resistance states, enabling multi-level data storage and analog computing capabilities. However, accurately determining and controlling these variable states remains technically challenging due to factors including device-to-device variability, temporal drift, and environmental sensitivity.

The primary technical objectives driving current research include developing robust state detection methodologies that can reliably distinguish between multiple resistance levels under varying operational conditions. This encompasses creating sensing circuits with enhanced noise immunity, implementing error correction algorithms specifically designed for memristive systems, and establishing standardized characterization protocols for multi-state devices.

Advanced state determination techniques are essential for unlocking memristor applications in artificial neural networks, where precise synaptic weight representation directly impacts learning accuracy and computational efficiency. The ability to program and read multiple distinct resistance states with high fidelity enables memristors to emulate biological synapses more effectively than traditional digital approaches.

Research objectives also encompass developing predictive models for state evolution over time, addressing the challenge of resistance drift that can compromise data integrity in long-term storage applications. This includes investigating the underlying physical mechanisms governing ionic migration and filament formation in various memristive materials, from metal oxides to organic compounds.

The convergence of materials science, circuit design, and algorithmic innovation defines the current trajectory of memristor state determination research, positioning this technology as a cornerstone for next-generation computing architectures that blur the boundaries between memory and processing elements.

The evolution of memristor technology has progressed through distinct phases, beginning with theoretical foundations in the 1970s, followed by material science breakthroughs in the 2000s, and advancing toward practical applications in the 2010s. Current development focuses on addressing fundamental challenges in state determination and switching reliability, which are critical for commercial viability.

Variable memristor state determination has emerged as a pivotal research area due to the inherent complexity of memristive switching mechanisms. Unlike traditional binary memory devices, memristors can exhibit multiple intermediate resistance states, enabling multi-level data storage and analog computing capabilities. However, accurately determining and controlling these variable states remains technically challenging due to factors including device-to-device variability, temporal drift, and environmental sensitivity.

The primary technical objectives driving current research include developing robust state detection methodologies that can reliably distinguish between multiple resistance levels under varying operational conditions. This encompasses creating sensing circuits with enhanced noise immunity, implementing error correction algorithms specifically designed for memristive systems, and establishing standardized characterization protocols for multi-state devices.

Advanced state determination techniques are essential for unlocking memristor applications in artificial neural networks, where precise synaptic weight representation directly impacts learning accuracy and computational efficiency. The ability to program and read multiple distinct resistance states with high fidelity enables memristors to emulate biological synapses more effectively than traditional digital approaches.

Research objectives also encompass developing predictive models for state evolution over time, addressing the challenge of resistance drift that can compromise data integrity in long-term storage applications. This includes investigating the underlying physical mechanisms governing ionic migration and filament formation in various memristive materials, from metal oxides to organic compounds.

The convergence of materials science, circuit design, and algorithmic innovation defines the current trajectory of memristor state determination research, positioning this technology as a cornerstone for next-generation computing architectures that blur the boundaries between memory and processing elements.

Market Demand for Advanced Memory and Computing Solutions

The global memory and computing market is experiencing unprecedented growth driven by the exponential increase in data generation and the rising demand for high-performance computing solutions. Traditional memory technologies face significant limitations in meeting the requirements of emerging applications such as artificial intelligence, machine learning, edge computing, and Internet of Things devices. These applications demand memory solutions that can provide faster access speeds, lower power consumption, higher density, and enhanced reliability.

Memristor technology represents a paradigm shift in memory and computing architectures, offering unique advantages that address current market pain points. The ability to store multiple states in a single device, combined with non-volatile characteristics and in-memory computing capabilities, positions memristors as a critical technology for next-generation computing systems. Variable memristor state determination innovations are particularly crucial as they enable more precise control over device behavior, leading to improved reliability and expanded functionality.

The neuromorphic computing market is emerging as a significant driver for advanced memristor solutions. Brain-inspired computing architectures require memory devices that can mimic synaptic behavior, where variable resistance states represent different synaptic weights. This application demands sophisticated state determination mechanisms to ensure accurate neural network operations and learning processes.

Data centers and cloud computing infrastructure represent another substantial market opportunity. The growing emphasis on energy efficiency and computational density in data centers creates strong demand for memory technologies that can reduce power consumption while maintaining high performance. Variable memristor state determination enables more efficient data processing and storage, directly addressing these market needs.

The automotive industry's transition toward autonomous vehicles and advanced driver assistance systems creates additional market demand. These applications require memory solutions capable of operating reliably in harsh environments while providing real-time processing capabilities. Memristors with advanced state determination mechanisms can meet these stringent requirements while offering the flexibility needed for adaptive automotive systems.

Mobile and edge computing devices continue to drive demand for low-power, high-density memory solutions. The proliferation of smart devices and the push toward edge AI processing require memory technologies that can deliver superior performance within strict power and size constraints. Variable memristor state determination innovations enable more efficient utilization of these devices in resource-constrained environments.

Memristor technology represents a paradigm shift in memory and computing architectures, offering unique advantages that address current market pain points. The ability to store multiple states in a single device, combined with non-volatile characteristics and in-memory computing capabilities, positions memristors as a critical technology for next-generation computing systems. Variable memristor state determination innovations are particularly crucial as they enable more precise control over device behavior, leading to improved reliability and expanded functionality.

The neuromorphic computing market is emerging as a significant driver for advanced memristor solutions. Brain-inspired computing architectures require memory devices that can mimic synaptic behavior, where variable resistance states represent different synaptic weights. This application demands sophisticated state determination mechanisms to ensure accurate neural network operations and learning processes.

Data centers and cloud computing infrastructure represent another substantial market opportunity. The growing emphasis on energy efficiency and computational density in data centers creates strong demand for memory technologies that can reduce power consumption while maintaining high performance. Variable memristor state determination enables more efficient data processing and storage, directly addressing these market needs.

The automotive industry's transition toward autonomous vehicles and advanced driver assistance systems creates additional market demand. These applications require memory solutions capable of operating reliably in harsh environments while providing real-time processing capabilities. Memristors with advanced state determination mechanisms can meet these stringent requirements while offering the flexibility needed for adaptive automotive systems.

Mobile and edge computing devices continue to drive demand for low-power, high-density memory solutions. The proliferation of smart devices and the push toward edge AI processing require memory technologies that can deliver superior performance within strict power and size constraints. Variable memristor state determination innovations enable more efficient utilization of these devices in resource-constrained environments.

Current Memristor State Detection Challenges and Limitations

Current memristor state detection faces significant challenges that limit the widespread adoption and reliability of memristive devices in practical applications. The fundamental difficulty lies in accurately distinguishing between multiple resistance states, particularly when these states are closely spaced or when environmental factors introduce noise and variability.

One of the primary limitations is the inherent variability in memristor resistance values. Manufacturing processes introduce device-to-device variations that can cause overlapping resistance distributions between different programmed states. This variability makes it challenging to establish reliable threshold values for state discrimination, especially in multi-level cell applications where precise state differentiation is crucial for data integrity.

Temperature dependency presents another critical challenge in memristor state detection. Resistance values can drift significantly with temperature fluctuations, causing programmed states to shift beyond their intended ranges. This thermal sensitivity requires complex compensation mechanisms and limits the operational temperature range of memristive systems, particularly in automotive and industrial applications where wide temperature variations are common.

Read disturb phenomena further complicate state detection processes. Repeated read operations can gradually alter the resistance state of memristors, leading to cumulative errors over time. This issue is particularly problematic in applications requiring frequent state verification or in systems with high read frequencies, where the accumulated disturbance can eventually cause state misidentification.

Aging and endurance limitations introduce long-term reliability concerns for state detection. As memristors undergo repeated switching cycles, their resistance characteristics gradually degrade, causing state boundaries to shift and detection margins to narrow. This degradation process is often non-uniform across different resistance levels, making it difficult to maintain consistent detection accuracy throughout the device lifetime.

The speed versus accuracy trade-off represents a fundamental constraint in current detection methodologies. Fast read operations may not allow sufficient time for resistance stabilization, leading to measurement errors, while slower, more accurate reads can significantly impact system performance. This limitation is particularly challenging in high-speed memory applications where rapid state determination is essential.

Parasitic effects from interconnects and peripheral circuitry introduce additional complexity to state detection. Wire resistance, capacitive coupling, and leakage currents can mask the true memristor resistance, especially in large array configurations where these parasitic effects accumulate. These factors necessitate sophisticated compensation techniques and limit the scalability of memristive systems.

One of the primary limitations is the inherent variability in memristor resistance values. Manufacturing processes introduce device-to-device variations that can cause overlapping resistance distributions between different programmed states. This variability makes it challenging to establish reliable threshold values for state discrimination, especially in multi-level cell applications where precise state differentiation is crucial for data integrity.

Temperature dependency presents another critical challenge in memristor state detection. Resistance values can drift significantly with temperature fluctuations, causing programmed states to shift beyond their intended ranges. This thermal sensitivity requires complex compensation mechanisms and limits the operational temperature range of memristive systems, particularly in automotive and industrial applications where wide temperature variations are common.

Read disturb phenomena further complicate state detection processes. Repeated read operations can gradually alter the resistance state of memristors, leading to cumulative errors over time. This issue is particularly problematic in applications requiring frequent state verification or in systems with high read frequencies, where the accumulated disturbance can eventually cause state misidentification.

Aging and endurance limitations introduce long-term reliability concerns for state detection. As memristors undergo repeated switching cycles, their resistance characteristics gradually degrade, causing state boundaries to shift and detection margins to narrow. This degradation process is often non-uniform across different resistance levels, making it difficult to maintain consistent detection accuracy throughout the device lifetime.

The speed versus accuracy trade-off represents a fundamental constraint in current detection methodologies. Fast read operations may not allow sufficient time for resistance stabilization, leading to measurement errors, while slower, more accurate reads can significantly impact system performance. This limitation is particularly challenging in high-speed memory applications where rapid state determination is essential.

Parasitic effects from interconnects and peripheral circuitry introduce additional complexity to state detection. Wire resistance, capacitive coupling, and leakage currents can mask the true memristor resistance, especially in large array configurations where these parasitic effects accumulate. These factors necessitate sophisticated compensation techniques and limit the scalability of memristive systems.

Existing Variable Memristor State Detection Solutions

01 Voltage-based memristor state sensing techniques

Methods for determining memristor states by applying specific voltage pulses or voltage sweeps and measuring the resulting current or resistance. These techniques involve applying read voltages that are lower than the switching threshold to avoid disturbing the stored state. The voltage-based sensing can include differential voltage measurements and voltage divider configurations to accurately detect the resistance state of the memristor device.- Voltage-based memristor state sensing techniques: Methods for determining memristor states by applying specific voltage pulses or sweeps and measuring the resulting current or resistance. These techniques involve controlled voltage application to read the conductance state without disturbing the stored information. The sensing circuitry can differentiate between high and low resistance states by comparing measured values against reference thresholds.

- Current-based memristor state detection methods: Approaches that utilize current measurements to determine the resistance state of memristive devices. These methods involve applying a read current and measuring the voltage drop across the memristor element, or using current sensing amplifiers to detect the conductance level. The techniques enable non-destructive readout of stored data while maintaining state integrity.

- Multi-level state discrimination in memristive devices: Techniques for identifying and distinguishing between multiple intermediate resistance states in memristors beyond binary operation. These methods employ sophisticated sensing schemes with multiple reference levels or analog-to-digital conversion to accurately determine the precise conductance state. Such approaches enable higher density data storage by utilizing the analog nature of memristive switching.

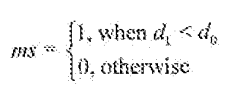

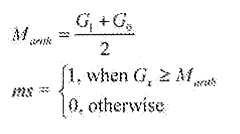

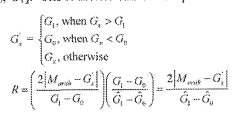

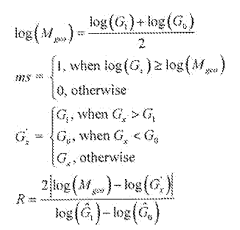

- Self-referencing and differential sensing architectures: Circuit configurations that use reference memristors or differential sensing to improve state determination accuracy. These architectures compare the target memristor against a reference element or complementary device to cancel common-mode variations and enhance read margin. The differential approach reduces sensitivity to process variations and environmental factors.

- Adaptive and iterative state verification methods: Advanced techniques that employ multiple read operations or adaptive algorithms to verify and confirm memristor states. These methods may use iterative sensing with adjustable parameters, error correction schemes, or machine learning algorithms to improve state determination reliability. The approaches are particularly useful for compensating drift effects and ensuring accurate readout over device lifetime.

02 Current-based memristor state detection methods

Approaches that utilize current measurements to determine the resistance state of memristors. These methods involve applying a sensing current through the memristor and measuring the voltage drop or comparing the current against reference values. Current-based detection can provide fast and reliable state determination while minimizing power consumption and avoiding unintended state changes during the read operation.Expand Specific Solutions03 Multi-level state discrimination in memristive devices

Techniques for identifying and distinguishing between multiple resistance states in memristors beyond simple binary states. These methods enable the detection of intermediate resistance levels, allowing for multi-bit storage per cell. The discrimination involves using multiple reference levels, adaptive sensing schemes, or iterative verification processes to accurately determine which of several possible states the memristor currently occupies.Expand Specific Solutions04 Self-referencing and differential sensing architectures

Circuit architectures that employ self-referencing or differential sensing to improve the accuracy and reliability of memristor state determination. These approaches compare the target memristor against a reference memristor or use differential amplification techniques to enhance signal margins. Such architectures can compensate for process variations, temperature effects, and aging, providing more robust state detection across different operating conditions.Expand Specific Solutions05 Adaptive and iterative state verification methods

Advanced techniques that use adaptive algorithms or iterative processes to verify and confirm memristor states. These methods may involve multiple read operations with varying parameters, feedback mechanisms to adjust sensing conditions, or machine learning approaches to improve state determination accuracy. Such techniques are particularly useful for handling device variability, drift over time, and ensuring reliable operation in large-scale memristor arrays.Expand Specific Solutions

Key Players in Memristor and Neuromorphic Computing Industry

The variable memristor state determination field represents an emerging technology sector in the early-to-mid development stage, with significant growth potential driven by next-generation memory applications. The market shows substantial promise as memristors offer advantages in neuromorphic computing and non-volatile memory systems. Technology maturity varies significantly across players, with established semiconductor giants like Samsung Electronics, Micron Technology, and IBM leading advanced development alongside specialized memory companies such as Everspin Technologies and KIOXIA Corp. Academic institutions including MIT, Peking University, and various Chinese universities contribute fundamental research, while companies like Hewlett Packard Enterprise and Infineon Technologies focus on practical implementations. The competitive landscape reflects a mix of mature corporations with extensive R&D capabilities and emerging players, indicating the technology's transition from research phase toward commercial viability, though widespread adoption remains several years away.

Hewlett Packard Enterprise Development LP

Technical Solution: HPE has developed advanced memristor crossbar arrays with integrated sensing circuits for precise state determination. Their approach utilizes adaptive voltage sensing techniques combined with machine learning algorithms to accurately distinguish between multiple resistance states in memristive devices. The company's technology incorporates real-time calibration mechanisms that compensate for device variations and environmental factors, enabling reliable multi-level cell operation. Their memristor state detection system features low-power sensing amplifiers and digital signal processing units that can identify up to 16 distinct resistance levels with high accuracy, making it suitable for high-density neuromorphic computing applications and non-volatile memory systems.

Strengths: Pioneer in memristor research with extensive patent portfolio and proven crossbar architecture. Weaknesses: Limited commercial deployment and high manufacturing complexity for large-scale production.

SanDisk Technologies LLC

Technical Solution: SanDisk has developed innovative sensing methodologies for memristive storage devices, focusing on multi-level cell detection in ReRAM arrays. Their technology employs advanced read circuits with temperature compensation and adaptive reference generation to accurately determine variable memristor states. The company's approach includes sophisticated error correction algorithms and machine learning-based state classification techniques that can handle device-to-device variations and endurance-related drift. Their sensing system integrates on-chip calibration circuits and uses statistical analysis methods to optimize read margins and improve data retention reliability in high-density memristive memory arrays.

Strengths: Strong expertise in non-volatile memory technologies and established manufacturing capabilities. Weaknesses: Primarily focused on storage applications rather than neuromorphic computing, limited research in emerging memristor materials.

Core Patents in Memristor State Sensing Innovations

Determining a state of memristors in a crossbar array

PatentWO2016137446A1

Innovation

- A method and system that apply a bias voltage to a target row line in a crossbar array, increasing it to a state voltage to generate a state current, which is compared to a reference current to determine the resistance state of the memristor, while reducing sneak currents through the use of selectors with threshold voltages and fractional voltages on non-target lines.

Memory element and method for determining the data state of a memory element

PatentWO2012015438A1

Innovation

- A method involving measuring the current through a memristive memory element with an interrogation voltage, setting it to both binary data states '0' and '1', and computing the most likely data state based on the measured conductances, along with calculating a reliability metric to account for physical state drift and inconsistencies.

Fabrication Standards for Memristor Device Manufacturing

The establishment of robust fabrication standards for memristor device manufacturing represents a critical foundation for advancing innovations in variable memristor state determination. Current manufacturing processes face significant challenges in achieving consistent device performance, particularly in controlling the switching characteristics that enable precise state determination. The lack of standardized fabrication protocols has resulted in substantial device-to-device variations, limiting the reliability of state detection mechanisms.

Material selection and preparation constitute fundamental aspects of memristor fabrication standards. The choice of switching materials, including metal oxides such as TiO2, HfO2, and Ta2O5, directly impacts the device's ability to maintain distinct resistance states. Standardized material purity requirements, typically exceeding 99.9%, and controlled grain size distributions are essential for reproducible switching behavior. The substrate preparation process must also adhere to strict cleanliness standards, with surface roughness maintained below 0.5 nm RMS to ensure uniform film deposition.

Deposition techniques require precise parameter control to achieve consistent memristor performance. Physical vapor deposition and atomic layer deposition have emerged as preferred methods, with standardized chamber conditions including base pressure below 10^-7 Torr and controlled deposition rates. Temperature uniformity across the substrate, maintained within ±2°C, ensures homogeneous film properties that directly influence state determination accuracy.

Electrode fabrication standards play a crucial role in memristor device reliability. The interface between electrodes and switching materials significantly affects the formation and dissolution of conductive filaments. Standardized electrode materials, such as platinum or titanium nitride, with controlled thickness variations below 5%, ensure consistent electric field distributions during switching operations.

Quality control measures throughout the fabrication process are essential for maintaining device uniformity. In-line monitoring of film thickness, composition, and electrical properties enables real-time process adjustments. Statistical process control methods, including control charts and capability studies, help maintain fabrication parameters within specified tolerances, directly supporting the development of reliable state determination techniques.

Environmental control during manufacturing represents another critical standard. Cleanroom conditions with particle counts below Class 100 specifications prevent contamination that could create unwanted switching sites. Humidity control below 45% relative humidity and temperature stability within ±1°C minimize process variations that affect device performance consistency.

Material selection and preparation constitute fundamental aspects of memristor fabrication standards. The choice of switching materials, including metal oxides such as TiO2, HfO2, and Ta2O5, directly impacts the device's ability to maintain distinct resistance states. Standardized material purity requirements, typically exceeding 99.9%, and controlled grain size distributions are essential for reproducible switching behavior. The substrate preparation process must also adhere to strict cleanliness standards, with surface roughness maintained below 0.5 nm RMS to ensure uniform film deposition.

Deposition techniques require precise parameter control to achieve consistent memristor performance. Physical vapor deposition and atomic layer deposition have emerged as preferred methods, with standardized chamber conditions including base pressure below 10^-7 Torr and controlled deposition rates. Temperature uniformity across the substrate, maintained within ±2°C, ensures homogeneous film properties that directly influence state determination accuracy.

Electrode fabrication standards play a crucial role in memristor device reliability. The interface between electrodes and switching materials significantly affects the formation and dissolution of conductive filaments. Standardized electrode materials, such as platinum or titanium nitride, with controlled thickness variations below 5%, ensure consistent electric field distributions during switching operations.

Quality control measures throughout the fabrication process are essential for maintaining device uniformity. In-line monitoring of film thickness, composition, and electrical properties enables real-time process adjustments. Statistical process control methods, including control charts and capability studies, help maintain fabrication parameters within specified tolerances, directly supporting the development of reliable state determination techniques.

Environmental control during manufacturing represents another critical standard. Cleanroom conditions with particle counts below Class 100 specifications prevent contamination that could create unwanted switching sites. Humidity control below 45% relative humidity and temperature stability within ±1°C minimize process variations that affect device performance consistency.

Integration Challenges in Neuromorphic Computing Systems

The integration of variable memristor state determination technologies into neuromorphic computing systems presents multifaceted challenges that span hardware, software, and architectural domains. These challenges fundamentally stem from the inherent complexity of bridging analog memristive devices with digital processing paradigms while maintaining the computational efficiency that neuromorphic systems promise.

Hardware integration challenges primarily revolve around the precise control and readout mechanisms required for variable memristor states. The analog nature of memristive conductance variations demands sophisticated peripheral circuitry capable of accurately detecting minute resistance changes across large arrays. Signal integrity becomes critical when dealing with crossbar architectures, where sneak path currents and parasitic effects can significantly impact state determination accuracy. Additionally, process variations in memristor fabrication create device-to-device inconsistencies that complicate uniform integration across large-scale neuromorphic chips.

Thermal management represents another significant integration hurdle, as memristor state determination often requires current pulses that generate localized heating. This thermal coupling between adjacent devices can lead to unintended state changes and crosstalk, necessitating careful thermal design considerations and potentially limiting device density. The challenge intensifies in three-dimensional integration scenarios where heat dissipation becomes increasingly constrained.

Software and algorithmic integration challenges emerge from the need to map high-level neural network operations onto memristor-based hardware with inherent device limitations. The stochastic nature of memristor switching requires robust error correction and compensation algorithms that can adapt to device drift and aging effects. Furthermore, the development of efficient training algorithms that can work within the constraints of limited precision and asymmetric weight updates poses ongoing challenges for practical deployment.

System-level integration faces scalability concerns as the complexity of control circuitry grows exponentially with array size. The peripheral area overhead for accurate state determination can dominate chip area, potentially negating the density advantages of memristor-based approaches. Power management becomes increasingly complex as different operational modes require varying voltage and current levels, demanding sophisticated power delivery networks and regulation schemes.

Standardization and interface challenges also impede widespread adoption, as the lack of established protocols for memristor-based neuromorphic systems complicates integration with existing computing infrastructures and development tools.

Hardware integration challenges primarily revolve around the precise control and readout mechanisms required for variable memristor states. The analog nature of memristive conductance variations demands sophisticated peripheral circuitry capable of accurately detecting minute resistance changes across large arrays. Signal integrity becomes critical when dealing with crossbar architectures, where sneak path currents and parasitic effects can significantly impact state determination accuracy. Additionally, process variations in memristor fabrication create device-to-device inconsistencies that complicate uniform integration across large-scale neuromorphic chips.

Thermal management represents another significant integration hurdle, as memristor state determination often requires current pulses that generate localized heating. This thermal coupling between adjacent devices can lead to unintended state changes and crosstalk, necessitating careful thermal design considerations and potentially limiting device density. The challenge intensifies in three-dimensional integration scenarios where heat dissipation becomes increasingly constrained.

Software and algorithmic integration challenges emerge from the need to map high-level neural network operations onto memristor-based hardware with inherent device limitations. The stochastic nature of memristor switching requires robust error correction and compensation algorithms that can adapt to device drift and aging effects. Furthermore, the development of efficient training algorithms that can work within the constraints of limited precision and asymmetric weight updates poses ongoing challenges for practical deployment.

System-level integration faces scalability concerns as the complexity of control circuitry grows exponentially with array size. The peripheral area overhead for accurate state determination can dominate chip area, potentially negating the density advantages of memristor-based approaches. Power management becomes increasingly complex as different operational modes require varying voltage and current levels, demanding sophisticated power delivery networks and regulation schemes.

Standardization and interface challenges also impede widespread adoption, as the lack of established protocols for memristor-based neuromorphic systems complicates integration with existing computing infrastructures and development tools.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!