Gate oxide reliability in silicon carbide MOSFETs

FEB 14, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

SiC MOSFET Gate Oxide Reliability Background and Objectives

Silicon carbide (SiC) MOSFETs have emerged as transformative power semiconductor devices, offering superior performance compared to traditional silicon-based counterparts in high-voltage, high-temperature, and high-frequency applications. The wide bandgap properties of SiC enable reduced switching losses, higher breakdown voltages, and enhanced thermal conductivity, making these devices ideal for electric vehicles, renewable energy systems, industrial motor drives, and aerospace applications. However, despite these advantages, gate oxide reliability remains a critical bottleneck that limits the widespread adoption and long-term operational stability of SiC MOSFETs.

The gate oxide in SiC MOSFETs, typically composed of thermally grown silicon dioxide (SiO₂), faces unique challenges not encountered in silicon devices. The SiC/SiO₂ interface exhibits significantly higher defect densities, including carbon clusters, near-interface traps, and dangling bonds, which degrade channel mobility and threshold voltage stability. These defects arise from the inherent difficulties in oxidizing SiC and the presence of carbon at the interface, leading to reliability concerns under operational stress conditions.

Gate oxide reliability encompasses several degradation mechanisms that affect device performance over time. Time-dependent dielectric breakdown (TDDB) represents a primary failure mode, where prolonged exposure to high electric fields causes progressive oxide degradation and eventual catastrophic failure. Bias temperature instability (BTI), including both negative and positive variants, induces threshold voltage shifts through charge trapping and interface state generation. Additionally, hot carrier injection and gate leakage current contribute to accelerated aging and performance drift.

The objectives of addressing gate oxide reliability in SiC MOSFETs are multifaceted. Primarily, research aims to understand the fundamental physical mechanisms governing oxide degradation and interface trap formation. This understanding enables the development of improved oxidation processes, interface passivation techniques, and alternative dielectric materials that enhance reliability margins. Furthermore, establishing accurate lifetime prediction models and accelerated testing methodologies is essential for qualifying devices for mission-critical applications with stringent reliability requirements spanning decades of operation.

Achieving robust gate oxide reliability directly impacts the commercial viability and market penetration of SiC technology, enabling manufacturers to offer products with extended warranties and predictable performance characteristics that meet industry standards and customer expectations.

The gate oxide in SiC MOSFETs, typically composed of thermally grown silicon dioxide (SiO₂), faces unique challenges not encountered in silicon devices. The SiC/SiO₂ interface exhibits significantly higher defect densities, including carbon clusters, near-interface traps, and dangling bonds, which degrade channel mobility and threshold voltage stability. These defects arise from the inherent difficulties in oxidizing SiC and the presence of carbon at the interface, leading to reliability concerns under operational stress conditions.

Gate oxide reliability encompasses several degradation mechanisms that affect device performance over time. Time-dependent dielectric breakdown (TDDB) represents a primary failure mode, where prolonged exposure to high electric fields causes progressive oxide degradation and eventual catastrophic failure. Bias temperature instability (BTI), including both negative and positive variants, induces threshold voltage shifts through charge trapping and interface state generation. Additionally, hot carrier injection and gate leakage current contribute to accelerated aging and performance drift.

The objectives of addressing gate oxide reliability in SiC MOSFETs are multifaceted. Primarily, research aims to understand the fundamental physical mechanisms governing oxide degradation and interface trap formation. This understanding enables the development of improved oxidation processes, interface passivation techniques, and alternative dielectric materials that enhance reliability margins. Furthermore, establishing accurate lifetime prediction models and accelerated testing methodologies is essential for qualifying devices for mission-critical applications with stringent reliability requirements spanning decades of operation.

Achieving robust gate oxide reliability directly impacts the commercial viability and market penetration of SiC technology, enabling manufacturers to offer products with extended warranties and predictable performance characteristics that meet industry standards and customer expectations.

Market Demand for Reliable SiC Power Devices

The global power electronics market is experiencing unprecedented growth driven by the accelerating transition toward electrification across multiple sectors. Electric vehicles represent one of the most significant demand drivers, with automotive manufacturers increasingly adopting silicon carbide power devices to achieve higher efficiency, extended driving range, and faster charging capabilities. The superior performance characteristics of SiC MOSFETs compared to traditional silicon-based devices make them particularly attractive for traction inverters and onboard charging systems, where power density and thermal management are critical considerations.

Renewable energy infrastructure constitutes another major application domain fueling demand for reliable SiC power devices. Solar inverters, wind turbine converters, and energy storage systems require power semiconductors capable of operating efficiently under demanding environmental conditions while maintaining long-term reliability. The ability of SiC devices to handle higher voltages and temperatures with reduced switching losses directly translates to improved system-level performance and lower lifecycle costs, making them increasingly preferred in utility-scale installations.

Industrial motor drives and power supply applications are also transitioning toward SiC technology to meet stringent energy efficiency regulations and operational requirements. Data centers, telecommunications infrastructure, and industrial automation systems demand power conversion solutions that minimize energy consumption while maximizing reliability and uptime. The compact form factor enabled by SiC devices allows for more efficient thermal management and higher power density designs, addressing space constraints in modern equipment.

However, the widespread adoption of SiC MOSFETs hinges critically on addressing gate oxide reliability concerns. End-users across all application sectors require assurance of long-term device stability and predictable failure mechanisms. Automotive qualification standards demand operational lifetimes exceeding fifteen years under harsh conditions, while industrial applications require similar longevity guarantees. Any uncertainty regarding gate oxide degradation mechanisms or time-dependent breakdown phenomena directly impacts market acceptance and deployment rates.

The market demand for reliable SiC power devices continues to intensify as system designers seek to unlock the full performance potential of wide-bandgap semiconductors. Resolving gate oxide reliability challenges represents not merely a technical requirement but a fundamental prerequisite for capturing the substantial commercial opportunities emerging across electrification and energy conversion markets.

Renewable energy infrastructure constitutes another major application domain fueling demand for reliable SiC power devices. Solar inverters, wind turbine converters, and energy storage systems require power semiconductors capable of operating efficiently under demanding environmental conditions while maintaining long-term reliability. The ability of SiC devices to handle higher voltages and temperatures with reduced switching losses directly translates to improved system-level performance and lower lifecycle costs, making them increasingly preferred in utility-scale installations.

Industrial motor drives and power supply applications are also transitioning toward SiC technology to meet stringent energy efficiency regulations and operational requirements. Data centers, telecommunications infrastructure, and industrial automation systems demand power conversion solutions that minimize energy consumption while maximizing reliability and uptime. The compact form factor enabled by SiC devices allows for more efficient thermal management and higher power density designs, addressing space constraints in modern equipment.

However, the widespread adoption of SiC MOSFETs hinges critically on addressing gate oxide reliability concerns. End-users across all application sectors require assurance of long-term device stability and predictable failure mechanisms. Automotive qualification standards demand operational lifetimes exceeding fifteen years under harsh conditions, while industrial applications require similar longevity guarantees. Any uncertainty regarding gate oxide degradation mechanisms or time-dependent breakdown phenomena directly impacts market acceptance and deployment rates.

The market demand for reliable SiC power devices continues to intensify as system designers seek to unlock the full performance potential of wide-bandgap semiconductors. Resolving gate oxide reliability challenges represents not merely a technical requirement but a fundamental prerequisite for capturing the substantial commercial opportunities emerging across electrification and energy conversion markets.

Current Gate Oxide Reliability Challenges in SiC MOSFETs

Silicon carbide MOSFETs have emerged as promising power semiconductor devices for high-voltage and high-temperature applications, yet their gate oxide reliability remains a critical bottleneck limiting widespread commercial adoption. The gate oxide in SiC MOSFETs, typically silicon dioxide grown on the SiC surface, faces unique challenges that differ fundamentally from those encountered in conventional silicon-based devices.

The primary challenge stems from the inherent material properties of the SiC-SiO2 interface. Unlike the mature Si-SiO2 system, the SiC-SiO2 interface exhibits significantly higher defect densities, typically ranging from 10^11 to 10^13 cm^-2eV^-1, which is orders of magnitude higher than silicon counterparts. These interface traps severely degrade channel mobility, increase threshold voltage instability, and create reliability concerns under prolonged operation.

Time-dependent dielectric breakdown represents another critical reliability concern. SiC MOSFETs operate under higher electric fields due to the material's wide bandgap characteristics, subjecting the gate oxide to extreme electrical stress. This accelerates charge trapping mechanisms and defect generation within the oxide layer, potentially leading to premature device failure. The breakdown field strength, while theoretically higher in SiC systems, is compromised by processing-induced defects and carbon-related contamination at the interface.

Bias temperature instability poses significant operational challenges, particularly under positive gate bias conditions. The threshold voltage shift observed during high-temperature operation directly impacts device performance and long-term stability. This phenomenon is exacerbated by the presence of near-interface traps and mobile ionic contamination, which become increasingly active at elevated temperatures typical of SiC MOSFET applications.

Carbon cluster formation at the SiC-SiO2 interface during thermal oxidation introduces additional complexity. These carbon-rich regions create localized defect states that act as charge trapping centers and scattering sites, further degrading device reliability. The challenge is compounded by the difficulty in completely removing or passivating these carbon-related defects through conventional processing techniques.

Current manufacturing processes struggle to achieve the oxide quality and interface control necessary for long-term reliability assurance. The lack of standardized reliability testing protocols specific to SiC technology further complicates the assessment and comparison of different device architectures and processing approaches across the industry.

The primary challenge stems from the inherent material properties of the SiC-SiO2 interface. Unlike the mature Si-SiO2 system, the SiC-SiO2 interface exhibits significantly higher defect densities, typically ranging from 10^11 to 10^13 cm^-2eV^-1, which is orders of magnitude higher than silicon counterparts. These interface traps severely degrade channel mobility, increase threshold voltage instability, and create reliability concerns under prolonged operation.

Time-dependent dielectric breakdown represents another critical reliability concern. SiC MOSFETs operate under higher electric fields due to the material's wide bandgap characteristics, subjecting the gate oxide to extreme electrical stress. This accelerates charge trapping mechanisms and defect generation within the oxide layer, potentially leading to premature device failure. The breakdown field strength, while theoretically higher in SiC systems, is compromised by processing-induced defects and carbon-related contamination at the interface.

Bias temperature instability poses significant operational challenges, particularly under positive gate bias conditions. The threshold voltage shift observed during high-temperature operation directly impacts device performance and long-term stability. This phenomenon is exacerbated by the presence of near-interface traps and mobile ionic contamination, which become increasingly active at elevated temperatures typical of SiC MOSFET applications.

Carbon cluster formation at the SiC-SiO2 interface during thermal oxidation introduces additional complexity. These carbon-rich regions create localized defect states that act as charge trapping centers and scattering sites, further degrading device reliability. The challenge is compounded by the difficulty in completely removing or passivating these carbon-related defects through conventional processing techniques.

Current manufacturing processes struggle to achieve the oxide quality and interface control necessary for long-term reliability assurance. The lack of standardized reliability testing protocols specific to SiC technology further complicates the assessment and comparison of different device architectures and processing approaches across the industry.

Existing Gate Oxide Reliability Enhancement Solutions

01 Gate oxide formation and passivation techniques

Various methods for forming and passivating gate oxide layers in silicon carbide MOSFETs to improve reliability. These techniques include thermal oxidation processes, nitridation treatments, and deposition of high-quality dielectric materials. The passivation methods help reduce interface trap density and improve the oxide-semiconductor interface quality, which are critical for long-term reliability and stable threshold voltage operation.- Gate oxide formation and passivation techniques: Methods for forming high-quality gate oxide layers on silicon carbide substrates through optimized oxidation processes, including thermal oxidation, nitridation, and passivation treatments. These techniques aim to reduce interface trap density and improve the dielectric properties of the gate oxide. Advanced processes such as nitrogen incorporation during oxidation or post-oxidation annealing in specific atmospheres can significantly enhance the oxide quality and reduce defects at the SiC/SiO2 interface.

- Interface engineering and defect reduction: Techniques focused on improving the silicon carbide and gate oxide interface quality by reducing interface states and defects. This includes methods such as hydrogen annealing, counter-doping at the interface, and the use of buffer layers or interlayers between the silicon carbide and gate oxide. These approaches help minimize threshold voltage instability and improve channel mobility by reducing the density of interface traps that can capture carriers.

- Alternative gate dielectric materials: Implementation of high-k dielectric materials or composite dielectric stacks as alternatives to traditional silicon dioxide for improved reliability. These materials can include aluminum oxide, hafnium oxide, or multilayer structures that provide better dielectric strength, reduced leakage current, and improved resistance to electrical stress. The use of alternative dielectrics can also help reduce the electric field across the oxide layer.

- Reliability testing and characterization methods: Methodologies for evaluating gate oxide reliability through various stress testing protocols including time-dependent dielectric breakdown, bias temperature instability testing, and high-temperature gate bias stress. These characterization techniques help assess oxide lifetime, identify failure mechanisms, and establish reliability metrics. Advanced monitoring systems can track parameters such as threshold voltage shift, leakage current evolution, and interface trap generation during accelerated aging tests.

- Device structure optimization for oxide protection: Design modifications to the MOSFET structure that enhance gate oxide reliability, including optimized gate electrode materials, edge termination structures, and field plate designs. These structural improvements help distribute electric field more uniformly across the oxide, reduce peak field concentrations at critical regions, and provide better protection against electrical overstress. Manufacturing process optimizations such as controlled doping profiles and improved lithography can also contribute to enhanced oxide reliability.

02 Interface trap reduction and defect management

Approaches to minimize interface traps and defects at the silicon carbide and gate oxide interface. Methods include hydrogen annealing, nitrogen incorporation, and specialized thermal treatments that reduce dangling bonds and carbon-related defects. These techniques significantly improve channel mobility and reduce threshold voltage instability, enhancing overall device reliability.Expand Specific Solutions03 Screening and testing methodologies for oxide reliability

Testing and screening procedures designed to evaluate gate oxide reliability in silicon carbide MOSFETs. These include time-dependent dielectric breakdown testing, bias temperature instability measurements, and accelerated life testing protocols. Such methodologies help identify weak oxide regions and predict long-term reliability performance under various operating conditions.Expand Specific Solutions04 Advanced gate dielectric materials and structures

Implementation of alternative dielectric materials and multilayer gate structures to enhance oxide reliability. These include high-k dielectrics, composite oxide layers, and engineered dielectric stacks that provide improved breakdown voltage, reduced leakage current, and better resistance to electrical stress. Such structures offer superior performance compared to conventional thermal oxides.Expand Specific Solutions05 Device structure optimization for enhanced reliability

Design modifications and structural optimizations in silicon carbide MOSFET architecture to improve gate oxide reliability. These include edge termination designs, field plate structures, and optimized doping profiles that reduce electric field concentration at the oxide interface. Such structural improvements minimize hot carrier injection and extend device lifetime under high voltage and high temperature operation.Expand Specific Solutions

Key Players in SiC Power Semiconductor Industry

The silicon carbide MOSFET gate oxide reliability field is in a rapid growth phase, driven by expanding electric vehicle and renewable energy markets. The global SiC power device market is experiencing substantial expansion, with projections indicating multi-billion dollar valuations as adoption accelerates across automotive, industrial, and energy sectors. Technology maturity varies significantly among players: established leaders like Wolfspeed, Mitsubishi Electric, and TSMC demonstrate advanced manufacturing capabilities and proven reliability solutions, while emerging companies such as Global Power Technology, Fast Sic Semiconductor, and Semiq are developing competitive offerings. Traditional semiconductor giants including Bosch, Panasonic, and GlobalFoundries are leveraging existing expertise to enter this space. Chinese entities like Yangzhou Yangjie, Zhuzhou CRRC Times Semiconductor, and various research institutions are rapidly advancing domestic capabilities. The competitive landscape reflects a mix of mature technology providers and innovative newcomers addressing critical gate oxide reliability challenges essential for commercial SiC MOSFET deployment.

Wolfspeed, Inc.

Technical Solution: Wolfspeed employs advanced gate oxide engineering techniques to enhance reliability in SiC MOSFETs. Their approach includes optimized thermal oxidation processes combined with post-oxidation annealing in nitric oxide (NO) ambient to reduce interface trap density at the SiO2/SiC interface. The company implements nitrogen incorporation at the gate oxide interface to passivate carbon-related defects and dangling bonds, which are primary sources of reliability degradation. Wolfspeed's gate oxide typically achieves interface trap densities below 3×10^11 cm-2eV-1 and demonstrates time-dependent dielectric breakdown (TDDB) lifetimes exceeding 100 years under operating conditions. Their manufacturing process includes stringent control of oxidation temperature profiles and multi-step annealing sequences to ensure consistent oxide quality and long-term threshold voltage stability.

Strengths: Industry-leading gate oxide reliability with proven field performance, extensive manufacturing experience, and comprehensive quality control processes. Weaknesses: Higher manufacturing costs due to complex processing steps, and potential scalability challenges for next-generation high-voltage devices.

Mitsubishi Electric Corp.

Technical Solution: Mitsubishi Electric has developed proprietary gate oxide formation techniques focusing on ultra-clean oxidation environments and precise temperature control to minimize defect generation in SiC MOSFETs. Their technology incorporates a two-step oxidation process: initial dry oxidation followed by wet oxidation with controlled humidity levels to achieve optimal oxide thickness uniformity. The company utilizes phosphorus doping in the gate polysilicon combined with optimized annealing cycles to reduce electric field stress at the oxide interface. Mitsubishi's approach includes comprehensive reliability screening using high-temperature gate bias (HTGB) stress testing and time-dependent dielectric breakdown analysis. Their devices demonstrate stable threshold voltage characteristics with drift rates less than 50mV over 10 years of projected operation, and breakdown field strengths exceeding 10MV/cm.

Strengths: Strong integration with power module packaging expertise, robust reliability validation protocols, and excellent thermal cycling performance. Weaknesses: Limited market presence outside industrial applications, and relatively conservative voltage scaling roadmap compared to pure-play SiC manufacturers.

Core Innovations in SiC Gate Dielectric Technologies

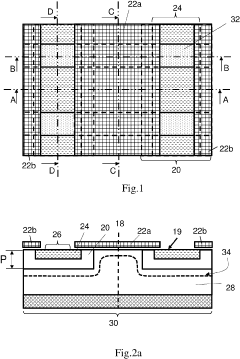

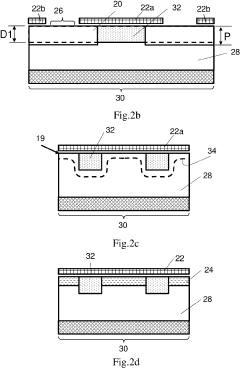

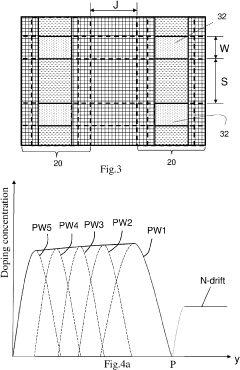

Sic mosfet with transverse p+ region

PatentActiveUS20230053874A1

Innovation

- The design incorporates a silicon carbide MOSFET structure with specific doping layers and geometries, including a polysilicon gate layer, to enhance the protection of the gate oxide without increasing the MOSFET cell area, utilizing epitaxy and ion implantation processes to create N+ and P+ regions that act as shields, ensuring adequate body diode performance and channel mobility.

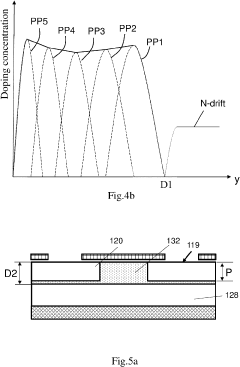

Semiconductor device and method of manufacturing semiconductor device

PatentPendingEP4531110A1

Innovation

- The semiconductor device incorporates a JFET region with a width that is greater near the top surface than at the bottom, and second well regions with a notch at the bottom part toward the JFET region, creating a shielding effect for the gate interface. This is achieved through a manufacturing process involving epitaxy layers, scatter oxide layers, and angled dopant implantation.

Automotive and Industrial Standards for SiC Devices

The deployment of silicon carbide MOSFETs in automotive and industrial applications necessitates compliance with stringent reliability and safety standards that directly address gate oxide integrity. The automotive sector, governed primarily by the AEC-Q101 qualification standard for discrete semiconductors, imposes rigorous testing protocols including high-temperature reverse bias (HTRB), high-temperature gate bias (HTGB), and temperature cycling tests that specifically evaluate gate oxide robustness under operational stress conditions. These standards mandate extended stress durations at elevated temperatures, often exceeding 1000 hours at junction temperatures of 175°C or higher, conditions that critically challenge the stability of the SiC-SiO2 interface.

Industrial applications reference IEC 61287 and related standards that establish reliability benchmarks for power semiconductor devices operating in harsh environments. These frameworks require demonstration of gate oxide time-dependent dielectric breakdown (TDDB) characteristics with projected lifetimes exceeding 20 years under continuous operation. The standards specify maximum allowable gate leakage currents, typically in the nanoampere range, and define threshold voltage shift limits that ensure consistent device performance throughout the operational lifetime.

Recent updates to automotive functional safety standards, particularly ISO 26262, have introduced additional requirements for systematic capability and random hardware failure metrics that directly impact gate oxide design margins. Manufacturers must demonstrate failure-in-time (FIT) rates below specified thresholds, necessitating comprehensive understanding of oxide degradation mechanisms and their statistical distributions. The JEDEC JEP122H standard provides guidelines for calculating device-level FIT rates based on gate oxide reliability data, establishing methodologies for accelerated testing and lifetime projection.

Certification bodies increasingly demand evidence of gate oxide reliability under dynamic switching conditions rather than static stress alone, reflecting real-world operational profiles in traction inverters and motor drives. This shift has prompted development of application-specific test protocols that combine electrical stress with thermal cycling and humidity exposure, creating multi-stress environments that more accurately replicate field conditions. Compliance with these evolving standards requires not only meeting minimum qualification criteria but also implementing robust process controls and continuous monitoring systems that ensure consistent gate oxide quality across production volumes.

Industrial applications reference IEC 61287 and related standards that establish reliability benchmarks for power semiconductor devices operating in harsh environments. These frameworks require demonstration of gate oxide time-dependent dielectric breakdown (TDDB) characteristics with projected lifetimes exceeding 20 years under continuous operation. The standards specify maximum allowable gate leakage currents, typically in the nanoampere range, and define threshold voltage shift limits that ensure consistent device performance throughout the operational lifetime.

Recent updates to automotive functional safety standards, particularly ISO 26262, have introduced additional requirements for systematic capability and random hardware failure metrics that directly impact gate oxide design margins. Manufacturers must demonstrate failure-in-time (FIT) rates below specified thresholds, necessitating comprehensive understanding of oxide degradation mechanisms and their statistical distributions. The JEDEC JEP122H standard provides guidelines for calculating device-level FIT rates based on gate oxide reliability data, establishing methodologies for accelerated testing and lifetime projection.

Certification bodies increasingly demand evidence of gate oxide reliability under dynamic switching conditions rather than static stress alone, reflecting real-world operational profiles in traction inverters and motor drives. This shift has prompted development of application-specific test protocols that combine electrical stress with thermal cycling and humidity exposure, creating multi-stress environments that more accurately replicate field conditions. Compliance with these evolving standards requires not only meeting minimum qualification criteria but also implementing robust process controls and continuous monitoring systems that ensure consistent gate oxide quality across production volumes.

High Temperature Operation Impact on Gate Oxide

Silicon carbide MOSFETs are increasingly deployed in high-temperature environments due to their superior material properties, yet elevated operating temperatures impose severe stress on the gate oxide layer, fundamentally altering its reliability characteristics. The gate oxide in SiC MOSFETs, typically composed of thermally grown silicon dioxide, experiences accelerated degradation mechanisms when subjected to temperatures exceeding 150°C, which are common in automotive, aerospace, and industrial power conversion applications. At elevated temperatures, the intrinsic defect generation rate within the oxide increases exponentially, leading to enhanced trap-assisted tunneling and increased leakage currents that compromise device performance and long-term stability.

The thermal activation of charge carriers at high temperatures significantly amplifies the stress on the gate oxide interface. Elevated temperatures enhance the mobility of ionic contaminants and hydrogen-related species within the oxide, which can migrate toward the SiC-SiO2 interface and create additional interface states. These interface traps not only degrade the channel mobility but also shift the threshold voltage, causing parametric drift that affects circuit-level performance. Furthermore, the combination of high temperature and electric field stress creates a synergistic effect that accelerates time-dependent dielectric breakdown, reducing the operational lifetime of the device substantially compared to room-temperature operation.

The coefficient of thermal expansion mismatch between silicon carbide and silicon dioxide becomes more pronounced at elevated temperatures, inducing mechanical stress at the interface that can generate structural defects and weaken the oxide integrity. This thermomechanical stress, coupled with the inherent roughness of the SiC-SiO2 interface due to carbon-related defects, creates localized electric field enhancements that serve as preferential sites for oxide breakdown. High-temperature operation also exacerbates the impact of bias temperature instability, where prolonged gate bias at elevated temperatures causes progressive degradation of the oxide quality through charge trapping and interface state generation.

Understanding these temperature-dependent degradation mechanisms is essential for developing robust gate oxide engineering strategies and establishing realistic operational limits for SiC MOSFET deployment in harsh thermal environments.

The thermal activation of charge carriers at high temperatures significantly amplifies the stress on the gate oxide interface. Elevated temperatures enhance the mobility of ionic contaminants and hydrogen-related species within the oxide, which can migrate toward the SiC-SiO2 interface and create additional interface states. These interface traps not only degrade the channel mobility but also shift the threshold voltage, causing parametric drift that affects circuit-level performance. Furthermore, the combination of high temperature and electric field stress creates a synergistic effect that accelerates time-dependent dielectric breakdown, reducing the operational lifetime of the device substantially compared to room-temperature operation.

The coefficient of thermal expansion mismatch between silicon carbide and silicon dioxide becomes more pronounced at elevated temperatures, inducing mechanical stress at the interface that can generate structural defects and weaken the oxide integrity. This thermomechanical stress, coupled with the inherent roughness of the SiC-SiO2 interface due to carbon-related defects, creates localized electric field enhancements that serve as preferential sites for oxide breakdown. High-temperature operation also exacerbates the impact of bias temperature instability, where prolonged gate bias at elevated temperatures causes progressive degradation of the oxide quality through charge trapping and interface state generation.

Understanding these temperature-dependent degradation mechanisms is essential for developing robust gate oxide engineering strategies and establishing realistic operational limits for SiC MOSFET deployment in harsh thermal environments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!