Reducing Signal Instability in Forksheet Arrays

APR 9, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Forksheet Array Signal Stability Background and Objectives

Forksheet arrays represent a revolutionary advancement in semiconductor device architecture, emerging as a critical solution for continuing Moore's Law scaling beyond the 3nm technology node. These three-dimensional transistor structures feature vertically stacked nanosheets with fork-like configurations that enable unprecedented device density while maintaining electrostatic control. The technology builds upon the foundation of Gate-All-Around (GAA) transistors, incorporating multiple parallel channels that significantly enhance current drive capability per unit area.

The evolution of forksheet technology stems from the semiconductor industry's relentless pursuit of performance improvements amid physical scaling limitations. Traditional FinFET structures have approached their practical limits in terms of power efficiency and area scaling, necessitating innovative architectural approaches. Forksheet arrays address these constraints by implementing a unique geometry where multiple nanosheets are arranged in a fork-like pattern, allowing for independent gate control and optimized current flow paths.

Signal instability in forksheet arrays has emerged as one of the most significant technical challenges hindering widespread commercial adoption. This instability manifests through various mechanisms including threshold voltage variations, parasitic capacitance fluctuations, and inter-sheet coupling effects. The complex three-dimensional geometry creates multiple potential sources of electrical interference, making signal integrity maintenance considerably more challenging than in conventional planar or FinFET devices.

Current research indicates that signal instability primarily originates from manufacturing process variations, material interface defects, and electromagnetic coupling between adjacent nanosheets. These factors contribute to unpredictable device behavior, reduced yield rates, and compromised circuit reliability. The industry recognizes that addressing these stability issues is paramount for successful technology transfer from research laboratories to high-volume manufacturing environments.

The primary objective of signal stability enhancement in forksheet arrays focuses on achieving consistent electrical characteristics across all device instances within an array. This encompasses minimizing threshold voltage scatter, reducing parasitic effects, and ensuring uniform current-voltage relationships. Additionally, the goal extends to developing robust design methodologies that can predict and compensate for potential instability sources during the circuit design phase.

Long-term technological objectives include establishing manufacturing processes capable of producing forksheet arrays with signal stability metrics comparable to or exceeding current FinFET standards. This requires developing advanced process control techniques, novel materials engineering approaches, and sophisticated circuit design strategies that can effectively mitigate inherent structural complexities while maximizing the performance benefits of the forksheet architecture.

The evolution of forksheet technology stems from the semiconductor industry's relentless pursuit of performance improvements amid physical scaling limitations. Traditional FinFET structures have approached their practical limits in terms of power efficiency and area scaling, necessitating innovative architectural approaches. Forksheet arrays address these constraints by implementing a unique geometry where multiple nanosheets are arranged in a fork-like pattern, allowing for independent gate control and optimized current flow paths.

Signal instability in forksheet arrays has emerged as one of the most significant technical challenges hindering widespread commercial adoption. This instability manifests through various mechanisms including threshold voltage variations, parasitic capacitance fluctuations, and inter-sheet coupling effects. The complex three-dimensional geometry creates multiple potential sources of electrical interference, making signal integrity maintenance considerably more challenging than in conventional planar or FinFET devices.

Current research indicates that signal instability primarily originates from manufacturing process variations, material interface defects, and electromagnetic coupling between adjacent nanosheets. These factors contribute to unpredictable device behavior, reduced yield rates, and compromised circuit reliability. The industry recognizes that addressing these stability issues is paramount for successful technology transfer from research laboratories to high-volume manufacturing environments.

The primary objective of signal stability enhancement in forksheet arrays focuses on achieving consistent electrical characteristics across all device instances within an array. This encompasses minimizing threshold voltage scatter, reducing parasitic effects, and ensuring uniform current-voltage relationships. Additionally, the goal extends to developing robust design methodologies that can predict and compensate for potential instability sources during the circuit design phase.

Long-term technological objectives include establishing manufacturing processes capable of producing forksheet arrays with signal stability metrics comparable to or exceeding current FinFET standards. This requires developing advanced process control techniques, novel materials engineering approaches, and sophisticated circuit design strategies that can effectively mitigate inherent structural complexities while maximizing the performance benefits of the forksheet architecture.

Market Demand for Stable Forksheet Array Solutions

The semiconductor industry faces mounting pressure to deliver increasingly sophisticated electronic devices with enhanced performance and reliability. Forksheet arrays, representing a critical advancement in transistor architecture for sub-3nm technology nodes, have emerged as a pivotal solution for maintaining Moore's Law progression. However, signal instability issues in these arrays pose significant challenges that directly impact device performance, yield rates, and overall market viability.

Market demand for stable forksheet array solutions is primarily driven by the explosive growth in artificial intelligence, machine learning, and high-performance computing applications. These sectors require processors with exceptional computational density and energy efficiency, characteristics that forksheet technology promises to deliver. The automotive industry's transition toward autonomous vehicles and advanced driver assistance systems further amplifies demand for reliable semiconductor solutions capable of operating under stringent safety requirements.

Consumer electronics manufacturers are increasingly seeking forksheet-based processors to power next-generation smartphones, tablets, and wearable devices. The market expects these devices to deliver superior performance while maintaining extended battery life, creating substantial demand for stable signal processing capabilities. Data center operators and cloud service providers represent another significant market segment, requiring processors that can handle massive computational workloads with minimal signal degradation.

The telecommunications sector's deployment of 5G and preparation for 6G networks creates additional market pressure for stable forksheet solutions. Network infrastructure equipment demands exceptional signal integrity to support high-frequency operations and ultra-low latency requirements. Signal instability in forksheet arrays could severely compromise network performance and reliability.

Manufacturing yield considerations significantly influence market demand patterns. Semiconductor foundries require forksheet solutions that demonstrate consistent signal stability across large-scale production runs. Variability in signal performance directly translates to reduced yields and increased manufacturing costs, making stability a critical market differentiator.

The Internet of Things ecosystem expansion creates diverse market opportunities for stable forksheet arrays. Edge computing devices, industrial sensors, and smart city infrastructure require reliable signal processing capabilities across varying environmental conditions. Market demand extends beyond traditional computing applications to encompass specialized requirements for medical devices, aerospace systems, and industrial automation equipment.

Regional market dynamics reveal concentrated demand in technology hubs including Silicon Valley, Taiwan, South Korea, and emerging semiconductor manufacturing centers. Government initiatives supporting domestic semiconductor capabilities further influence market demand patterns, with national security considerations driving requirements for reliable, domestically-produced forksheet solutions.

Market demand for stable forksheet array solutions is primarily driven by the explosive growth in artificial intelligence, machine learning, and high-performance computing applications. These sectors require processors with exceptional computational density and energy efficiency, characteristics that forksheet technology promises to deliver. The automotive industry's transition toward autonomous vehicles and advanced driver assistance systems further amplifies demand for reliable semiconductor solutions capable of operating under stringent safety requirements.

Consumer electronics manufacturers are increasingly seeking forksheet-based processors to power next-generation smartphones, tablets, and wearable devices. The market expects these devices to deliver superior performance while maintaining extended battery life, creating substantial demand for stable signal processing capabilities. Data center operators and cloud service providers represent another significant market segment, requiring processors that can handle massive computational workloads with minimal signal degradation.

The telecommunications sector's deployment of 5G and preparation for 6G networks creates additional market pressure for stable forksheet solutions. Network infrastructure equipment demands exceptional signal integrity to support high-frequency operations and ultra-low latency requirements. Signal instability in forksheet arrays could severely compromise network performance and reliability.

Manufacturing yield considerations significantly influence market demand patterns. Semiconductor foundries require forksheet solutions that demonstrate consistent signal stability across large-scale production runs. Variability in signal performance directly translates to reduced yields and increased manufacturing costs, making stability a critical market differentiator.

The Internet of Things ecosystem expansion creates diverse market opportunities for stable forksheet arrays. Edge computing devices, industrial sensors, and smart city infrastructure require reliable signal processing capabilities across varying environmental conditions. Market demand extends beyond traditional computing applications to encompass specialized requirements for medical devices, aerospace systems, and industrial automation equipment.

Regional market dynamics reveal concentrated demand in technology hubs including Silicon Valley, Taiwan, South Korea, and emerging semiconductor manufacturing centers. Government initiatives supporting domestic semiconductor capabilities further influence market demand patterns, with national security considerations driving requirements for reliable, domestically-produced forksheet solutions.

Current Signal Instability Issues in Forksheet Technologies

Forksheet transistor arrays face significant signal instability challenges that stem from their unique three-dimensional architecture and complex manufacturing requirements. The fundamental issue lies in the inherent structural asymmetry between P-type and N-type regions, where the shared middle sheet creates uneven parasitic capacitances and resistance variations across different transistor elements within the array.

Process-induced variations represent a major source of signal instability in forksheet technologies. The critical dimension control during the formation of the central dividing wall often exhibits non-uniformities, leading to variations in channel width and effective gate control across individual transistors. These manufacturing inconsistencies result in threshold voltage mismatches that can exceed 50mV within a single array, significantly impacting circuit performance and yield.

Thermal management issues compound the stability problems in forksheet arrays. The dense three-dimensional structure creates localized hotspots during operation, particularly at the junction regions where P and N channels meet. Temperature gradients across the array cause differential thermal expansion and contraction, leading to mechanical stress that affects carrier mobility and introduces time-dependent signal drift.

Parasitic coupling effects between adjacent forksheet structures create another layer of complexity. The proximity of P and N channels in the vertical stack generates unwanted capacitive and inductive coupling, resulting in crosstalk and signal interference. This coupling becomes more pronounced at higher operating frequencies, where the parasitic reactances significantly impact signal integrity and timing characteristics.

Gate control uniformity presents additional challenges due to the complex geometry of forksheet transistors. The wrap-around gate structure, while providing excellent electrostatic control, suffers from corner effects and field concentration issues that vary across the array. These non-uniformities lead to inconsistent switching characteristics and contribute to overall signal instability.

Contact resistance variations further exacerbate stability issues in forksheet arrays. The multi-level metallization required to connect the vertically stacked channels introduces additional resistance and capacitance variations. Poor contact formation or degradation over time can cause significant changes in signal transmission characteristics, particularly affecting high-speed digital applications where precise timing is critical.

Process-induced variations represent a major source of signal instability in forksheet technologies. The critical dimension control during the formation of the central dividing wall often exhibits non-uniformities, leading to variations in channel width and effective gate control across individual transistors. These manufacturing inconsistencies result in threshold voltage mismatches that can exceed 50mV within a single array, significantly impacting circuit performance and yield.

Thermal management issues compound the stability problems in forksheet arrays. The dense three-dimensional structure creates localized hotspots during operation, particularly at the junction regions where P and N channels meet. Temperature gradients across the array cause differential thermal expansion and contraction, leading to mechanical stress that affects carrier mobility and introduces time-dependent signal drift.

Parasitic coupling effects between adjacent forksheet structures create another layer of complexity. The proximity of P and N channels in the vertical stack generates unwanted capacitive and inductive coupling, resulting in crosstalk and signal interference. This coupling becomes more pronounced at higher operating frequencies, where the parasitic reactances significantly impact signal integrity and timing characteristics.

Gate control uniformity presents additional challenges due to the complex geometry of forksheet transistors. The wrap-around gate structure, while providing excellent electrostatic control, suffers from corner effects and field concentration issues that vary across the array. These non-uniformities lead to inconsistent switching characteristics and contribute to overall signal instability.

Contact resistance variations further exacerbate stability issues in forksheet arrays. The multi-level metallization required to connect the vertically stacked channels introduces additional resistance and capacitance variations. Poor contact formation or degradation over time can cause significant changes in signal transmission characteristics, particularly affecting high-speed digital applications where precise timing is critical.

Existing Signal Stabilization Solutions for Arrays

01 Structural design modifications for forksheet transistor stability

Forksheet transistor arrays can experience signal instability due to structural variations and parasitic effects. Modifications to the physical structure, including optimized spacing between adjacent sheets, improved gate alignment, and enhanced isolation structures, can significantly reduce signal fluctuations. Design techniques focusing on uniform sheet dimensions and controlled aspect ratios help maintain consistent electrical characteristics across the array, thereby improving overall signal stability and device reliability.- Structural design optimization for forksheet transistor arrays: Forksheet transistor arrays can experience signal instability due to structural design issues. Optimizing the geometric configuration of the forksheet structures, including the spacing between adjacent sheets, the thickness of dielectric isolation layers, and the alignment of gate structures, can significantly improve signal stability. Advanced lithography techniques and precise etching processes are employed to achieve the desired structural parameters that minimize parasitic capacitance and resistance effects.

- Dielectric isolation enhancement between forksheet structures: Signal instability in forksheet arrays often stems from inadequate electrical isolation between adjacent transistor structures. Implementing high-k dielectric materials or multi-layer dielectric stacks between forksheet elements can reduce cross-talk and leakage currents. The selection of appropriate dielectric materials with optimal thickness and composition helps maintain signal integrity by preventing unwanted coupling between neighboring devices.

- Gate stack engineering for improved signal control: The gate stack configuration in forksheet arrays plays a critical role in signal stability. Engineering the gate electrode materials, work function tuning layers, and interfacial oxide layers can enhance the electrostatic control over the channel region. This approach reduces threshold voltage variations and improves the switching characteristics of the transistors, thereby stabilizing signal transmission across the array.

- Contact and interconnect optimization for reduced resistance: Signal instability can arise from high contact resistance and interconnect parasitic effects in forksheet arrays. Optimizing the contact formation process, including the use of low-resistance metal silicides and barrier layers, reduces series resistance. Additionally, designing interconnect layouts with minimized length and optimized cross-sectional area helps maintain signal integrity by reducing RC delay and voltage drops across the array.

- Stress management and mechanical stability techniques: Mechanical stress in forksheet structures can lead to signal instability through mobility degradation and threshold voltage shifts. Implementing stress engineering techniques, such as strain-inducing layers or stress-relief structures, helps maintain consistent electrical characteristics. Proper thermal budget management during fabrication and the use of mechanically robust materials ensure long-term stability of the forksheet arrays under operational conditions.

02 Material engineering and interface optimization

Signal instability in forksheet arrays can be mitigated through careful selection and engineering of materials at critical interfaces. The use of high-quality dielectric materials with low trap density, optimized work function metals for gate electrodes, and improved contact materials can reduce charge trapping and interface state effects. Advanced deposition techniques and surface treatments ensure better interface quality, leading to reduced noise and improved signal integrity in forksheet transistor arrays.Expand Specific Solutions03 Process control and manufacturing techniques

Manufacturing process variations are a significant contributor to signal instability in forksheet arrays. Implementing precise lithography techniques, controlled etching processes, and uniform deposition methods can minimize dimensional variations across the array. Advanced process monitoring and feedback control systems help maintain consistency in critical dimensions and material properties. Sequential fabrication steps with improved alignment accuracy and reduced process-induced stress contribute to enhanced device uniformity and signal stability.Expand Specific Solutions04 Electrical characterization and compensation circuits

Active compensation and calibration techniques can address signal instability in forksheet arrays. Circuit-level solutions include adaptive biasing schemes, feedback compensation networks, and on-chip calibration circuits that dynamically adjust operating parameters to counteract variations. Electrical characterization methods enable identification of instability sources and implementation of targeted correction strategies. Integration of sensing and adjustment mechanisms within the array architecture allows real-time compensation for environmental and operational variations affecting signal stability.Expand Specific Solutions05 Thermal management and stress reduction

Thermal effects and mechanical stress are critical factors contributing to signal instability in forksheet transistor arrays. Implementation of effective thermal dissipation structures, including optimized substrate materials and heat spreading layers, helps maintain uniform temperature distribution. Stress engineering techniques, such as strategic placement of stress-relief structures and selection of materials with matched thermal expansion coefficients, reduce thermomechanical effects. These approaches minimize temperature-dependent variations and stress-induced performance shifts, resulting in improved signal stability across operating conditions.Expand Specific Solutions

Key Players in Forksheet Array Development Industry

The forksheet array signal instability reduction technology represents an emerging semiconductor manufacturing challenge within the advanced node development sector. The industry is in a transitional phase, moving from traditional FinFET architectures to next-generation gate-all-around structures, creating a specialized but growing market segment estimated in the billions as foundries prepare for sub-3nm processes. Technology maturity varies significantly among key players, with Intel, Samsung Electronics, and IBM leading fundamental research and patent development, while Taiwan Semiconductor Manufacturing Company and other foundries focus on manufacturing implementation. Companies like Texas Instruments and Socionext contribute specialized analog and mixed-signal expertise, while research institutions including University of Massachusetts provide theoretical foundations. The competitive landscape shows established semiconductor giants leveraging existing fabrication capabilities alongside emerging specialized firms developing novel signal stabilization techniques, indicating a market poised for rapid evolution as demand for ultra-scaled transistor technologies intensifies across computing and mobile applications.

International Business Machines Corp.

Technical Solution: IBM has pioneered research into forksheet transistor architectures with focus on reducing signal instability through innovative device physics approaches. Their solution involves implementing strained silicon channels with optimized crystal orientation to improve carrier transport properties and reduce scattering effects. IBM's approach includes development of novel gate stack engineering techniques that minimize interface trap density and improve electrostatic control. The company has also investigated advanced interconnect schemes that reduce coupling effects between adjacent forksheet devices, utilizing low-k dielectric materials and optimized routing strategies to maintain signal integrity across large arrays.

Strengths: Strong fundamental research capabilities and deep understanding of device physics principles. Weaknesses: Limited manufacturing scale compared to pure-play foundries and longer time-to-market for commercial implementation.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed integrated solutions for forksheet array signal stability focusing on system-level optimization and advanced packaging techniques. Their approach combines improved device design with sophisticated signal processing algorithms to compensate for inherent variability in forksheet structures. The company implements advanced error correction mechanisms and adaptive calibration systems that dynamically adjust for signal variations across the array. Huawei's solution also incorporates thermal management strategies and power delivery optimization to minimize temperature-induced signal instability, utilizing advanced substrate materials and innovative cooling solutions to maintain consistent operating conditions.

Strengths: System-level integration expertise and strong capabilities in signal processing and compensation techniques. Weaknesses: Limited access to cutting-edge fabrication technologies due to trade restrictions and dependency on external foundry partners.

Core Patents in Forksheet Signal Stability Enhancement

Pre-emphasis for strobe signals in memory device

PatentInactiveUS7397712B2

Innovation

- Incorporating a pre-emphasis controller and strobe output circuits with termination units to stabilize the strobe signals by modifying their signal levels, specifically using pre-emphasis control signals to influence the slew rate and ensure full signal swing when transitioning from a termination level to another, thereby reducing instability.

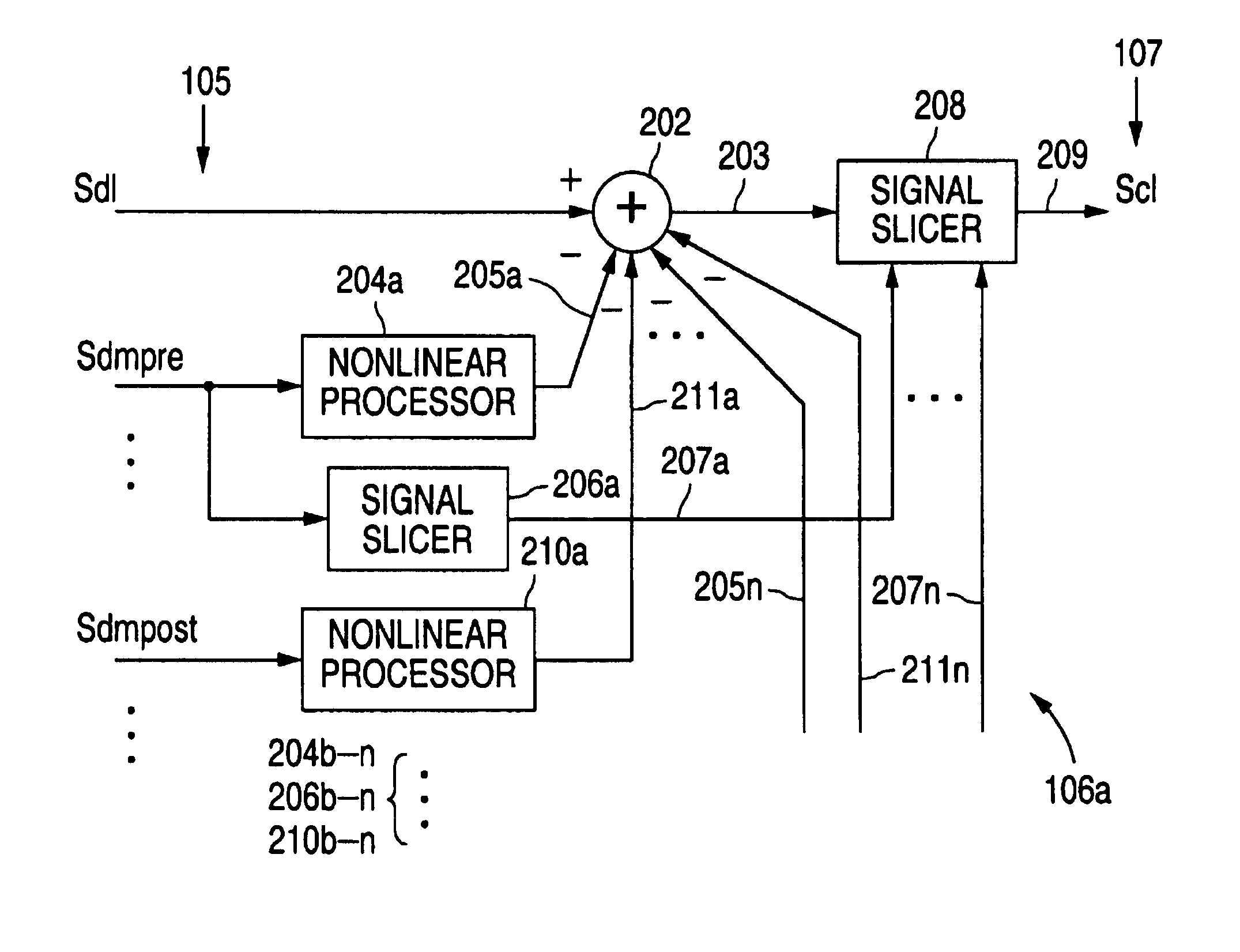

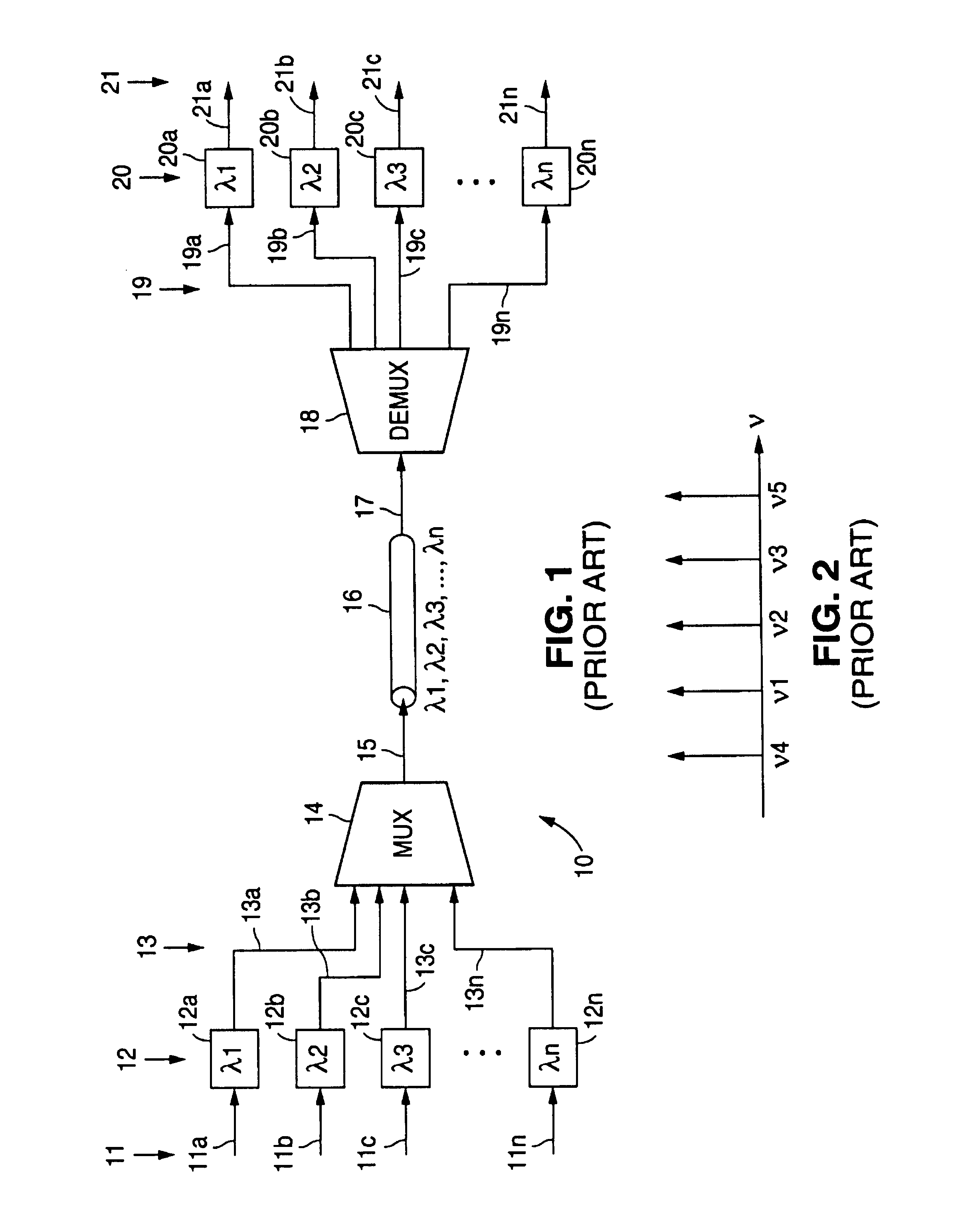

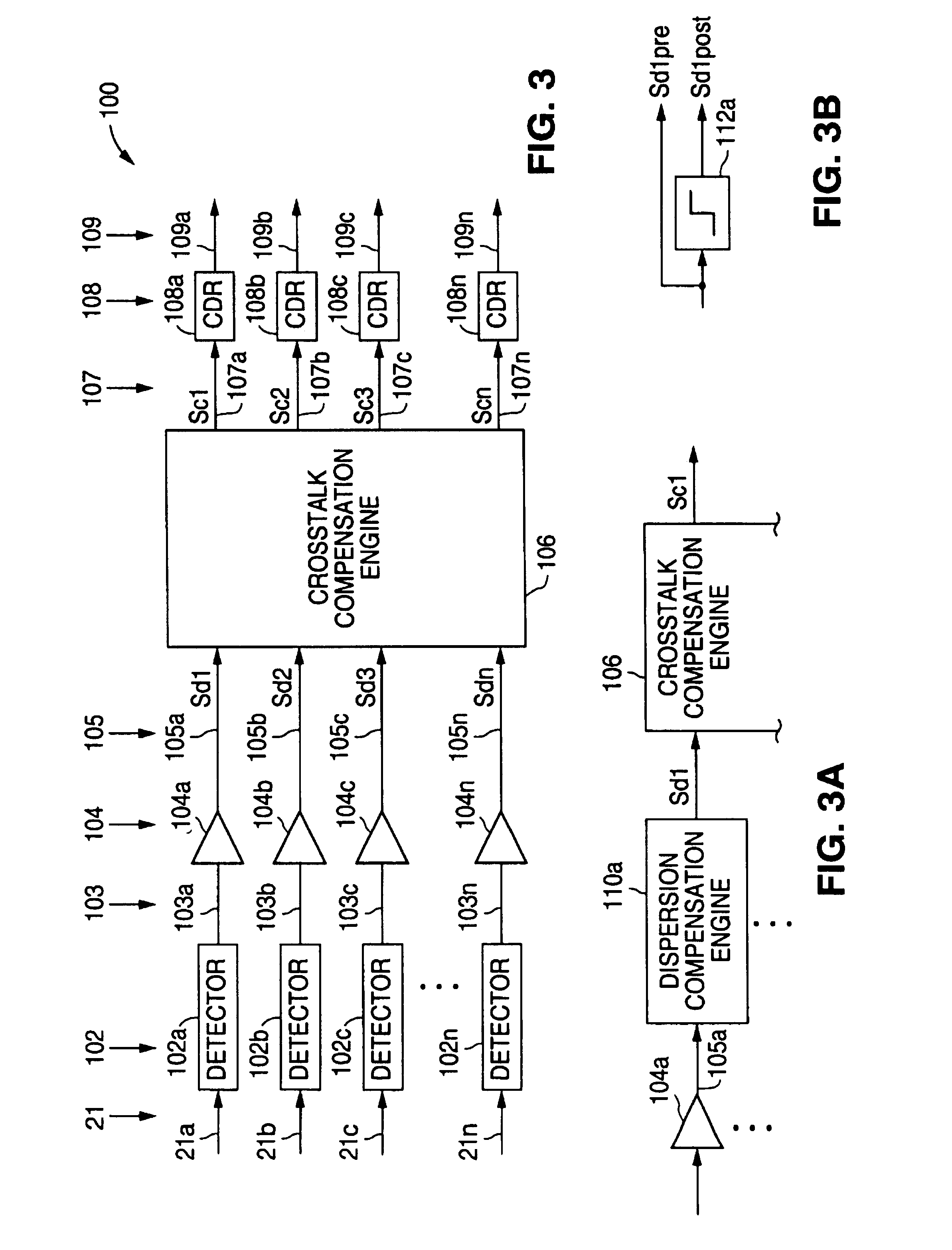

Crosstalk compensation engine for reducing signal crosstalk effects within a data signal

PatentInactiveUS7020402B2

Innovation

- A crosstalk compensation engine is introduced, comprising input and output signal terminals and crosstalk compensation circuitry that processes demultiplexed data signals to significantly reduce signal crosstalk products by canceling interference signals from adjacent channels, using combinations of signal combiners, nonlinear signal processors, and adaptive signal slicers to mitigate DWDM, FWM, and XPM effects.

Manufacturing Process Optimization for Signal Stability

Manufacturing process optimization represents a critical pathway for achieving enhanced signal stability in forksheet arrays, requiring systematic refinement of fabrication techniques and quality control measures. The inherent complexity of forksheet transistor structures demands precise manufacturing protocols that address both structural integrity and electrical performance parameters simultaneously.

Process parameter standardization emerges as a fundamental requirement for consistent signal performance across forksheet arrays. Critical manufacturing variables including etch depth uniformity, sidewall angle control, and surface roughness minimization must be maintained within stringent tolerances to prevent signal degradation. Advanced process control systems utilizing real-time monitoring and feedback mechanisms enable manufacturers to detect and correct deviations before they impact device performance.

Thermal management during fabrication stages significantly influences signal stability outcomes in forksheet devices. Optimized annealing profiles and temperature ramping protocols help minimize stress-induced defects that contribute to signal instability. Controlled atmosphere processing environments prevent contamination and oxidation effects that can degrade electrical characteristics over time.

Material deposition techniques require careful optimization to ensure uniform coverage and consistent electrical properties across forksheet structures. Atomic layer deposition and chemical vapor deposition parameters must be fine-tuned to achieve conformal coating on complex three-dimensional geometries while maintaining precise thickness control. These optimizations directly impact carrier mobility and reduce parasitic effects that cause signal fluctuations.

Lithography process enhancements focus on achieving superior pattern fidelity and dimensional control essential for stable device operation. Advanced exposure techniques, including multiple patterning strategies and optimized resist formulations, enable manufacturers to achieve the precise geometries required for consistent electrical performance across large-scale arrays.

Quality assurance protocols incorporating in-line metrology and statistical process control methodologies ensure manufacturing consistency and early detection of process drift. Comprehensive testing at multiple fabrication stages allows for rapid identification and correction of issues that could compromise signal stability in the final device arrays.

Process parameter standardization emerges as a fundamental requirement for consistent signal performance across forksheet arrays. Critical manufacturing variables including etch depth uniformity, sidewall angle control, and surface roughness minimization must be maintained within stringent tolerances to prevent signal degradation. Advanced process control systems utilizing real-time monitoring and feedback mechanisms enable manufacturers to detect and correct deviations before they impact device performance.

Thermal management during fabrication stages significantly influences signal stability outcomes in forksheet devices. Optimized annealing profiles and temperature ramping protocols help minimize stress-induced defects that contribute to signal instability. Controlled atmosphere processing environments prevent contamination and oxidation effects that can degrade electrical characteristics over time.

Material deposition techniques require careful optimization to ensure uniform coverage and consistent electrical properties across forksheet structures. Atomic layer deposition and chemical vapor deposition parameters must be fine-tuned to achieve conformal coating on complex three-dimensional geometries while maintaining precise thickness control. These optimizations directly impact carrier mobility and reduce parasitic effects that cause signal fluctuations.

Lithography process enhancements focus on achieving superior pattern fidelity and dimensional control essential for stable device operation. Advanced exposure techniques, including multiple patterning strategies and optimized resist formulations, enable manufacturers to achieve the precise geometries required for consistent electrical performance across large-scale arrays.

Quality assurance protocols incorporating in-line metrology and statistical process control methodologies ensure manufacturing consistency and early detection of process drift. Comprehensive testing at multiple fabrication stages allows for rapid identification and correction of issues that could compromise signal stability in the final device arrays.

Quality Control Standards for Forksheet Array Performance

Establishing comprehensive quality control standards for forksheet array performance requires a multi-layered approach that addresses both manufacturing consistency and operational reliability. These standards must encompass electrical characteristics, structural integrity, and long-term stability metrics to ensure optimal device performance across varying operational conditions.

The foundation of quality control begins with electrical parameter specifications that define acceptable ranges for key performance indicators. Critical metrics include threshold voltage uniformity across array elements, subthreshold swing consistency, and drain-induced barrier lowering characteristics. Statistical process control methods should be implemented to monitor these parameters, with control limits set at three standard deviations from target values to maintain manufacturing yield while ensuring performance reliability.

Structural quality assessment forms another crucial component of the standards framework. This includes dimensional tolerances for fin width, gate pitch, and contact alignment, which directly impact electrical performance and signal stability. Advanced metrology techniques such as critical dimension scanning electron microscopy and atomic force microscopy should be employed to verify conformance to specified tolerances, typically maintained within ±5% of nominal values.

Environmental stress testing protocols constitute an essential element of quality standards, evaluating device performance under accelerated aging conditions. Temperature cycling tests between -40°C and 125°C, humidity exposure at 85% relative humidity and 85°C, and bias temperature instability assessments should be conducted to validate long-term reliability. These tests help identify potential failure modes and establish confidence intervals for operational lifetime predictions.

Process variation monitoring requires implementation of statistical sampling plans that capture both within-wafer and wafer-to-wafer variations. Control charts tracking key process parameters such as etch uniformity, deposition thickness, and implant dose distribution provide early warning indicators of process drift that could compromise array performance.

Acceptance criteria should incorporate both absolute performance thresholds and relative matching requirements between array elements. Signal-to-noise ratio specifications, typically exceeding 40 dB for high-performance applications, ensure adequate signal integrity. Additionally, matching tolerances between adjacent elements should be maintained within 2% to minimize cross-talk and interference effects that contribute to signal instability.

The foundation of quality control begins with electrical parameter specifications that define acceptable ranges for key performance indicators. Critical metrics include threshold voltage uniformity across array elements, subthreshold swing consistency, and drain-induced barrier lowering characteristics. Statistical process control methods should be implemented to monitor these parameters, with control limits set at three standard deviations from target values to maintain manufacturing yield while ensuring performance reliability.

Structural quality assessment forms another crucial component of the standards framework. This includes dimensional tolerances for fin width, gate pitch, and contact alignment, which directly impact electrical performance and signal stability. Advanced metrology techniques such as critical dimension scanning electron microscopy and atomic force microscopy should be employed to verify conformance to specified tolerances, typically maintained within ±5% of nominal values.

Environmental stress testing protocols constitute an essential element of quality standards, evaluating device performance under accelerated aging conditions. Temperature cycling tests between -40°C and 125°C, humidity exposure at 85% relative humidity and 85°C, and bias temperature instability assessments should be conducted to validate long-term reliability. These tests help identify potential failure modes and establish confidence intervals for operational lifetime predictions.

Process variation monitoring requires implementation of statistical sampling plans that capture both within-wafer and wafer-to-wafer variations. Control charts tracking key process parameters such as etch uniformity, deposition thickness, and implant dose distribution provide early warning indicators of process drift that could compromise array performance.

Acceptance criteria should incorporate both absolute performance thresholds and relative matching requirements between array elements. Signal-to-noise ratio specifications, typically exceeding 40 dB for high-performance applications, ensure adequate signal integrity. Additionally, matching tolerances between adjacent elements should be maintained within 2% to minimize cross-talk and interference effects that contribute to signal instability.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!