Analyzing TSV Benefits in Distributed Computing Platforms

APR 15, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

TSV Technology Background and Computing Platform Goals

Through-Silicon Via (TSV) technology represents a revolutionary advancement in semiconductor packaging and interconnect solutions, fundamentally transforming how electronic components communicate within complex systems. This three-dimensional interconnect technology enables vertical electrical connections through silicon substrates, creating direct pathways between stacked dies or chips. Unlike traditional wire bonding or flip-chip connections that rely on horizontal routing around chip perimeters, TSV creates perpendicular channels filled with conductive materials, typically copper, that penetrate through the silicon wafer thickness.

The evolution of TSV technology stems from the semiconductor industry's relentless pursuit of Moore's Law continuation amid physical scaling limitations. As transistor dimensions approach atomic scales, traditional two-dimensional scaling faces increasing challenges including power density, heat dissipation, and manufacturing complexity. TSV technology emerged as a viable solution to extend performance improvements through vertical integration rather than continued horizontal miniaturization.

In distributed computing platforms, TSV technology addresses critical architectural challenges that have historically limited system performance and efficiency. Traditional computing architectures suffer from the "memory wall" phenomenon, where data movement between processing units and memory hierarchies creates significant latency and energy consumption bottlenecks. The physical separation between different functional blocks in conventional packaging approaches exacerbates these issues, particularly in high-performance computing environments where massive parallel processing demands rapid data exchange.

The primary technological objective of implementing TSV in distributed computing platforms centers on achieving ultra-low latency interconnects between heterogeneous computing elements. This includes enabling seamless integration of processors, memory modules, accelerators, and specialized computing units within compact three-dimensional architectures. By reducing interconnect distances from millimeters to micrometers, TSV technology promises to dramatically decrease signal propagation delays while simultaneously reducing power consumption associated with data transmission.

Furthermore, TSV technology aims to enable unprecedented levels of bandwidth density in distributed computing systems. Traditional interconnect solutions face fundamental limitations in achieving the data throughput requirements of modern parallel computing workloads. The vertical integration capabilities of TSV allow for thousands of parallel connections within minimal footprint areas, potentially delivering bandwidth improvements of several orders of magnitude compared to conventional approaches.

The strategic implementation of TSV technology in distributed computing platforms also targets enhanced thermal management and system reliability. By enabling more efficient heat dissipation pathways and reducing the overall system footprint, TSV-based architectures can achieve better thermal characteristics while maintaining high computational density. This technological approach aligns with the growing demands for energy-efficient computing solutions in data centers and edge computing applications.

The evolution of TSV technology stems from the semiconductor industry's relentless pursuit of Moore's Law continuation amid physical scaling limitations. As transistor dimensions approach atomic scales, traditional two-dimensional scaling faces increasing challenges including power density, heat dissipation, and manufacturing complexity. TSV technology emerged as a viable solution to extend performance improvements through vertical integration rather than continued horizontal miniaturization.

In distributed computing platforms, TSV technology addresses critical architectural challenges that have historically limited system performance and efficiency. Traditional computing architectures suffer from the "memory wall" phenomenon, where data movement between processing units and memory hierarchies creates significant latency and energy consumption bottlenecks. The physical separation between different functional blocks in conventional packaging approaches exacerbates these issues, particularly in high-performance computing environments where massive parallel processing demands rapid data exchange.

The primary technological objective of implementing TSV in distributed computing platforms centers on achieving ultra-low latency interconnects between heterogeneous computing elements. This includes enabling seamless integration of processors, memory modules, accelerators, and specialized computing units within compact three-dimensional architectures. By reducing interconnect distances from millimeters to micrometers, TSV technology promises to dramatically decrease signal propagation delays while simultaneously reducing power consumption associated with data transmission.

Furthermore, TSV technology aims to enable unprecedented levels of bandwidth density in distributed computing systems. Traditional interconnect solutions face fundamental limitations in achieving the data throughput requirements of modern parallel computing workloads. The vertical integration capabilities of TSV allow for thousands of parallel connections within minimal footprint areas, potentially delivering bandwidth improvements of several orders of magnitude compared to conventional approaches.

The strategic implementation of TSV technology in distributed computing platforms also targets enhanced thermal management and system reliability. By enabling more efficient heat dissipation pathways and reducing the overall system footprint, TSV-based architectures can achieve better thermal characteristics while maintaining high computational density. This technological approach aligns with the growing demands for energy-efficient computing solutions in data centers and edge computing applications.

Market Demand for Advanced Distributed Computing Solutions

The distributed computing market is experiencing unprecedented growth driven by the exponential increase in data generation and the need for real-time processing capabilities. Organizations across industries are generating massive datasets that require sophisticated computational architectures to extract meaningful insights and maintain competitive advantages. This surge in data complexity has created substantial demand for advanced distributed computing solutions that can efficiently handle parallel processing workloads.

Cloud service providers represent the largest segment of demand for advanced distributed computing technologies. Major hyperscale data centers require architectures that can support millions of concurrent users while maintaining low latency and high throughput. The integration of TSV technology in these environments addresses critical bottlenecks in inter-processor communication and memory access patterns that traditional architectures struggle to resolve efficiently.

Artificial intelligence and machine learning applications constitute another significant demand driver. Deep learning workloads require massive parallel processing capabilities with high-bandwidth memory access and minimal communication overhead between processing units. TSV-enabled distributed systems offer substantial advantages in training large language models and neural networks by reducing data movement costs and improving overall system efficiency.

Financial services organizations increasingly demand high-performance computing solutions for algorithmic trading, risk analysis, and fraud detection systems. These applications require microsecond-level response times and the ability to process thousands of transactions simultaneously. Advanced distributed computing platforms with TSV integration provide the necessary performance characteristics to meet these stringent requirements.

Scientific computing and research institutions drive demand for specialized distributed computing solutions capable of handling complex simulations and modeling tasks. Climate modeling, pharmaceutical research, and materials science applications require sustained computational performance across distributed nodes with efficient data sharing capabilities.

The telecommunications industry faces growing pressure to support edge computing deployments and 5G network infrastructure. These applications demand distributed computing solutions that can operate efficiently in resource-constrained environments while maintaining high reliability and performance standards. TSV technology enables more compact and efficient processing nodes suitable for edge deployment scenarios.

Enterprise digital transformation initiatives continue to fuel demand for scalable distributed computing platforms. Organizations migrating legacy systems to modern architectures require solutions that can seamlessly integrate with existing infrastructure while providing enhanced performance and scalability characteristics for future growth requirements.

Cloud service providers represent the largest segment of demand for advanced distributed computing technologies. Major hyperscale data centers require architectures that can support millions of concurrent users while maintaining low latency and high throughput. The integration of TSV technology in these environments addresses critical bottlenecks in inter-processor communication and memory access patterns that traditional architectures struggle to resolve efficiently.

Artificial intelligence and machine learning applications constitute another significant demand driver. Deep learning workloads require massive parallel processing capabilities with high-bandwidth memory access and minimal communication overhead between processing units. TSV-enabled distributed systems offer substantial advantages in training large language models and neural networks by reducing data movement costs and improving overall system efficiency.

Financial services organizations increasingly demand high-performance computing solutions for algorithmic trading, risk analysis, and fraud detection systems. These applications require microsecond-level response times and the ability to process thousands of transactions simultaneously. Advanced distributed computing platforms with TSV integration provide the necessary performance characteristics to meet these stringent requirements.

Scientific computing and research institutions drive demand for specialized distributed computing solutions capable of handling complex simulations and modeling tasks. Climate modeling, pharmaceutical research, and materials science applications require sustained computational performance across distributed nodes with efficient data sharing capabilities.

The telecommunications industry faces growing pressure to support edge computing deployments and 5G network infrastructure. These applications demand distributed computing solutions that can operate efficiently in resource-constrained environments while maintaining high reliability and performance standards. TSV technology enables more compact and efficient processing nodes suitable for edge deployment scenarios.

Enterprise digital transformation initiatives continue to fuel demand for scalable distributed computing platforms. Organizations migrating legacy systems to modern architectures require solutions that can seamlessly integrate with existing infrastructure while providing enhanced performance and scalability characteristics for future growth requirements.

Current TSV Implementation Status and Technical Challenges

Through-Silicon Via (TSV) technology has achieved significant maturity in memory stacking applications, particularly in High Bandwidth Memory (HBM) and 3D NAND flash implementations. Major semiconductor manufacturers including Samsung, SK Hynix, and Micron have successfully deployed TSV-based solutions in production environments. However, the adoption of TSV technology in distributed computing platforms remains in early developmental stages, with most implementations confined to research laboratories and prototype systems.

Current TSV implementations in distributed computing primarily focus on processor-memory integration and heterogeneous chip stacking. Intel's Foveros technology and AMD's 3D V-Cache represent notable commercial attempts to leverage TSV for computing applications. These implementations demonstrate TSV's capability to provide high-density vertical interconnections with significantly reduced latency compared to traditional wire bonding or flip-chip connections.

The manufacturing complexity of TSV technology presents substantial challenges for widespread adoption in distributed computing platforms. Deep reactive ion etching processes required for via formation demand precise control over aspect ratios, typically ranging from 10:1 to 20:1. Achieving uniform via profiles across large wafers while maintaining acceptable yield rates remains technically demanding, particularly for computing chips with diverse thermal and electrical requirements.

Thermal management emerges as a critical challenge in TSV-enabled distributed computing systems. The vertical stacking of active computing elements creates concentrated heat generation zones that traditional cooling solutions struggle to address effectively. Thermal coupling between stacked dies can lead to performance degradation and reliability issues, requiring innovative cooling architectures and thermal interface materials.

Electrical design challenges include signal integrity maintenance across vertical interconnections and power delivery optimization. TSV parasitic effects, including capacitance and inductance variations, can significantly impact high-frequency signal transmission essential for distributed computing applications. Additionally, the mechanical stress induced by TSV structures during thermal cycling can affect long-term reliability, particularly in data center environments with frequent temperature fluctuations.

Cost considerations remain a significant barrier to TSV adoption in distributed computing platforms. The additional processing steps, specialized equipment requirements, and reduced yield rates associated with TSV manufacturing substantially increase production costs compared to conventional 2D integration approaches. Current industry estimates suggest TSV implementation adds 15-30% to overall manufacturing costs, making economic justification challenging for many distributed computing applications.

Current TSV implementations in distributed computing primarily focus on processor-memory integration and heterogeneous chip stacking. Intel's Foveros technology and AMD's 3D V-Cache represent notable commercial attempts to leverage TSV for computing applications. These implementations demonstrate TSV's capability to provide high-density vertical interconnections with significantly reduced latency compared to traditional wire bonding or flip-chip connections.

The manufacturing complexity of TSV technology presents substantial challenges for widespread adoption in distributed computing platforms. Deep reactive ion etching processes required for via formation demand precise control over aspect ratios, typically ranging from 10:1 to 20:1. Achieving uniform via profiles across large wafers while maintaining acceptable yield rates remains technically demanding, particularly for computing chips with diverse thermal and electrical requirements.

Thermal management emerges as a critical challenge in TSV-enabled distributed computing systems. The vertical stacking of active computing elements creates concentrated heat generation zones that traditional cooling solutions struggle to address effectively. Thermal coupling between stacked dies can lead to performance degradation and reliability issues, requiring innovative cooling architectures and thermal interface materials.

Electrical design challenges include signal integrity maintenance across vertical interconnections and power delivery optimization. TSV parasitic effects, including capacitance and inductance variations, can significantly impact high-frequency signal transmission essential for distributed computing applications. Additionally, the mechanical stress induced by TSV structures during thermal cycling can affect long-term reliability, particularly in data center environments with frequent temperature fluctuations.

Cost considerations remain a significant barrier to TSV adoption in distributed computing platforms. The additional processing steps, specialized equipment requirements, and reduced yield rates associated with TSV manufacturing substantially increase production costs compared to conventional 2D integration approaches. Current industry estimates suggest TSV implementation adds 15-30% to overall manufacturing costs, making economic justification challenging for many distributed computing applications.

Existing TSV Solutions for Distributed Computing Platforms

01 Enhanced electrical performance and reduced signal path length

Through-silicon via (TSV) technology enables vertical interconnections through the silicon substrate, significantly reducing signal path length compared to traditional wire bonding. This results in improved electrical performance including reduced resistance, capacitance, and inductance. The shorter interconnect paths lead to faster signal transmission, lower power consumption, and enhanced overall circuit performance. TSV structures provide superior high-frequency characteristics and enable higher bandwidth for data transmission.- Enhanced electrical performance and reduced signal path length: Through-silicon via (TSV) technology enables vertical interconnections through the silicon substrate, significantly reducing signal path length compared to traditional wire bonding. This results in improved electrical performance including reduced resistance, capacitance, and inductance. The shorter interconnect paths lead to faster signal transmission, lower power consumption, and enhanced overall circuit performance. TSV structures facilitate high-speed data transfer between stacked dies while minimizing signal delay and crosstalk.

- Increased packaging density and miniaturization: TSV technology enables three-dimensional integration of semiconductor devices, allowing multiple dies to be stacked vertically in a compact footprint. This vertical stacking approach significantly increases packaging density compared to planar configurations, enabling more functionality within a smaller area. The reduced form factor is particularly beneficial for mobile devices, wearables, and other space-constrained applications. This miniaturization capability supports the continued scaling of electronic systems while maintaining or improving performance characteristics.

- Improved thermal management capabilities: TSV structures provide efficient thermal conduction paths through the silicon substrate, facilitating heat dissipation from stacked die configurations. The vertical thermal pathways enable more effective heat removal compared to traditional lateral heat spreading methods. This improved thermal management is critical for high-power applications and densely packed three-dimensional integrated circuits. The enhanced heat dissipation capability helps maintain optimal operating temperatures, improving reliability and extending device lifetime.

- Heterogeneous integration and system flexibility: TSV technology enables the integration of different types of semiconductor devices, such as logic, memory, sensors, and analog components, within a single three-dimensional package. This heterogeneous integration capability allows designers to combine dies manufactured using different process technologies and materials, optimizing each component independently. The flexibility to mix and match various functional blocks enables the creation of highly customized system-in-package solutions tailored to specific application requirements. This approach reduces development time and costs while improving overall system performance.

- Reduced power consumption and improved bandwidth: The shorter interconnect distances provided by TSV technology result in lower power consumption for signal transmission between stacked dies. Reduced parasitic capacitance and resistance in vertical connections minimize energy loss during data transfer. Additionally, TSV structures support higher bandwidth communication between dies through increased interconnect density and parallel data paths. The combination of lower power consumption and higher bandwidth makes TSV technology particularly advantageous for memory-intensive applications and high-performance computing systems.

02 Increased packaging density and miniaturization

TSV technology enables three-dimensional stacking of multiple dies or chips, allowing for significant reduction in package footprint and overall device size. This vertical integration approach maximizes space utilization and enables higher component density within a smaller form factor. The technology facilitates the creation of compact, high-performance packages suitable for applications requiring miniaturization. Multiple functional layers can be integrated vertically, reducing the horizontal space requirements substantially.Expand Specific Solutions03 Improved thermal management capabilities

TSV structures provide efficient heat dissipation paths through the silicon substrate, enabling better thermal management in stacked die configurations. The vertical interconnects facilitate heat transfer from internal layers to external heat sinks or cooling systems. This thermal advantage is particularly beneficial for high-power applications and densely packed integrated circuits. The technology allows for more uniform temperature distribution across stacked components, reducing hot spots and improving reliability.Expand Specific Solutions04 Enhanced heterogeneous integration

TSV technology enables the integration of different types of chips or dies manufactured using different process technologies or materials within a single package. This allows for combining logic, memory, sensors, and other functional components in a vertical stack, optimizing each layer for its specific function. The approach facilitates the integration of components that would be difficult or impossible to manufacture on a single die. This heterogeneous integration capability enables system-level optimization and improved overall performance.Expand Specific Solutions05 Cost reduction and yield improvement

TSV technology can reduce overall manufacturing costs by enabling known good die testing before stacking, improving yield rates. The ability to stack smaller dies instead of creating one large monolithic die reduces the impact of defects and improves manufacturing efficiency. The technology allows for more flexible manufacturing approaches and can reduce the need for expensive large-area substrates. Additionally, the reduced interconnect length and improved performance can lead to lower system-level costs through reduced power consumption and simplified cooling requirements.Expand Specific Solutions

Key Players in TSV and Distributed Computing Industry

The TSV (Through-Silicon Via) technology in distributed computing platforms represents a rapidly evolving competitive landscape characterized by significant market growth and diverse technological maturity levels across key players. The industry is transitioning from early adoption to mainstream implementation, driven by increasing demand for high-performance computing and data center optimization. Major semiconductor companies like Samsung Electronics, AMD, Qualcomm, and Micron Technology lead in advanced TSV integration for memory and processing solutions, while infrastructure providers including VMware, IBM, and Red Hat focus on software optimization for TSV-enabled hardware. Chinese companies such as Huawei, China Mobile, and Inspur are aggressively investing in TSV research for telecommunications and cloud computing applications. The market demonstrates varying technological readiness, with established players like Samsung and Micron achieving commercial-scale TSV production, while emerging companies and research institutions including Xidian University are developing next-generation applications, creating a dynamic ecosystem spanning hardware manufacturing to distributed system optimization.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced TSV technology for 3D memory architectures, particularly in their High Bandwidth Memory (HBM) products. Their TSV implementation enables vertical stacking of memory dies with through-silicon connections that provide significantly higher bandwidth compared to traditional wire bonding. In distributed computing platforms, Samsung's TSV-enabled memory solutions offer reduced latency and improved data throughput by minimizing the physical distance between processing units and memory layers. The company has achieved TSV diameters as small as 5 micrometers with aspect ratios exceeding 10:1, enabling dense vertical integration. Their TSV technology supports multi-gigabit data rates per connection, making it particularly suitable for high-performance computing clusters and data center applications where memory bandwidth is critical for distributed workload processing.

Strengths: Industry-leading TSV manufacturing capabilities, proven HBM integration, high bandwidth density. Weaknesses: High manufacturing costs, complex thermal management requirements in stacked configurations.

Advanced Micro Devices, Inc.

Technical Solution: AMD leverages TSV technology primarily through their integration with HBM memory in high-performance GPUs and APUs used in distributed computing environments. Their approach focuses on utilizing TSV-enabled memory stacks to create wider memory buses that can handle the massive parallel processing demands of distributed workloads. AMD's implementation allows for memory bandwidth exceeding 1 TB/s in their flagship products, which is crucial for distributed machine learning and scientific computing applications. The TSV connections enable shorter signal paths between the GPU cores and memory, reducing power consumption and improving overall system efficiency. In distributed computing platforms, this translates to better performance per watt ratios and reduced cooling requirements across compute nodes.

Strengths: Excellent integration with high-performance computing applications, proven scalability in distributed environments. Weaknesses: Dependency on external memory suppliers for TSV technology, limited control over TSV manufacturing processes.

Core TSV Innovations for Computing Performance Enhancement

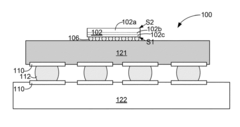

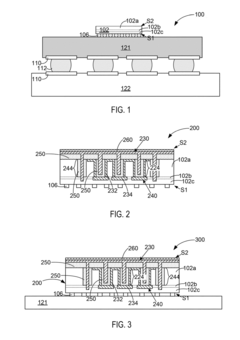

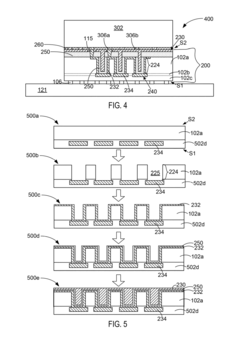

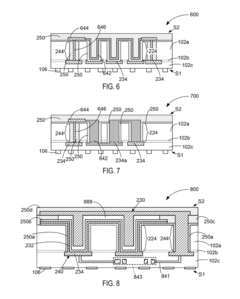

Through-silicon via (TSV)-based devices and associated techniques and configurations

PatentActiveUS20150255372A1

Innovation

- The implementation of through-silicon via (TSV)-based devices, including capacitors, resistors, and resonators, which utilize TSV structures extending through the bulk semiconductor material, electrically insulative materials, and electrode or resistor materials within these structures to provide enhanced capacitance and resistance while reducing footprint and inductance.

Systems and methods for improved through-silicon-vias

PatentActiveUS20190311973A1

Innovation

- Modifying the sidewall of TSVs to protrude into the silicon substrate and introducing voids within the TSVs to absorb and distribute stress, thereby reducing the stress profile on the interconnects without compromising electrical properties.

Manufacturing Standards and Quality Control for TSV

Manufacturing standards for TSV technology in distributed computing platforms have evolved significantly to address the unique requirements of high-performance interconnects. The semiconductor industry has established comprehensive frameworks that encompass dimensional tolerances, electrical specifications, and reliability parameters specifically tailored for TSV applications in data centers and cloud computing environments.

Current manufacturing standards primarily focus on via diameter consistency, typically ranging from 5 to 50 micrometers, with aspect ratios between 5:1 and 20:1 depending on the application requirements. Critical dimensional parameters include via sidewall angle control within ±2 degrees, copper fill void density below 0.1%, and inter-via spacing uniformity to prevent electrical crosstalk in high-density configurations.

Quality control methodologies have been standardized around multi-stage inspection protocols that integrate both in-line and offline measurement techniques. Advanced metrology systems employ high-resolution X-ray computed tomography for void detection, scanning electron microscopy for sidewall profile analysis, and electrical test structures for resistance and capacitance verification across wafer lots.

Thermal cycling standards specifically address the operational environment of distributed computing platforms, where TSVs must withstand temperature variations from -40°C to 125°C over millions of cycles. Standardized stress testing protocols evaluate solder joint integrity, copper migration resistance, and dielectric breakdown characteristics under accelerated aging conditions that simulate decades of operational use.

Process control standards mandate statistical process control implementation with real-time monitoring of critical parameters including etch rate uniformity, electroplating current density distribution, and chemical mechanical planarization removal rates. These standards ensure manufacturing repeatability across different foundries and enable supply chain scalability for large-scale distributed computing deployments.

Reliability qualification standards require comprehensive failure mode analysis covering electromigration, thermomechanical stress, and corrosion resistance. Standardized test vehicles incorporate representative circuit patterns and power delivery networks that mirror actual distributed computing workloads, ensuring that laboratory qualification translates effectively to field performance in demanding computational environments.

Current manufacturing standards primarily focus on via diameter consistency, typically ranging from 5 to 50 micrometers, with aspect ratios between 5:1 and 20:1 depending on the application requirements. Critical dimensional parameters include via sidewall angle control within ±2 degrees, copper fill void density below 0.1%, and inter-via spacing uniformity to prevent electrical crosstalk in high-density configurations.

Quality control methodologies have been standardized around multi-stage inspection protocols that integrate both in-line and offline measurement techniques. Advanced metrology systems employ high-resolution X-ray computed tomography for void detection, scanning electron microscopy for sidewall profile analysis, and electrical test structures for resistance and capacitance verification across wafer lots.

Thermal cycling standards specifically address the operational environment of distributed computing platforms, where TSVs must withstand temperature variations from -40°C to 125°C over millions of cycles. Standardized stress testing protocols evaluate solder joint integrity, copper migration resistance, and dielectric breakdown characteristics under accelerated aging conditions that simulate decades of operational use.

Process control standards mandate statistical process control implementation with real-time monitoring of critical parameters including etch rate uniformity, electroplating current density distribution, and chemical mechanical planarization removal rates. These standards ensure manufacturing repeatability across different foundries and enable supply chain scalability for large-scale distributed computing deployments.

Reliability qualification standards require comprehensive failure mode analysis covering electromigration, thermomechanical stress, and corrosion resistance. Standardized test vehicles incorporate representative circuit patterns and power delivery networks that mirror actual distributed computing workloads, ensuring that laboratory qualification translates effectively to field performance in demanding computational environments.

Thermal Management Considerations in TSV-Based Systems

Thermal management represents one of the most critical challenges in TSV-based distributed computing systems, as the three-dimensional integration inherently creates complex heat dissipation pathways that differ significantly from traditional planar architectures. The vertical interconnects introduce unique thermal characteristics that must be carefully considered during system design and operation.

TSVs themselves act as thermal conduits, creating both opportunities and challenges for heat management. The copper-filled vias provide efficient thermal pathways between stacked dies, enabling heat generated in lower layers to be conducted upward through the silicon substrate. However, this vertical heat transfer can create thermal hotspots at via locations, particularly when multiple high-power components are vertically aligned across different layers.

The thermal resistance characteristics of TSV structures vary significantly based on via diameter, pitch, and fill material properties. Larger diameter TSVs generally provide better thermal conductivity but consume more silicon real estate, creating design trade-offs between thermal performance and integration density. The thermal interface materials between stacked dies also play crucial roles in overall system thermal behavior.

Power density distribution becomes increasingly complex in TSV-based systems, as heat generation sources are distributed across multiple vertical layers rather than confined to a single plane. This three-dimensional heat generation pattern requires sophisticated thermal modeling approaches that account for inter-layer thermal coupling effects and the anisotropic thermal properties of the stacked structure.

Cooling solution design must address the challenge of removing heat from internal layers that lack direct access to external cooling surfaces. Traditional heat sink approaches become less effective as heat must travel through multiple material interfaces and silicon layers before reaching the cooling medium. Advanced cooling strategies, including embedded microfluidic channels and through-silicon cooling vias, are being developed to address these limitations.

Temperature gradients across TSV-based systems can create significant thermomechanical stress, particularly at the interfaces between different materials with varying coefficients of thermal expansion. These stress concentrations can lead to reliability issues including via cracking, delamination, and performance degradation over thermal cycling conditions.

Real-time thermal monitoring and dynamic thermal management become essential in TSV-based distributed computing platforms, requiring integrated temperature sensors and adaptive power management algorithms that can respond to thermal conditions across multiple layers simultaneously.

TSVs themselves act as thermal conduits, creating both opportunities and challenges for heat management. The copper-filled vias provide efficient thermal pathways between stacked dies, enabling heat generated in lower layers to be conducted upward through the silicon substrate. However, this vertical heat transfer can create thermal hotspots at via locations, particularly when multiple high-power components are vertically aligned across different layers.

The thermal resistance characteristics of TSV structures vary significantly based on via diameter, pitch, and fill material properties. Larger diameter TSVs generally provide better thermal conductivity but consume more silicon real estate, creating design trade-offs between thermal performance and integration density. The thermal interface materials between stacked dies also play crucial roles in overall system thermal behavior.

Power density distribution becomes increasingly complex in TSV-based systems, as heat generation sources are distributed across multiple vertical layers rather than confined to a single plane. This three-dimensional heat generation pattern requires sophisticated thermal modeling approaches that account for inter-layer thermal coupling effects and the anisotropic thermal properties of the stacked structure.

Cooling solution design must address the challenge of removing heat from internal layers that lack direct access to external cooling surfaces. Traditional heat sink approaches become less effective as heat must travel through multiple material interfaces and silicon layers before reaching the cooling medium. Advanced cooling strategies, including embedded microfluidic channels and through-silicon cooling vias, are being developed to address these limitations.

Temperature gradients across TSV-based systems can create significant thermomechanical stress, particularly at the interfaces between different materials with varying coefficients of thermal expansion. These stress concentrations can lead to reliability issues including via cracking, delamination, and performance degradation over thermal cycling conditions.

Real-time thermal monitoring and dynamic thermal management become essential in TSV-based distributed computing platforms, requiring integrated temperature sensors and adaptive power management algorithms that can respond to thermal conditions across multiple layers simultaneously.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!