EUV Lithography vs Extreme Double Patterning: A Throughput Review

APR 2, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

EUV Lithography and EDP Technology Background and Goals

The semiconductor industry has reached a critical juncture in lithographic technology development, where traditional optical lithography approaches face fundamental physical limitations in achieving sub-10nm manufacturing nodes. Two primary technological pathways have emerged to address these challenges: Extreme Ultraviolet (EUV) lithography and Extreme Double Patterning (EDP) techniques, each representing distinct philosophical approaches to overcoming resolution barriers.

EUV lithography represents a revolutionary leap in semiconductor manufacturing, utilizing 13.5nm wavelength light to achieve unprecedented resolution capabilities. This technology emerged from decades of research into shorter wavelength light sources, promising to simplify complex patterning processes while enabling direct printing of features at advanced nodes. The fundamental principle leverages the inverse relationship between wavelength and achievable resolution, theoretically enabling single-exposure patterning of critical dimensions previously impossible with conventional 193nm immersion lithography.

Extreme Double Patterning evolved as an extension of existing 193nm immersion lithography infrastructure, employing sophisticated multi-exposure techniques to achieve effective resolution enhancement. This approach represents an evolutionary pathway that maximizes existing capital investments while pushing the boundaries of what conventional lithography can accomplish through advanced process engineering and computational lithography techniques.

The historical development trajectory shows EUV technology originating from research initiatives in the 1990s, driven by the recognition that wavelength reduction was essential for continued Moore's Law progression. Meanwhile, double patterning techniques emerged as interim solutions, initially implemented as Litho-Etch-Litho-Etch (LELE) processes before evolving into more sophisticated Self-Aligned Double Patterning (SADP) and Self-Aligned Quadruple Patterning (SAQP) methodologies.

The primary technological goal centers on achieving optimal throughput performance while maintaining manufacturing yield and cost-effectiveness at advanced nodes. EUV technology aims to simplify mask complexity and reduce process steps through single-exposure capability, potentially revolutionizing high-volume manufacturing economics. Conversely, EDP techniques target maximizing existing infrastructure utilization while achieving comparable resolution through innovative process architectures.

Both technologies face distinct challenges in achieving production-worthy throughput levels. EUV systems must overcome source power limitations, photoresist sensitivity constraints, and mask infrastructure complexities. EDP approaches confront overlay accuracy requirements, process complexity multiplication, and yield management across multiple patterning steps, creating fundamentally different optimization landscapes for manufacturing implementation.

EUV lithography represents a revolutionary leap in semiconductor manufacturing, utilizing 13.5nm wavelength light to achieve unprecedented resolution capabilities. This technology emerged from decades of research into shorter wavelength light sources, promising to simplify complex patterning processes while enabling direct printing of features at advanced nodes. The fundamental principle leverages the inverse relationship between wavelength and achievable resolution, theoretically enabling single-exposure patterning of critical dimensions previously impossible with conventional 193nm immersion lithography.

Extreme Double Patterning evolved as an extension of existing 193nm immersion lithography infrastructure, employing sophisticated multi-exposure techniques to achieve effective resolution enhancement. This approach represents an evolutionary pathway that maximizes existing capital investments while pushing the boundaries of what conventional lithography can accomplish through advanced process engineering and computational lithography techniques.

The historical development trajectory shows EUV technology originating from research initiatives in the 1990s, driven by the recognition that wavelength reduction was essential for continued Moore's Law progression. Meanwhile, double patterning techniques emerged as interim solutions, initially implemented as Litho-Etch-Litho-Etch (LELE) processes before evolving into more sophisticated Self-Aligned Double Patterning (SADP) and Self-Aligned Quadruple Patterning (SAQP) methodologies.

The primary technological goal centers on achieving optimal throughput performance while maintaining manufacturing yield and cost-effectiveness at advanced nodes. EUV technology aims to simplify mask complexity and reduce process steps through single-exposure capability, potentially revolutionizing high-volume manufacturing economics. Conversely, EDP techniques target maximizing existing infrastructure utilization while achieving comparable resolution through innovative process architectures.

Both technologies face distinct challenges in achieving production-worthy throughput levels. EUV systems must overcome source power limitations, photoresist sensitivity constraints, and mask infrastructure complexities. EDP approaches confront overlay accuracy requirements, process complexity multiplication, and yield management across multiple patterning steps, creating fundamentally different optimization landscapes for manufacturing implementation.

Market Demand for Advanced Semiconductor Manufacturing

The global semiconductor industry faces unprecedented demand driven by digital transformation across multiple sectors. Advanced manufacturing capabilities have become critical as device miniaturization reaches physical limits, necessitating sophisticated lithography solutions to maintain Moore's Law progression. The proliferation of artificial intelligence, 5G networks, autonomous vehicles, and Internet of Things applications creates substantial pressure for higher-performance chips with smaller geometries.

Leading-edge semiconductor nodes below 10nm represent the fastest-growing segment of the manufacturing market. Major foundries report capacity constraints at advanced nodes, with waiting lists extending beyond traditional planning horizons. This scarcity drives premium pricing and intensifies competition among chip designers for manufacturing slots. The concentration of advanced manufacturing capabilities among a limited number of foundries amplifies the strategic importance of throughput optimization.

Mobile processors, graphics processing units, and data center accelerators constitute primary demand drivers for sub-7nm manufacturing. These applications require exceptional transistor density and performance characteristics achievable only through cutting-edge lithography techniques. The automotive semiconductor market adds complexity with reliability requirements and volume projections that challenge traditional capacity planning models.

Manufacturing economics heavily influence technology adoption decisions. While EUV lithography offers simplified process flows, capital equipment costs and operational complexity create financial barriers. Extreme double patterning presents alternative pathways with different cost structures and throughput characteristics. Foundries must balance customer demands for advanced nodes against capital efficiency and manufacturing yield considerations.

Supply chain resilience concerns following recent global disruptions emphasize the strategic value of manufacturing flexibility. Governments worldwide implement semiconductor manufacturing incentives, creating additional demand for advanced lithography solutions. These policy initiatives accelerate capacity expansion plans and intensify competition for equipment suppliers.

The convergence of high-performance computing and mobile applications drives requirements for heterogeneous integration and advanced packaging technologies. These trends create additional manufacturing steps and complexity, influencing overall throughput requirements and equipment utilization strategies across the semiconductor value chain.

Leading-edge semiconductor nodes below 10nm represent the fastest-growing segment of the manufacturing market. Major foundries report capacity constraints at advanced nodes, with waiting lists extending beyond traditional planning horizons. This scarcity drives premium pricing and intensifies competition among chip designers for manufacturing slots. The concentration of advanced manufacturing capabilities among a limited number of foundries amplifies the strategic importance of throughput optimization.

Mobile processors, graphics processing units, and data center accelerators constitute primary demand drivers for sub-7nm manufacturing. These applications require exceptional transistor density and performance characteristics achievable only through cutting-edge lithography techniques. The automotive semiconductor market adds complexity with reliability requirements and volume projections that challenge traditional capacity planning models.

Manufacturing economics heavily influence technology adoption decisions. While EUV lithography offers simplified process flows, capital equipment costs and operational complexity create financial barriers. Extreme double patterning presents alternative pathways with different cost structures and throughput characteristics. Foundries must balance customer demands for advanced nodes against capital efficiency and manufacturing yield considerations.

Supply chain resilience concerns following recent global disruptions emphasize the strategic value of manufacturing flexibility. Governments worldwide implement semiconductor manufacturing incentives, creating additional demand for advanced lithography solutions. These policy initiatives accelerate capacity expansion plans and intensify competition for equipment suppliers.

The convergence of high-performance computing and mobile applications drives requirements for heterogeneous integration and advanced packaging technologies. These trends create additional manufacturing steps and complexity, influencing overall throughput requirements and equipment utilization strategies across the semiconductor value chain.

Current State and Challenges of EUV vs EDP Technologies

EUV lithography has emerged as the leading-edge patterning technology for advanced semiconductor nodes, particularly for 7nm and below. Current EUV systems, primarily ASML's NXE series, operate at 13.5nm wavelength and have achieved production throughput of approximately 170-185 wafers per hour. However, EUV technology faces significant challenges including limited source power, photoresist sensitivity requirements, and mask defectivity issues. The technology requires extremely clean vacuum environments and sophisticated multilayer mirrors, making it capital-intensive with tool costs exceeding $200 million per unit.

Extreme Double Patterning represents a mature extension of 193nm immersion lithography, utilizing multiple exposure and etch steps to achieve sub-40nm pitch capabilities. EDP techniques include Litho-Etch-Litho-Etch (LELE) and Self-Aligned Double Patterning (SADP) approaches. Current EDP systems can achieve throughput rates of 250-300 wafers per hour per scanner, but require multiple processing steps that significantly increase overall cycle time and manufacturing complexity.

The fundamental challenge in EUV adoption centers on source power limitations and photon shot noise. Current EUV sources generate approximately 250W of usable power, constraining throughput for the most advanced resist systems. Stochastic effects become pronounced at smaller feature sizes, requiring higher photon doses that further impact productivity. Additionally, EUV pellicle technology remains immature, forcing fabs to operate without protective pellicles and implement stringent contamination control measures.

EDP technologies face escalating overlay and edge placement error challenges as pitch requirements tighten. Multi-patterning introduces cumulative overlay errors that become increasingly difficult to control at advanced nodes. Process complexity increases exponentially with each additional patterning step, impacting yield and manufacturing cost. Critical dimension uniformity across multiple exposures presents ongoing challenges for process window optimization.

Geographically, EUV development is concentrated in the Netherlands (ASML), with supporting ecosystem development in Taiwan, South Korea, and the United States. EDP technology benefits from established 193nm infrastructure distributed globally across major semiconductor manufacturing regions. The supply chain maturity differs significantly, with EDP leveraging decades of ArF immersion lithography optimization while EUV requires entirely new infrastructure and expertise development.

Current industry adoption shows a hybrid approach, with leading foundries implementing EUV for critical layers while maintaining EDP for less critical patterning steps. This strategy balances throughput requirements with technical capabilities, as EUV technology continues maturing toward higher source power and improved resist performance targets.

Extreme Double Patterning represents a mature extension of 193nm immersion lithography, utilizing multiple exposure and etch steps to achieve sub-40nm pitch capabilities. EDP techniques include Litho-Etch-Litho-Etch (LELE) and Self-Aligned Double Patterning (SADP) approaches. Current EDP systems can achieve throughput rates of 250-300 wafers per hour per scanner, but require multiple processing steps that significantly increase overall cycle time and manufacturing complexity.

The fundamental challenge in EUV adoption centers on source power limitations and photon shot noise. Current EUV sources generate approximately 250W of usable power, constraining throughput for the most advanced resist systems. Stochastic effects become pronounced at smaller feature sizes, requiring higher photon doses that further impact productivity. Additionally, EUV pellicle technology remains immature, forcing fabs to operate without protective pellicles and implement stringent contamination control measures.

EDP technologies face escalating overlay and edge placement error challenges as pitch requirements tighten. Multi-patterning introduces cumulative overlay errors that become increasingly difficult to control at advanced nodes. Process complexity increases exponentially with each additional patterning step, impacting yield and manufacturing cost. Critical dimension uniformity across multiple exposures presents ongoing challenges for process window optimization.

Geographically, EUV development is concentrated in the Netherlands (ASML), with supporting ecosystem development in Taiwan, South Korea, and the United States. EDP technology benefits from established 193nm infrastructure distributed globally across major semiconductor manufacturing regions. The supply chain maturity differs significantly, with EDP leveraging decades of ArF immersion lithography optimization while EUV requires entirely new infrastructure and expertise development.

Current industry adoption shows a hybrid approach, with leading foundries implementing EUV for critical layers while maintaining EDP for less critical patterning steps. This strategy balances throughput requirements with technical capabilities, as EUV technology continues maturing toward higher source power and improved resist performance targets.

Current Throughput Solutions in EUV and EDP

01 EUV lithography source optimization and power enhancement

Extreme ultraviolet lithography requires high-power light sources to achieve adequate throughput for semiconductor manufacturing. Technologies focus on optimizing EUV source power, improving collection efficiency of generated EUV radiation, and enhancing the stability of plasma-based or laser-produced plasma sources. Advanced source configurations and thermal management systems enable higher photon flux delivery to wafer surfaces, directly impacting exposure throughput and manufacturing efficiency.- EUV lithography source optimization and power enhancement: Extreme ultraviolet lithography requires high-power light sources to achieve adequate throughput for semiconductor manufacturing. Techniques focus on optimizing EUV source power, improving collection efficiency of generated EUV radiation, and enhancing the stability of plasma-based or laser-produced plasma sources. Advanced source configurations and thermal management systems enable higher photon flux delivery to wafer exposure systems, directly impacting manufacturing throughput capabilities.

- Double patterning decomposition and layout optimization: Double patterning techniques involve decomposing circuit patterns into multiple exposure masks to achieve finer feature resolution beyond single exposure limits. Advanced algorithms analyze layout designs to determine optimal pattern splitting strategies, minimize conflicts, and reduce stitching errors. Computational methods evaluate coloring schemes and mask assignment to ensure manufacturability while maintaining design intent and electrical connectivity requirements.

- Photoresist materials and processing for EUV lithography: Specialized photoresist formulations designed for extreme ultraviolet wavelengths enable improved sensitivity and resolution. Chemical compositions are optimized to respond efficiently to EUV photon absorption while maintaining line edge roughness control and pattern fidelity. Processing parameters including exposure dose, post-exposure bake conditions, and development chemistry are tailored to maximize throughput without compromising critical dimension uniformity.

- Mask and reticle technologies for multiple patterning: Advanced photomask designs incorporate phase-shifting elements, optical proximity correction features, and sub-resolution assist features to enhance pattern transfer fidelity in multiple patterning schemes. Mask fabrication techniques address the stringent requirements for overlay accuracy and defect control necessary for double or multiple exposure processes. Inspection and metrology systems ensure mask quality meets the specifications required for high-volume manufacturing throughput.

- Overlay control and alignment systems for multi-patterning: Precise overlay alignment between successive lithography exposures is critical for double patterning success. Advanced metrology systems measure and correct alignment errors in real-time using sophisticated algorithms and feedback mechanisms. Wafer stage positioning systems with nanometer-level accuracy, combined with computational overlay correction models, enable the tight overlay budgets required for multiple patterning processes while maintaining acceptable manufacturing throughput rates.

02 Double patterning decomposition and layout optimization

Double patterning techniques decompose complex circuit patterns into multiple simpler exposures to overcome resolution limitations. Advanced algorithms analyze design layouts to determine optimal pattern splitting strategies, minimizing conflicts and overlay errors. Computational methods evaluate coloring schemes, stitch placement, and mask assignment to ensure manufacturability while maintaining design intent. These optimization approaches are critical for achieving high-density patterns with acceptable defect rates.Expand Specific Solutions03 Photoresist materials and processing for advanced lithography

Specialized photoresist formulations are developed to meet the sensitivity and resolution requirements of extreme ultraviolet and multiple patterning processes. Chemical compositions are optimized for line edge roughness reduction, improved etch resistance, and enhanced pattern fidelity. Processing parameters including exposure dose, post-exposure bake conditions, and development chemistry are tailored to maximize throughput while maintaining critical dimension control across various pattern densities.Expand Specific Solutions04 Overlay metrology and alignment for multi-patterning

Precise overlay control between successive patterning steps is essential for double and multiple patterning schemes. Advanced metrology systems measure alignment accuracy at nanometer scales using optical and computational techniques. Feedback mechanisms adjust exposure tool parameters in real-time to compensate for systematic and random overlay errors. Enhanced alignment mark designs and measurement algorithms improve throughput by reducing measurement time while maintaining accuracy requirements.Expand Specific Solutions05 Computational lithography and mask synthesis

Computational lithography techniques including optical proximity correction and source-mask optimization are adapted for extreme ultraviolet and multiple patterning workflows. Sophisticated simulation models predict imaging performance and guide mask pattern adjustments to compensate for optical effects and process variations. Mask synthesis algorithms generate optimized reticle designs that balance pattern fidelity with manufacturing constraints, enabling higher throughput through reduced iteration cycles and improved process windows.Expand Specific Solutions

Key Players in EUV and Double Patterning Industry

The EUV lithography versus extreme double patterning competition represents a mature semiconductor manufacturing technology landscape at a critical inflection point. The market, valued at over $100 billion globally, is experiencing intense competition between next-generation EUV adoption and optimized multi-patterning approaches. Technology maturity varies significantly across key players: ASML dominates EUV systems with advanced NXE platforms, while equipment manufacturers like Applied Materials, Lam Research, and Tokyo Electron have refined double patterning solutions. Leading foundries including TSMC and Samsung Electronics are implementing both approaches strategically, with TSMC advancing EUV for 7nm and below nodes while maintaining double patterning for cost-sensitive applications. The industry shows clear technological bifurcation, where EUV offers superior resolution but faces throughput and cost challenges, while extreme double patterning provides proven scalability with established supply chains from companies like Nikon, Intel, and SK Hynix driving continued optimization.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has implemented both EUV lithography and extreme double patterning in their advanced node production. For their 7nm and 5nm processes, they utilize EUV for critical layers while maintaining ArF immersion with double patterning for less critical layers to optimize cost and throughput. Their hybrid approach achieves production throughput of over 1000 wafers per day for advanced nodes, balancing the superior resolution of EUV with the higher throughput capabilities of double patterning techniques for different layer requirements.

Strengths: Hybrid approach optimization, high-volume production experience, cost-effective layer assignment strategy. Weaknesses: Complex process integration, higher overall process complexity, dependency on EUV tool availability.

Lam Research Corp.

Technical Solution: Lam Research provides critical etch and deposition equipment for both EUV and double patterning workflows. Their solutions include advanced plasma etch systems optimized for EUV resist processing and multi-patterning applications. For double patterning, they offer SADP and SAQP capable systems with precise CD control and high selectivity etching. Their equipment supports throughput requirements of over 200 wafers per hour for double patterning processes while maintaining the precision needed for EUV resist processing with minimal line edge roughness.

Strengths: Comprehensive equipment portfolio, high-precision processing capabilities, optimized for both technologies. Weaknesses: Equipment-focused rather than complete solution provider, dependency on customer process integration, high equipment costs.

Core Patents in EUV and Extreme Double Patterning

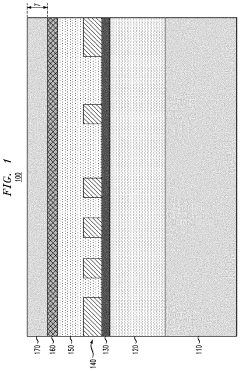

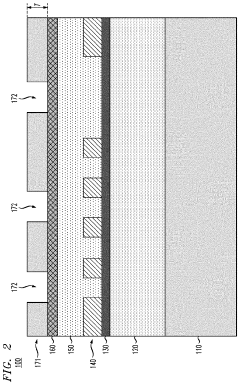

Plasma processing method

PatentActiveUS20220384148A1

Innovation

- A plasma processing method that selectively deposits a deposition film on the mask material by controlling etching parameters to ensure the incubation time of the mask material is shorter than that of the material to be etched, thereby improving etching selectivity and reducing roughness without forming the deposition film on the material to be etched.

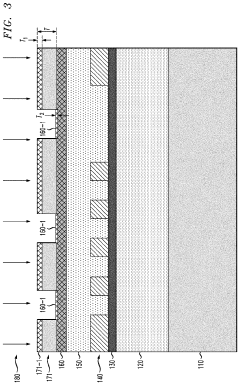

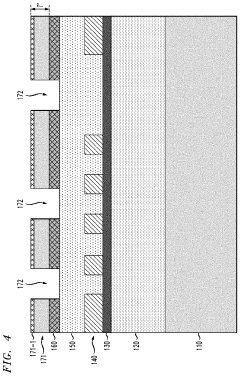

Extreme ultraviolet (EUV) lithography patterning methods utilizing EUV resist hardening

PatentInactiveUS20190384180A1

Innovation

- Implementing a surface-hardened EUV resist mask with an etch-resistant layer formed by a neutral atom beam process that implants chemical or metallic species into the EUV resist mask to enhance etch resistance, allowing for patterning of sub-36 nm pitch features without significant mask thickness reduction.

Supply Chain Dependencies for EUV Equipment

The EUV lithography supply chain represents one of the most complex and concentrated ecosystems in the semiconductor industry, with critical dependencies that significantly impact global chip manufacturing capabilities. ASML holds a monopoly position as the sole supplier of EUV scanners, creating an unprecedented single point of failure in the advanced semiconductor manufacturing process. This concentration stems from the extraordinary technical complexity and capital requirements needed to develop EUV systems, which have effectively prevented other equipment manufacturers from entering this market segment.

The optical components supply chain for EUV systems relies heavily on specialized suppliers with unique capabilities. Zeiss provides the critical multilayer mirrors and optical systems, while companies like Cymer (now part of ASML) supply the laser-produced plasma light sources. These components require extreme precision manufacturing with tolerances measured in picometers, limiting the supplier base to a handful of companies worldwide. The mirrors alone consist of over 100 alternating layers of molybdenum and silicon, manufactured using proprietary deposition techniques that few facilities can replicate.

Critical materials dependencies further constrain the EUV supply chain, particularly for tin targets used in light source generation and specialized photoresists. The tin pellets must meet stringent purity requirements, with only select suppliers capable of producing materials to the necessary specifications. Similarly, EUV photoresists require novel chemical formulations to achieve adequate sensitivity while maintaining resolution, with companies like JSR, Tokyo Ohka Kogyo, and Shin-Etsu Chemical leading development efforts.

Geopolitical factors have introduced additional complexity to EUV supply chain management, with export controls and technology transfer restrictions affecting component sourcing and system deployment. The concentration of key suppliers in specific regions creates vulnerability to trade disputes, natural disasters, and other disruptions that could impact global semiconductor production capacity.

The supply chain's fragility is further amplified by the long lead times required for EUV system production and component replacement. Manufacturing a single EUV scanner requires approximately 12-18 months, with critical components often having even longer procurement cycles. This extended timeline, combined with the limited supplier base, creates significant challenges for semiconductor manufacturers seeking to expand EUV capacity or maintain existing systems.

The optical components supply chain for EUV systems relies heavily on specialized suppliers with unique capabilities. Zeiss provides the critical multilayer mirrors and optical systems, while companies like Cymer (now part of ASML) supply the laser-produced plasma light sources. These components require extreme precision manufacturing with tolerances measured in picometers, limiting the supplier base to a handful of companies worldwide. The mirrors alone consist of over 100 alternating layers of molybdenum and silicon, manufactured using proprietary deposition techniques that few facilities can replicate.

Critical materials dependencies further constrain the EUV supply chain, particularly for tin targets used in light source generation and specialized photoresists. The tin pellets must meet stringent purity requirements, with only select suppliers capable of producing materials to the necessary specifications. Similarly, EUV photoresists require novel chemical formulations to achieve adequate sensitivity while maintaining resolution, with companies like JSR, Tokyo Ohka Kogyo, and Shin-Etsu Chemical leading development efforts.

Geopolitical factors have introduced additional complexity to EUV supply chain management, with export controls and technology transfer restrictions affecting component sourcing and system deployment. The concentration of key suppliers in specific regions creates vulnerability to trade disputes, natural disasters, and other disruptions that could impact global semiconductor production capacity.

The supply chain's fragility is further amplified by the long lead times required for EUV system production and component replacement. Manufacturing a single EUV scanner requires approximately 12-18 months, with critical components often having even longer procurement cycles. This extended timeline, combined with the limited supplier base, creates significant challenges for semiconductor manufacturers seeking to expand EUV capacity or maintain existing systems.

Cost-Performance Trade-offs in Advanced Node Manufacturing

The transition to advanced semiconductor nodes below 7nm presents manufacturers with critical cost-performance decisions that fundamentally reshape production economics. EUV lithography and extreme double patterning represent two distinct approaches, each carrying unique financial implications and operational trade-offs that directly impact manufacturing viability and market competitiveness.

EUV lithography demands substantial upfront capital investment, with individual scanners costing approximately $200-300 million. However, this technology offers simplified process flows by eliminating multiple patterning steps, reducing overall mask costs, and minimizing overlay errors. The single-exposure capability significantly decreases cycle times and improves yield predictability, translating to lower cost-per-wafer in high-volume production scenarios.

Extreme double patterning presents a lower initial capital barrier but introduces complex process overhead that escalates operational expenses. The requirement for precise overlay control, additional mask sets, and extended processing sequences increases both manufacturing time and defect probability. These factors compound to create higher variable costs per unit, particularly challenging for cost-sensitive applications.

Performance considerations reveal divergent optimization paths. EUV enables superior pattern fidelity and resolution uniformity, critical for high-performance computing applications where transistor variability directly impacts product specifications. The technology's ability to maintain consistent critical dimensions across large die areas provides significant advantages for advanced processor manufacturing.

Double patterning approaches offer greater process flexibility and established supply chain maturity, enabling manufacturers to leverage existing infrastructure investments. This pathway proves particularly attractive for mixed-node facilities or applications where absolute performance leadership is less critical than cost optimization.

The economic crossover point between these technologies varies significantly based on production volume, product mix, and target market segments. High-volume manufacturers typically achieve EUV cost advantages at production scales exceeding 10,000 wafers per month, while lower-volume specialty applications may favor double patterning approaches despite performance limitations.

Market dynamics further influence these trade-offs, as customer willingness to pay premiums for advanced node benefits directly affects manufacturing strategy selection and long-term technology roadmap decisions.

EUV lithography demands substantial upfront capital investment, with individual scanners costing approximately $200-300 million. However, this technology offers simplified process flows by eliminating multiple patterning steps, reducing overall mask costs, and minimizing overlay errors. The single-exposure capability significantly decreases cycle times and improves yield predictability, translating to lower cost-per-wafer in high-volume production scenarios.

Extreme double patterning presents a lower initial capital barrier but introduces complex process overhead that escalates operational expenses. The requirement for precise overlay control, additional mask sets, and extended processing sequences increases both manufacturing time and defect probability. These factors compound to create higher variable costs per unit, particularly challenging for cost-sensitive applications.

Performance considerations reveal divergent optimization paths. EUV enables superior pattern fidelity and resolution uniformity, critical for high-performance computing applications where transistor variability directly impacts product specifications. The technology's ability to maintain consistent critical dimensions across large die areas provides significant advantages for advanced processor manufacturing.

Double patterning approaches offer greater process flexibility and established supply chain maturity, enabling manufacturers to leverage existing infrastructure investments. This pathway proves particularly attractive for mixed-node facilities or applications where absolute performance leadership is less critical than cost optimization.

The economic crossover point between these technologies varies significantly based on production volume, product mix, and target market segments. High-volume manufacturers typically achieve EUV cost advantages at production scales exceeding 10,000 wafers per month, while lower-volume specialty applications may favor double patterning approaches despite performance limitations.

Market dynamics further influence these trade-offs, as customer willingness to pay premiums for advanced node benefits directly affects manufacturing strategy selection and long-term technology roadmap decisions.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!