How to Ensure Data Coherency with Active Memory Systems

MAR 7, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Active Memory Data Coherency Background and Objectives

Active memory systems represent a paradigm shift in computer architecture, where memory components possess computational capabilities beyond traditional passive storage. Unlike conventional memory hierarchies that rely on separate processing units to manage data operations, active memory integrates processing elements directly within memory modules. This architectural evolution addresses the growing performance gap between processor speed and memory bandwidth, commonly known as the "memory wall" problem.

The emergence of active memory technologies stems from the increasing demands of data-intensive applications such as artificial intelligence, big data analytics, and high-performance computing workloads. These applications require frequent data movement between memory and processing units, creating bottlenecks that limit overall system performance. Active memory systems aim to minimize data movement by bringing computation closer to where data resides, fundamentally changing how systems handle memory operations.

Data coherency in active memory environments presents unique challenges compared to traditional computing architectures. In conventional systems, coherency protocols primarily manage consistency between processor caches and main memory. However, active memory introduces multiple distributed processing elements within the memory hierarchy, each capable of modifying data independently. This distributed processing capability creates complex scenarios where multiple memory modules may simultaneously access and modify shared data structures.

The coherency challenge becomes particularly acute when considering the heterogeneous nature of active memory systems. Different memory modules may employ varying processing capabilities, from simple arithmetic operations to complex neural network computations. Ensuring that all processing elements maintain a consistent view of shared data while maximizing parallel processing efficiency requires sophisticated coordination mechanisms.

Current market trends indicate growing adoption of near-data computing solutions, including processing-in-memory technologies and smart memory controllers. Major semiconductor companies are investing heavily in active memory research, recognizing its potential to address performance limitations in emerging applications. The convergence of artificial intelligence workloads and edge computing requirements further accelerates the need for coherent active memory solutions.

The primary objective of ensuring data coherency in active memory systems is to maintain data consistency across distributed processing elements while preserving the performance benefits of near-data computation. This involves developing protocols that can efficiently coordinate memory operations across multiple active memory modules without introducing significant latency penalties. Additionally, the solution must scale effectively as system complexity increases and support diverse application requirements ranging from real-time processing to batch analytics workloads.

The emergence of active memory technologies stems from the increasing demands of data-intensive applications such as artificial intelligence, big data analytics, and high-performance computing workloads. These applications require frequent data movement between memory and processing units, creating bottlenecks that limit overall system performance. Active memory systems aim to minimize data movement by bringing computation closer to where data resides, fundamentally changing how systems handle memory operations.

Data coherency in active memory environments presents unique challenges compared to traditional computing architectures. In conventional systems, coherency protocols primarily manage consistency between processor caches and main memory. However, active memory introduces multiple distributed processing elements within the memory hierarchy, each capable of modifying data independently. This distributed processing capability creates complex scenarios where multiple memory modules may simultaneously access and modify shared data structures.

The coherency challenge becomes particularly acute when considering the heterogeneous nature of active memory systems. Different memory modules may employ varying processing capabilities, from simple arithmetic operations to complex neural network computations. Ensuring that all processing elements maintain a consistent view of shared data while maximizing parallel processing efficiency requires sophisticated coordination mechanisms.

Current market trends indicate growing adoption of near-data computing solutions, including processing-in-memory technologies and smart memory controllers. Major semiconductor companies are investing heavily in active memory research, recognizing its potential to address performance limitations in emerging applications. The convergence of artificial intelligence workloads and edge computing requirements further accelerates the need for coherent active memory solutions.

The primary objective of ensuring data coherency in active memory systems is to maintain data consistency across distributed processing elements while preserving the performance benefits of near-data computation. This involves developing protocols that can efficiently coordinate memory operations across multiple active memory modules without introducing significant latency penalties. Additionally, the solution must scale effectively as system complexity increases and support diverse application requirements ranging from real-time processing to batch analytics workloads.

Market Demand for Coherent Active Memory Solutions

The market demand for coherent active memory solutions is experiencing unprecedented growth driven by the exponential increase in data-intensive applications across multiple industries. Cloud computing providers, high-performance computing centers, and enterprise data centers are increasingly seeking memory architectures that can maintain data consistency while delivering superior performance compared to traditional passive memory systems.

Financial services organizations represent a significant market segment, where real-time trading systems and risk management platforms require instantaneous access to coherent data across distributed memory pools. The stringent latency requirements and regulatory compliance demands in this sector create substantial opportunities for active memory solutions that can guarantee data coherency without compromising performance.

Artificial intelligence and machine learning workloads constitute another rapidly expanding market driver. Large-scale neural network training and inference operations demand massive memory bandwidth and capacity while maintaining strict data coherency requirements. The proliferation of AI applications in autonomous vehicles, natural language processing, and computer vision creates sustained demand for memory systems capable of handling complex data dependencies.

The telecommunications industry's transition to 5G networks and edge computing infrastructure generates substantial demand for coherent active memory solutions. Network function virtualization and software-defined networking require memory architectures that can maintain data consistency across distributed processing nodes while supporting ultra-low latency requirements essential for real-time communication services.

Scientific computing and research institutions drive demand through computationally intensive simulations in climate modeling, genomics, and materials science. These applications require memory systems capable of maintaining coherency across large-scale parallel processing environments while supporting complex data sharing patterns between computational nodes.

Enterprise database management systems increasingly require active memory solutions to support in-memory analytics and real-time transaction processing. The growing adoption of hybrid transactional and analytical processing workloads creates market opportunities for memory architectures that can ensure data coherency while supporting concurrent read and write operations across multiple processing units.

The gaming and entertainment industry's demand for immersive experiences drives requirements for coherent memory systems capable of supporting real-time rendering and physics simulations. Virtual and augmented reality applications require consistent data access patterns across graphics processing units and central processing units to maintain seamless user experiences.

Financial services organizations represent a significant market segment, where real-time trading systems and risk management platforms require instantaneous access to coherent data across distributed memory pools. The stringent latency requirements and regulatory compliance demands in this sector create substantial opportunities for active memory solutions that can guarantee data coherency without compromising performance.

Artificial intelligence and machine learning workloads constitute another rapidly expanding market driver. Large-scale neural network training and inference operations demand massive memory bandwidth and capacity while maintaining strict data coherency requirements. The proliferation of AI applications in autonomous vehicles, natural language processing, and computer vision creates sustained demand for memory systems capable of handling complex data dependencies.

The telecommunications industry's transition to 5G networks and edge computing infrastructure generates substantial demand for coherent active memory solutions. Network function virtualization and software-defined networking require memory architectures that can maintain data consistency across distributed processing nodes while supporting ultra-low latency requirements essential for real-time communication services.

Scientific computing and research institutions drive demand through computationally intensive simulations in climate modeling, genomics, and materials science. These applications require memory systems capable of maintaining coherency across large-scale parallel processing environments while supporting complex data sharing patterns between computational nodes.

Enterprise database management systems increasingly require active memory solutions to support in-memory analytics and real-time transaction processing. The growing adoption of hybrid transactional and analytical processing workloads creates market opportunities for memory architectures that can ensure data coherency while supporting concurrent read and write operations across multiple processing units.

The gaming and entertainment industry's demand for immersive experiences drives requirements for coherent memory systems capable of supporting real-time rendering and physics simulations. Virtual and augmented reality applications require consistent data access patterns across graphics processing units and central processing units to maintain seamless user experiences.

Current Coherency Challenges in Active Memory Architectures

Active memory systems face significant coherency challenges that stem from their fundamental architectural differences compared to traditional passive memory hierarchies. The primary challenge lies in maintaining consistent data states across multiple processing elements that can simultaneously access and modify shared memory locations. Unlike conventional systems where memory serves as a passive storage medium, active memory architectures integrate computational capabilities directly within the memory subsystem, creating complex interdependencies between processing and storage operations.

Cache coherency protocols, which have been refined over decades for traditional architectures, encounter substantial limitations when applied to active memory systems. The distributed nature of processing elements within active memory creates scenarios where multiple computational units may operate on the same data simultaneously, leading to potential race conditions and inconsistent memory states. Traditional snooping and directory-based protocols struggle to scale effectively in these environments due to the increased complexity of tracking coherency across numerous active memory nodes.

Memory consistency models present another critical challenge, as active memory systems must reconcile the ordering guarantees expected by software with the parallel execution capabilities of distributed memory processors. The relaxed consistency models that work well in conventional multiprocessor systems may not provide adequate guarantees for applications running on active memory architectures, where the boundary between computation and storage becomes blurred.

Latency and bandwidth constraints further complicate coherency maintenance in active memory systems. The overhead associated with coherency protocols can significantly impact performance, particularly when frequent synchronization is required between distant memory nodes. Network congestion and variable communication delays between active memory elements can lead to coherency protocol timeouts and degraded system performance.

Scalability represents a fundamental challenge as active memory systems grow in size and complexity. Traditional coherency mechanisms exhibit quadratic scaling behavior in terms of communication overhead, making them unsuitable for large-scale active memory deployments. The challenge intensifies when considering heterogeneous active memory systems that incorporate different types of processing elements with varying computational capabilities and memory access patterns.

Programming model complexity adds another layer of difficulty, as developers must navigate the intricacies of data placement and coherency management in active memory systems. The lack of standardized coherency semantics across different active memory architectures creates portability issues and increases development complexity, hindering widespread adoption of these promising technologies.

Cache coherency protocols, which have been refined over decades for traditional architectures, encounter substantial limitations when applied to active memory systems. The distributed nature of processing elements within active memory creates scenarios where multiple computational units may operate on the same data simultaneously, leading to potential race conditions and inconsistent memory states. Traditional snooping and directory-based protocols struggle to scale effectively in these environments due to the increased complexity of tracking coherency across numerous active memory nodes.

Memory consistency models present another critical challenge, as active memory systems must reconcile the ordering guarantees expected by software with the parallel execution capabilities of distributed memory processors. The relaxed consistency models that work well in conventional multiprocessor systems may not provide adequate guarantees for applications running on active memory architectures, where the boundary between computation and storage becomes blurred.

Latency and bandwidth constraints further complicate coherency maintenance in active memory systems. The overhead associated with coherency protocols can significantly impact performance, particularly when frequent synchronization is required between distant memory nodes. Network congestion and variable communication delays between active memory elements can lead to coherency protocol timeouts and degraded system performance.

Scalability represents a fundamental challenge as active memory systems grow in size and complexity. Traditional coherency mechanisms exhibit quadratic scaling behavior in terms of communication overhead, making them unsuitable for large-scale active memory deployments. The challenge intensifies when considering heterogeneous active memory systems that incorporate different types of processing elements with varying computational capabilities and memory access patterns.

Programming model complexity adds another layer of difficulty, as developers must navigate the intricacies of data placement and coherency management in active memory systems. The lack of standardized coherency semantics across different active memory architectures creates portability issues and increases development complexity, hindering widespread adoption of these promising technologies.

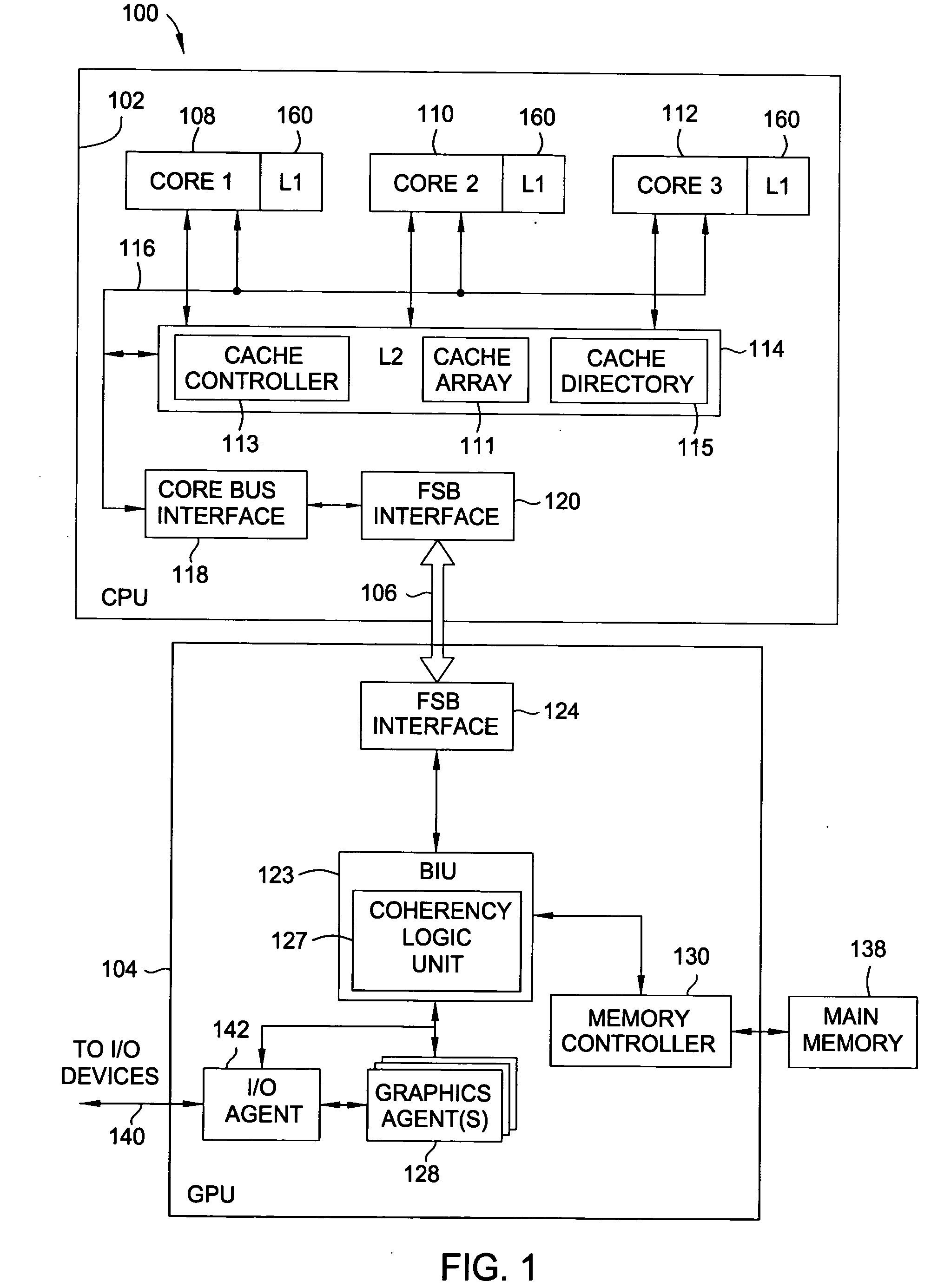

Existing Coherency Mechanisms for Active Memory Systems

01 Cache coherency protocols for multi-processor systems

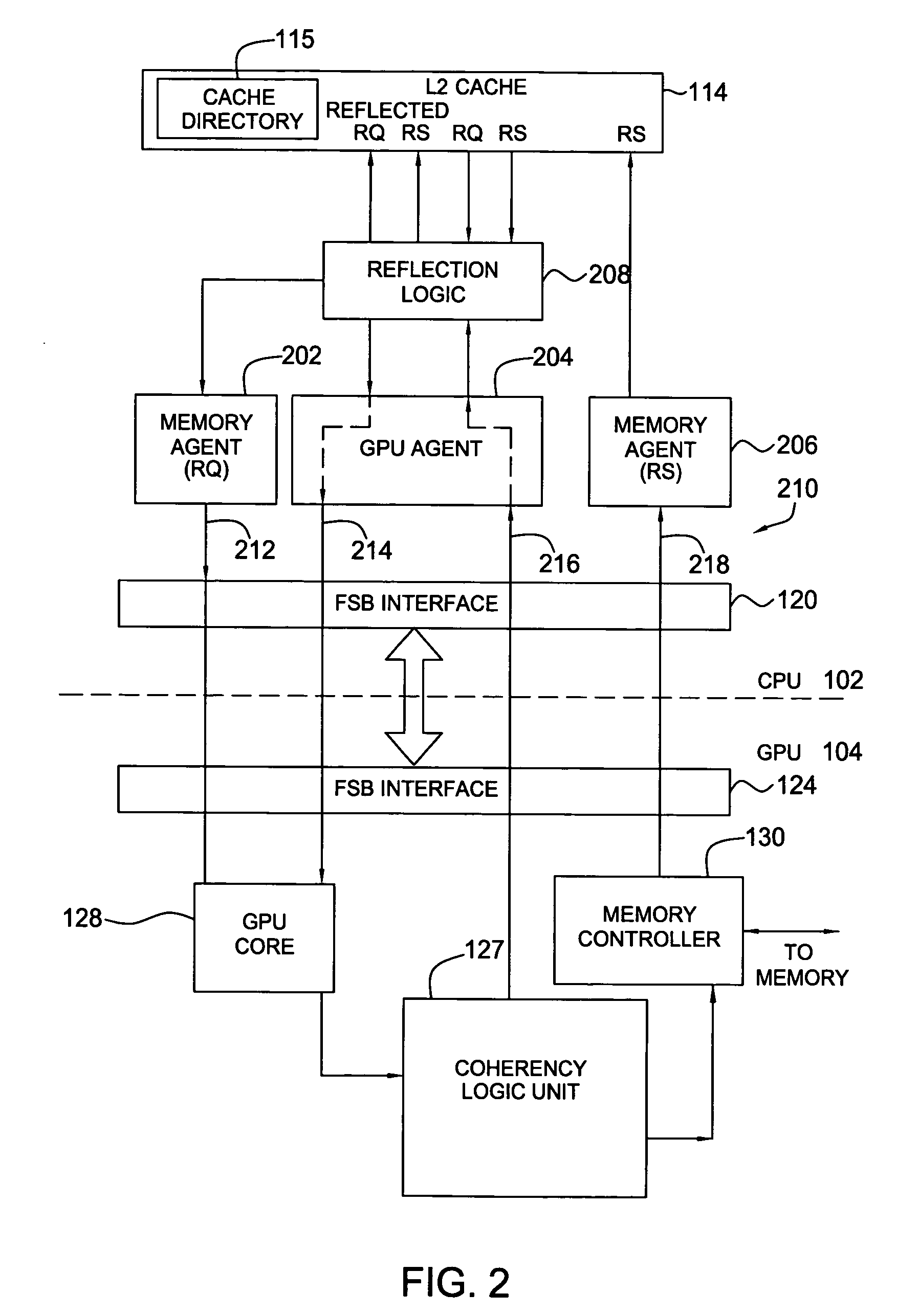

Cache coherency protocols are essential mechanisms to maintain data consistency across multiple processors or cores that share memory. These protocols ensure that when one processor modifies data in its cache, other processors are notified or their cached copies are invalidated or updated. Common protocols include MESI, MOESI, and directory-based coherency schemes. These mechanisms prevent stale data reads and maintain system-wide data integrity in shared memory architectures.- Cache coherency protocols for multiprocessor systems: Cache coherency protocols are essential mechanisms to maintain data consistency across multiple processors or cores that share memory. These protocols ensure that when one processor modifies data in its cache, other processors are notified or their cached copies are invalidated or updated. Various coherency protocols such as MESI, MOESI, and directory-based protocols can be implemented to track cache line states and coordinate data access among multiple processing units, preventing stale data reads and ensuring system-wide data integrity.

- Snoop-based coherency mechanisms: Snoop-based coherency mechanisms involve monitoring or snooping bus transactions to maintain cache coherence in shared memory systems. Each cache controller monitors the bus for memory access requests from other processors and takes appropriate actions such as invalidating or updating its local cache copies. This approach allows caches to remain coherent without requiring a centralized directory, making it suitable for systems with moderate numbers of processors where bus bandwidth is sufficient to handle snoop traffic.

- Directory-based coherency schemes: Directory-based coherency schemes utilize a centralized or distributed directory structure to track the state and location of cached data blocks throughout the system. The directory maintains information about which processors have copies of specific memory blocks and their current states. This approach reduces broadcast traffic compared to snoop-based systems and scales better for larger multiprocessor configurations. Directory entries can indicate whether data is shared, exclusively owned, or modified, enabling efficient coherency management.

- Coherency management in non-uniform memory access architectures: In non-uniform memory access architectures, coherency management must account for varying memory access latencies and distributed memory structures. Specialized coherency protocols and hardware mechanisms are employed to maintain data consistency across nodes with local and remote memory. These systems often combine directory-based tracking with optimized message passing and cache-to-cache transfers to minimize latency while ensuring coherent views of shared data across the distributed memory hierarchy.

- Hardware-software co-designed coherency solutions: Hardware-software co-designed coherency solutions leverage both architectural features and software-level optimizations to achieve efficient data coherency. These approaches may include specialized instructions for cache management, memory barriers, and synchronization primitives that work in conjunction with hardware coherency protocols. Software can explicitly manage coherency for specific data structures or regions, while hardware handles automatic coherency for general memory accesses, providing flexibility and performance optimization opportunities for different workload characteristics.

02 Snoop-based coherency mechanisms

Snoop-based coherency is a technique where cache controllers monitor or 'snoop' on the bus to track memory operations performed by other processors. When a processor performs a read or write operation, other caches check their contents and take appropriate actions such as invalidation or data supply. This approach is commonly used in bus-based multiprocessor systems and provides a distributed method for maintaining cache coherency without centralized control.Expand Specific Solutions03 Directory-based coherency schemes

Directory-based coherency maintains a centralized or distributed directory that tracks the state and location of cached data blocks across the system. The directory contains information about which processors have copies of specific memory blocks and their states. This approach scales better than snoop-based protocols for large-scale systems as it reduces broadcast traffic and provides point-to-point communication for coherency operations.Expand Specific Solutions04 Memory consistency models and ordering

Memory consistency models define the rules for the order in which memory operations appear to execute in a multi-processor system. These models specify constraints on memory access ordering to ensure predictable program behavior while allowing performance optimizations. Implementations include sequential consistency, relaxed consistency models, and various ordering mechanisms that balance between performance and programmability. These models work in conjunction with coherency protocols to provide correct execution semantics.Expand Specific Solutions05 Coherency management in distributed and non-uniform memory architectures

In distributed memory systems and non-uniform memory access architectures, coherency management becomes more complex due to varying access latencies and distributed memory resources. Specialized techniques are employed to handle coherency across multiple memory domains, including remote memory access protocols, hierarchical coherency schemes, and optimized data migration strategies. These approaches address the challenges of maintaining coherency while minimizing latency penalties associated with remote memory accesses.Expand Specific Solutions

Key Players in Active Memory and Coherency Solutions

The active memory systems market for data coherency is in a mature growth phase, driven by increasing demands for real-time processing and AI workloads. The market spans billions in revenue across enterprise computing, mobile devices, and data centers. Technology maturity varies significantly among key players: Intel Corp. and Advanced Micro Devices lead in processor-integrated memory solutions, while Micron Technology and SK hynix dominate memory manufacturing with advanced coherency protocols. IBM and Hewlett Packard Enterprise focus on enterprise-grade coherent systems, whereas ARM Limited develops architectural standards for mobile coherency. Chinese players like Huawei Technologies and Hygon Information Technology are rapidly advancing but remain behind Western leaders in cutting-edge implementations. Academic institutions like Huazhong University of Science & Technology contribute foundational research, while emerging companies like Akeana explore RISC-V-based coherent architectures, indicating ongoing innovation in this competitive landscape.

Intel Corp.

Technical Solution: Intel implements comprehensive cache coherency protocols including MESI (Modified, Exclusive, Shared, Invalid) and MESIF protocols in their multi-core processors to ensure data coherency with active memory systems. Their approach utilizes hardware-based coherency mechanisms with sophisticated cache hierarchies, supporting both snooping and directory-based coherency protocols. Intel's processors feature advanced memory ordering guarantees and atomic operations to maintain consistency across multiple cores accessing shared memory regions. The company has developed specialized instructions like memory fences and barriers to provide fine-grained control over memory ordering, ensuring that memory operations complete in the expected sequence across different processing units.

Strengths: Mature hardware-based coherency protocols with proven reliability and performance in enterprise systems. Weaknesses: High complexity and power consumption in multi-socket systems with increasing core counts.

International Business Machines Corp.

Technical Solution: IBM has developed advanced coherency solutions through their POWER architecture and mainframe systems, implementing sophisticated directory-based coherency protocols for large-scale symmetric multiprocessing systems. Their approach includes hardware-assisted coherency management with specialized coherency engines that track memory state across multiple processors and memory domains. IBM's systems utilize advanced interconnect technologies and coherency protocols that can scale to hundreds of processors while maintaining strict memory consistency models. The company has pioneered techniques for handling coherency in heterogeneous computing environments, including GPU-CPU coherency and accelerator integration, ensuring seamless data sharing across different processing units in active memory systems.

Strengths: Excellent scalability for large enterprise systems and strong coherency guarantees in mission-critical applications. Weaknesses: Higher cost and complexity compared to commodity solutions, limited adoption outside enterprise markets.

Core Innovations in Active Memory Coherency Protocols

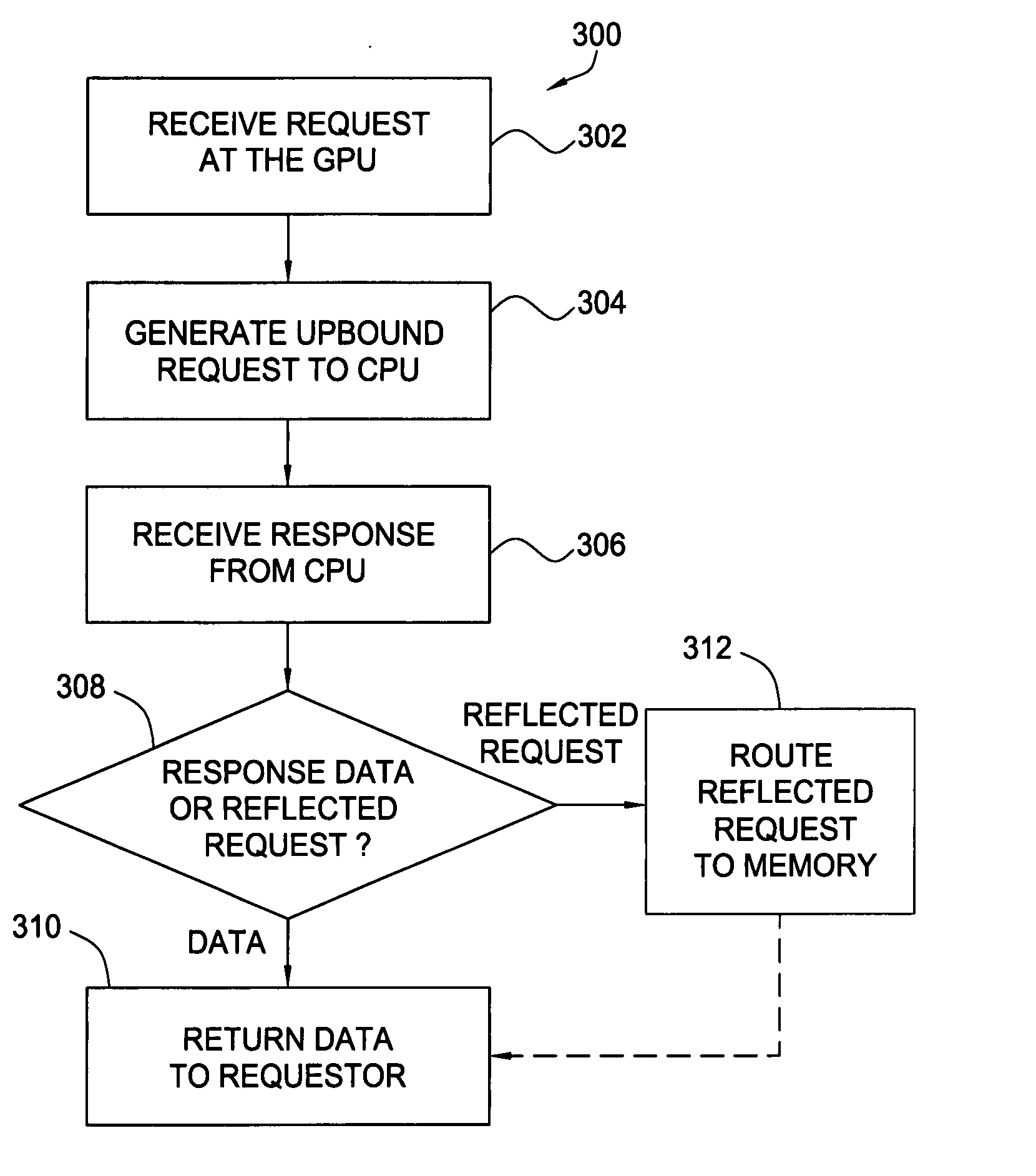

Method and apparatus for shared virtual memory to manage data coherency in a heterogeneous processing system

PatentPendingUS20250061060A1

Innovation

- The implementation of a scalable coherency tracking system that utilizes shared virtual memory to manage data coherency, reducing the granularity of coherency tracking and moving coherency state storage from dedicated hardware blocks to system memory as page table metadata.

Low latency coherency protocol for a multi-chip multiprocessor system

PatentInactiveUS20060080513A1

Innovation

- Implementing a low latency coherency protocol that uses virtual channels for request/response transactions between remote devices and processors, along with a snoop filter mechanism to reduce unnecessary snoop requests by filtering out requests targeting data not in the cache, allowing direct access to cached data and routing others directly to memory.

Performance Impact Assessment of Coherency Overhead

The performance implications of maintaining data coherency in active memory systems represent a critical trade-off between system reliability and computational efficiency. Coherency mechanisms inherently introduce latency penalties that can significantly impact overall system throughput, particularly in high-frequency memory access scenarios. These overheads manifest primarily through additional memory transactions, cache invalidation cycles, and synchronization protocols that must execute before data operations can complete.

Memory bandwidth consumption increases substantially when coherency protocols are active, as each coherent memory operation may trigger multiple auxiliary transactions across the memory hierarchy. Directory-based coherency systems typically consume 10-15% additional bandwidth for metadata management, while snooping protocols can generate broadcast traffic that scales poorly with system size. The cumulative effect becomes particularly pronounced in multi-socket configurations where inter-node coherency traffic competes with application data for limited interconnect resources.

Latency penalties vary significantly based on the coherency state transitions required for specific memory operations. Cache-to-cache transfers, while faster than main memory access, still introduce 50-100 nanosecond delays compared to local cache hits. Write operations face the highest overhead burden, as they must invalidate or update remote copies before completion, potentially stalling execution pipelines and reducing instruction-level parallelism effectiveness.

Energy consumption represents another substantial overhead dimension, as coherency maintenance requires continuous monitoring of memory transactions and periodic cache line state updates. Active memory systems with hardware-accelerated coherency can consume 15-25% additional power compared to non-coherent alternatives, primarily due to increased interconnect activity and cache controller complexity.

The scalability characteristics of coherency overhead present long-term performance concerns, as most protocols exhibit super-linear scaling behavior with increasing core counts. Systems exceeding 64-128 cores often experience coherency bottlenecks that limit effective parallelization, necessitating careful workload partitioning and data locality optimization strategies to maintain acceptable performance levels.

Memory bandwidth consumption increases substantially when coherency protocols are active, as each coherent memory operation may trigger multiple auxiliary transactions across the memory hierarchy. Directory-based coherency systems typically consume 10-15% additional bandwidth for metadata management, while snooping protocols can generate broadcast traffic that scales poorly with system size. The cumulative effect becomes particularly pronounced in multi-socket configurations where inter-node coherency traffic competes with application data for limited interconnect resources.

Latency penalties vary significantly based on the coherency state transitions required for specific memory operations. Cache-to-cache transfers, while faster than main memory access, still introduce 50-100 nanosecond delays compared to local cache hits. Write operations face the highest overhead burden, as they must invalidate or update remote copies before completion, potentially stalling execution pipelines and reducing instruction-level parallelism effectiveness.

Energy consumption represents another substantial overhead dimension, as coherency maintenance requires continuous monitoring of memory transactions and periodic cache line state updates. Active memory systems with hardware-accelerated coherency can consume 15-25% additional power compared to non-coherent alternatives, primarily due to increased interconnect activity and cache controller complexity.

The scalability characteristics of coherency overhead present long-term performance concerns, as most protocols exhibit super-linear scaling behavior with increasing core counts. Systems exceeding 64-128 cores often experience coherency bottlenecks that limit effective parallelization, necessitating careful workload partitioning and data locality optimization strategies to maintain acceptable performance levels.

Security Implications in Coherent Active Memory Design

The integration of active memory systems with coherent data management introduces significant security vulnerabilities that require comprehensive evaluation and mitigation strategies. Active memory architectures, which enable computational operations directly within memory modules, expand the traditional attack surface beyond conventional processor-memory boundaries. The distributed nature of coherent active memory systems creates multiple potential entry points for malicious actors, ranging from side-channel attacks exploiting coherence protocols to direct manipulation of in-memory computations.

Memory coherence protocols themselves present unique security challenges in active memory environments. Traditional coherence mechanisms rely on predictable state transitions and message passing between cache hierarchies and memory controllers. However, active memory systems introduce computational elements that can potentially intercept, modify, or replay coherence messages. This creates opportunities for adversaries to inject false coherence states, leading to data corruption or unauthorized access to sensitive information across different processing nodes.

The temporal aspects of coherence maintenance in active memory systems introduce timing-based attack vectors. Coherence protocols typically operate with specific timing constraints and ordering guarantees. Malicious actors could exploit these timing dependencies to infer sensitive data patterns or disrupt system operations through carefully crafted timing attacks. The distributed nature of active memory systems amplifies these risks, as coherence messages traverse multiple network segments and processing elements.

Hardware-level security mechanisms must be fundamentally reconsidered for coherent active memory architectures. Traditional memory protection units and access control mechanisms may prove insufficient when computational operations occur directly within memory modules. New security primitives are required to establish trusted execution environments that span both traditional processing units and active memory elements while maintaining coherence guarantees.

Cryptographic approaches to securing coherent active memory systems face unique implementation challenges. End-to-end encryption of coherence traffic could significantly impact performance, while selective encryption schemes must carefully balance security requirements with coherence protocol efficiency. Memory encryption techniques must be adapted to accommodate the computational capabilities of active memory while preserving the integrity of coherence operations across distributed memory hierarchies.

Memory coherence protocols themselves present unique security challenges in active memory environments. Traditional coherence mechanisms rely on predictable state transitions and message passing between cache hierarchies and memory controllers. However, active memory systems introduce computational elements that can potentially intercept, modify, or replay coherence messages. This creates opportunities for adversaries to inject false coherence states, leading to data corruption or unauthorized access to sensitive information across different processing nodes.

The temporal aspects of coherence maintenance in active memory systems introduce timing-based attack vectors. Coherence protocols typically operate with specific timing constraints and ordering guarantees. Malicious actors could exploit these timing dependencies to infer sensitive data patterns or disrupt system operations through carefully crafted timing attacks. The distributed nature of active memory systems amplifies these risks, as coherence messages traverse multiple network segments and processing elements.

Hardware-level security mechanisms must be fundamentally reconsidered for coherent active memory architectures. Traditional memory protection units and access control mechanisms may prove insufficient when computational operations occur directly within memory modules. New security primitives are required to establish trusted execution environments that span both traditional processing units and active memory elements while maintaining coherence guarantees.

Cryptographic approaches to securing coherent active memory systems face unique implementation challenges. End-to-end encryption of coherence traffic could significantly impact performance, while selective encryption schemes must carefully balance security requirements with coherence protocol efficiency. Memory encryption techniques must be adapted to accommodate the computational capabilities of active memory while preserving the integrity of coherence operations across distributed memory hierarchies.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!