How to Evaluate TSV Electromechanical Stability

APR 15, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

TSV Electromechanical Stability Background and Objectives

Through-Silicon Via (TSV) technology has emerged as a critical enabler for three-dimensional integrated circuits and advanced packaging solutions, fundamentally transforming the semiconductor industry's approach to device miniaturization and performance enhancement. As electronic systems demand higher integration density, improved electrical performance, and reduced form factors, TSV structures provide vertical interconnections that enable stacking of multiple silicon dies, creating compact, high-performance electronic packages.

The electromechanical stability of TSV structures represents one of the most significant technical challenges in modern semiconductor manufacturing and packaging. TSVs are subjected to complex mechanical stresses arising from thermal cycling, coefficient of thermal expansion mismatches between different materials, and manufacturing-induced residual stresses. These mechanical forces can lead to various failure modes including via cracking, delamination at interfaces, and degradation of electrical performance over operational lifetime.

Historical development of TSV technology began in the early 2000s with initial applications in MEMS devices and image sensors. The technology has evolved through several generations, progressing from simple through-hole connections to sophisticated high-aspect-ratio structures with advanced barrier layers and filling materials. Each evolutionary step has brought new challenges in maintaining structural integrity while meeting increasingly stringent electrical and thermal performance requirements.

The primary objective of evaluating TSV electromechanical stability is to establish comprehensive methodologies for predicting and preventing failure modes that could compromise device reliability. This evaluation encompasses understanding stress distribution patterns, identifying critical failure mechanisms, and developing predictive models that can guide design optimization. Key technical goals include establishing standardized testing protocols, developing accurate simulation frameworks, and creating design guidelines that ensure long-term reliability under various operational conditions.

Current industry trends indicate a growing emphasis on developing TSV structures capable of withstanding extreme environmental conditions while maintaining electrical performance. The integration of artificial intelligence and machine learning approaches in stability evaluation represents an emerging frontier, promising more accurate prediction capabilities and optimized design parameters for next-generation three-dimensional integrated systems.

The electromechanical stability of TSV structures represents one of the most significant technical challenges in modern semiconductor manufacturing and packaging. TSVs are subjected to complex mechanical stresses arising from thermal cycling, coefficient of thermal expansion mismatches between different materials, and manufacturing-induced residual stresses. These mechanical forces can lead to various failure modes including via cracking, delamination at interfaces, and degradation of electrical performance over operational lifetime.

Historical development of TSV technology began in the early 2000s with initial applications in MEMS devices and image sensors. The technology has evolved through several generations, progressing from simple through-hole connections to sophisticated high-aspect-ratio structures with advanced barrier layers and filling materials. Each evolutionary step has brought new challenges in maintaining structural integrity while meeting increasingly stringent electrical and thermal performance requirements.

The primary objective of evaluating TSV electromechanical stability is to establish comprehensive methodologies for predicting and preventing failure modes that could compromise device reliability. This evaluation encompasses understanding stress distribution patterns, identifying critical failure mechanisms, and developing predictive models that can guide design optimization. Key technical goals include establishing standardized testing protocols, developing accurate simulation frameworks, and creating design guidelines that ensure long-term reliability under various operational conditions.

Current industry trends indicate a growing emphasis on developing TSV structures capable of withstanding extreme environmental conditions while maintaining electrical performance. The integration of artificial intelligence and machine learning approaches in stability evaluation represents an emerging frontier, promising more accurate prediction capabilities and optimized design parameters for next-generation three-dimensional integrated systems.

Market Demand for Reliable TSV Technology

The semiconductor industry's relentless pursuit of miniaturization and enhanced performance has positioned Through-Silicon Via (TSV) technology as a critical enabler for advanced packaging solutions. As electronic devices become increasingly compact while demanding higher functionality, the market demand for reliable TSV technology has experienced substantial growth across multiple sectors.

The consumer electronics market represents the largest driver for TSV adoption, particularly in smartphones, tablets, and wearable devices. These applications require ultra-thin form factors while maintaining high-performance capabilities, making TSV-based 3D integration essential for achieving desired specifications. The automotive electronics sector has emerged as another significant demand driver, especially with the proliferation of advanced driver assistance systems and electric vehicle technologies that require robust, space-efficient semiconductor solutions.

Data center and high-performance computing applications constitute a rapidly expanding market segment for TSV technology. The increasing computational demands of artificial intelligence, machine learning, and cloud computing services necessitate memory and processor architectures that can deliver superior bandwidth and reduced latency. TSV technology enables the vertical stacking of memory dies and logic circuits, addressing these performance requirements while optimizing space utilization.

The reliability requirements across these market segments have intensified significantly, particularly regarding electromechanical stability. Automotive applications demand operational reliability under extreme temperature variations, mechanical stress, and extended operational lifespans. Consumer electronics require consistent performance despite frequent thermal cycling and mechanical handling. Data center applications necessitate continuous operation with minimal failure rates to maintain service availability.

Market research indicates that reliability concerns, particularly related to TSV electromechanical stability, represent primary barriers to broader technology adoption. Manufacturers increasingly prioritize suppliers who can demonstrate comprehensive evaluation methodologies and proven reliability metrics. This trend has created substantial demand for advanced testing and characterization capabilities that can accurately assess TSV performance under various stress conditions.

The medical device and aerospace sectors, while representing smaller market volumes, demand exceptionally high reliability standards that drive innovation in TSV evaluation techniques. These applications often require decades-long operational reliability, making thorough electromechanical stability assessment crucial for market acceptance and regulatory compliance.

The consumer electronics market represents the largest driver for TSV adoption, particularly in smartphones, tablets, and wearable devices. These applications require ultra-thin form factors while maintaining high-performance capabilities, making TSV-based 3D integration essential for achieving desired specifications. The automotive electronics sector has emerged as another significant demand driver, especially with the proliferation of advanced driver assistance systems and electric vehicle technologies that require robust, space-efficient semiconductor solutions.

Data center and high-performance computing applications constitute a rapidly expanding market segment for TSV technology. The increasing computational demands of artificial intelligence, machine learning, and cloud computing services necessitate memory and processor architectures that can deliver superior bandwidth and reduced latency. TSV technology enables the vertical stacking of memory dies and logic circuits, addressing these performance requirements while optimizing space utilization.

The reliability requirements across these market segments have intensified significantly, particularly regarding electromechanical stability. Automotive applications demand operational reliability under extreme temperature variations, mechanical stress, and extended operational lifespans. Consumer electronics require consistent performance despite frequent thermal cycling and mechanical handling. Data center applications necessitate continuous operation with minimal failure rates to maintain service availability.

Market research indicates that reliability concerns, particularly related to TSV electromechanical stability, represent primary barriers to broader technology adoption. Manufacturers increasingly prioritize suppliers who can demonstrate comprehensive evaluation methodologies and proven reliability metrics. This trend has created substantial demand for advanced testing and characterization capabilities that can accurately assess TSV performance under various stress conditions.

The medical device and aerospace sectors, while representing smaller market volumes, demand exceptionally high reliability standards that drive innovation in TSV evaluation techniques. These applications often require decades-long operational reliability, making thorough electromechanical stability assessment crucial for market acceptance and regulatory compliance.

Current TSV Stability Challenges and Limitations

TSV electromechanical stability evaluation faces significant challenges stemming from the complex multi-physics interactions within three-dimensional integrated circuits. The primary limitation lies in the lack of standardized measurement protocols that can accurately capture the dynamic behavior of TSVs under various operational conditions. Current evaluation methods often rely on simplified models that fail to account for the intricate coupling between electrical, thermal, and mechanical phenomena occurring simultaneously within the silicon substrate.

Thermal-mechanical stress represents one of the most critical challenges in TSV stability assessment. The coefficient of thermal expansion mismatch between copper fill material and silicon substrate creates substantial stress concentrations during temperature cycling. Existing evaluation techniques struggle to quantify these stress distributions in real-time, particularly at the nanoscale level where crack initiation and propagation occur. Traditional finite element analysis approaches often oversimplify the material interfaces and fail to capture the time-dependent viscoelastic behavior of the surrounding dielectric materials.

Electrical characterization limitations pose another significant barrier to comprehensive stability evaluation. Current measurement techniques cannot adequately separate the contributions of different failure mechanisms, such as electromigration, stress-induced voiding, and interfacial delamination. The parasitic effects introduced by test structures often mask the true electrical behavior of TSVs, making it difficult to establish reliable correlations between electrical parameters and mechanical integrity.

Scale-dependent measurement challenges further complicate stability evaluation efforts. The transition from wafer-level testing to package-level assessment introduces additional variables that current methodologies cannot effectively control. The influence of packaging materials, assembly processes, and system-level thermal cycling creates a complex environment where individual TSV behavior becomes difficult to isolate and characterize accurately.

Process variation sensitivity represents an often-overlooked limitation in current evaluation approaches. Manufacturing tolerances in TSV diameter, depth, and fill quality create significant variability in electromechanical response that existing statistical models inadequately address. The correlation between process parameters and long-term reliability remains poorly understood, limiting the predictive capability of current stability assessment methods.

Finally, the temporal aspects of TSV degradation present substantial evaluation challenges. Current accelerated testing protocols may not accurately represent real-world aging mechanisms, potentially leading to overly optimistic or conservative reliability predictions. The lack of comprehensive understanding regarding the interaction between different degradation modes over extended operational periods continues to limit the effectiveness of existing stability evaluation frameworks.

Thermal-mechanical stress represents one of the most critical challenges in TSV stability assessment. The coefficient of thermal expansion mismatch between copper fill material and silicon substrate creates substantial stress concentrations during temperature cycling. Existing evaluation techniques struggle to quantify these stress distributions in real-time, particularly at the nanoscale level where crack initiation and propagation occur. Traditional finite element analysis approaches often oversimplify the material interfaces and fail to capture the time-dependent viscoelastic behavior of the surrounding dielectric materials.

Electrical characterization limitations pose another significant barrier to comprehensive stability evaluation. Current measurement techniques cannot adequately separate the contributions of different failure mechanisms, such as electromigration, stress-induced voiding, and interfacial delamination. The parasitic effects introduced by test structures often mask the true electrical behavior of TSVs, making it difficult to establish reliable correlations between electrical parameters and mechanical integrity.

Scale-dependent measurement challenges further complicate stability evaluation efforts. The transition from wafer-level testing to package-level assessment introduces additional variables that current methodologies cannot effectively control. The influence of packaging materials, assembly processes, and system-level thermal cycling creates a complex environment where individual TSV behavior becomes difficult to isolate and characterize accurately.

Process variation sensitivity represents an often-overlooked limitation in current evaluation approaches. Manufacturing tolerances in TSV diameter, depth, and fill quality create significant variability in electromechanical response that existing statistical models inadequately address. The correlation between process parameters and long-term reliability remains poorly understood, limiting the predictive capability of current stability assessment methods.

Finally, the temporal aspects of TSV degradation present substantial evaluation challenges. Current accelerated testing protocols may not accurately represent real-world aging mechanisms, potentially leading to overly optimistic or conservative reliability predictions. The lack of comprehensive understanding regarding the interaction between different degradation modes over extended operational periods continues to limit the effectiveness of existing stability evaluation frameworks.

Existing TSV Stability Assessment Solutions

01 TSV structure design and geometric optimization

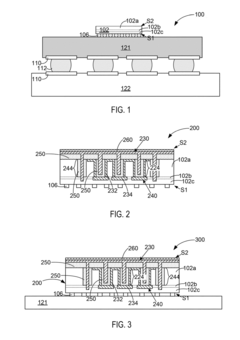

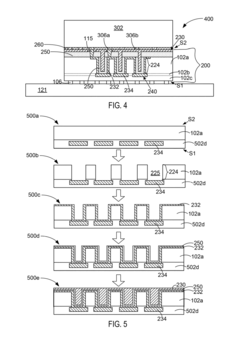

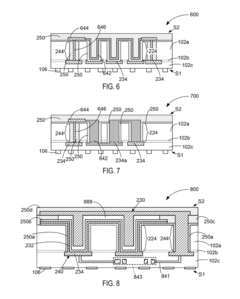

The electromechanical stability of through-silicon vias can be enhanced through optimized structural design, including via diameter, depth, aspect ratio, and spacing configurations. Geometric parameters such as tapered profiles, cylindrical shapes, and annular arrangements are critical for reducing stress concentration and improving mechanical reliability. Advanced design methodologies focus on minimizing coefficient of thermal expansion mismatch effects through strategic dimensional planning.- TSV structure design and geometry optimization: The electromechanical stability of through-silicon vias can be enhanced through optimized structural design and geometric configurations. This includes controlling the aspect ratio, diameter, and pitch of TSVs to minimize stress concentration and mechanical failure. Advanced design methodologies focus on the dimensional parameters and spatial arrangement of vias to improve overall structural integrity and reduce the risk of cracking or delamination during thermal cycling and mechanical stress.

- Barrier layer and liner materials for stress management: The implementation of appropriate barrier layers and liner materials plays a crucial role in managing thermomechanical stress in TSV structures. These materials serve as buffer layers between the silicon substrate and conductive fill material, helping to accommodate coefficient of thermal expansion mismatches. The selection and deposition of these intermediate layers can significantly reduce stress-induced failures and improve the long-term reliability of the interconnect structure.

- TSV filling materials and processes: The choice of filling materials and deposition processes directly impacts the electromechanical stability of TSV structures. Various conductive materials and filling techniques are employed to minimize void formation, reduce residual stress, and ensure uniform filling. Process optimization includes controlling deposition parameters, annealing conditions, and material composition to achieve better mechanical properties and electrical performance while maintaining structural integrity under operational conditions.

- Stress testing and reliability assessment methods: Comprehensive testing methodologies and reliability assessment techniques are essential for evaluating TSV electromechanical stability. These approaches include thermal cycling tests, mechanical stress analysis, and electrical characterization under various environmental conditions. Advanced monitoring and measurement techniques enable the detection of early failure mechanisms and provide data for improving design and manufacturing processes to enhance long-term reliability.

- Keep-out zone design and stress mitigation strategies: The establishment of appropriate keep-out zones around TSV structures and implementation of stress mitigation strategies are critical for maintaining electromechanical stability. These approaches involve defining exclusion areas where sensitive circuit elements should not be placed to avoid stress-induced failures. Additional mitigation techniques include the use of stress-relief structures, optimized layout patterns, and compensation mechanisms that reduce the impact of TSV-induced mechanical stress on surrounding devices and interconnects.

02 Barrier layer and liner materials for stress management

Implementation of specialized barrier layers and liner materials plays a crucial role in managing electromechanical stress in TSV structures. These intermediate layers serve to buffer thermal expansion differences between silicon substrate and conductive fill materials, while maintaining electrical isolation and preventing diffusion. Material selection and thickness optimization of these layers directly impact the overall mechanical stability and reliability of the interconnect structure.Expand Specific Solutions03 Fill material composition and deposition techniques

The choice of conductive fill materials and their deposition methods significantly affects TSV electromechanical performance. Various metallic compositions and deposition processes are employed to minimize void formation, reduce residual stress, and ensure uniform filling. Advanced techniques focus on controlling grain structure, material density, and adhesion properties to enhance both electrical conductivity and mechanical integrity under thermal cycling conditions.Expand Specific Solutions04 Stress testing and reliability assessment methods

Comprehensive evaluation methodologies have been developed to assess TSV electromechanical stability through various stress testing protocols. These include thermal cycling tests, mechanical stress measurements, electrical performance monitoring under different environmental conditions, and accelerated aging studies. Testing frameworks incorporate both simulation-based predictions and experimental validation to ensure long-term reliability and identify potential failure mechanisms.Expand Specific Solutions05 Keep-out zone definition and integration strategies

Establishing appropriate keep-out zones around TSV structures is essential for maintaining electromechanical stability in three-dimensional integrated circuits. These exclusion regions account for stress-induced effects on surrounding active devices and interconnects. Integration strategies include optimized placement rules, buffer zone dimensioning, and layout design guidelines that balance density requirements with mechanical reliability constraints to prevent stress-related failures in adjacent circuit elements.Expand Specific Solutions

Key Players in TSV and 3D IC Industry

The TSV electromechanical stability evaluation field represents a mature technology domain within the broader semiconductor packaging industry, currently experiencing significant growth driven by advanced 3D integration demands. The market demonstrates substantial scale with established players spanning research institutions, power grid companies, and semiconductor manufacturers. Technology maturity varies significantly across participants, with companies like IBM, Texas Instruments, Micron Technology, and GlobalFoundries representing highly advanced commercial capabilities in TSV implementation and testing methodologies. Chinese entities including State Grid Corp., NARI Technology, and National Center for Advanced Packaging show strong institutional research focus, while academic institutions like Fudan University and Industrial Technology Research Institute contribute fundamental research. The competitive landscape reflects a hybrid ecosystem where traditional semiconductor companies leverage established TSV expertise, emerging Chinese firms rapidly develop specialized capabilities, and research institutions provide foundational knowledge, indicating a technology transitioning from research-intensive development to broader commercial deployment across multiple application domains.

GlobalFoundries U.S., Inc.

Technical Solution: GlobalFoundries employs a multi-physics simulation approach combined with statistical process control methods to evaluate TSV electromechanical stability. Their methodology integrates thermal, electrical, and mechanical simulations to predict TSV behavior under operational stress conditions. The company utilizes wafer-level reliability testing with specialized test vehicles containing arrays of TSVs subjected to temperature cycling, mechanical bending, and electrical stress tests. Their evaluation protocol includes in-situ resistance monitoring during stress application, scanning acoustic microscopy for void detection, and cross-sectional analysis using focused ion beam techniques. GlobalFoundries has developed proprietary metrics for quantifying TSV reliability based on resistance drift patterns and failure mode analysis.

Strengths: Industry-proven manufacturing experience and robust statistical analysis methods. Weaknesses: Limited to specific process technologies and requires extensive test vehicle development.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive TSV electromechanical stability evaluation methodologies focusing on thermal-mechanical stress analysis and reliability testing. Their approach includes finite element modeling to predict stress distributions in TSV structures under various thermal cycling conditions, coupled with accelerated aging tests to assess long-term reliability. IBM's evaluation framework incorporates advanced characterization techniques including X-ray microscopy and electron beam inspection to detect micro-cracks and delamination in TSV interfaces. They utilize specialized test structures with embedded sensors to monitor real-time stress evolution during operation, enabling predictive failure analysis and optimization of TSV design parameters for enhanced mechanical stability.

Strengths: Comprehensive modeling capabilities and advanced characterization tools. Weaknesses: High cost of implementation and complex testing procedures.

Core Innovations in TSV Reliability Testing

Through-silicon via (TSV)-based devices and associated techniques and configurations

PatentActiveUS20150255372A1

Innovation

- The implementation of through-silicon via (TSV)-based devices, including capacitors, resistors, and resonators, which utilize TSV structures extending through the bulk semiconductor material, electrically insulative materials, and electrode or resistor materials within these structures to provide enhanced capacitance and resistance while reducing footprint and inductance.

Standardization Framework for TSV Testing

The establishment of a comprehensive standardization framework for TSV testing represents a critical need in the semiconductor industry, particularly as three-dimensional integrated circuits become increasingly prevalent. Current testing methodologies lack uniformity across different manufacturers and research institutions, leading to inconsistent evaluation criteria and incomparable results when assessing TSV electromechanical stability.

International standardization bodies, including IEEE, JEDEC, and IPC, have begun preliminary discussions on developing unified testing protocols for TSV structures. These efforts focus on creating standardized test conditions, measurement parameters, and acceptance criteria that can be universally applied across the industry. The framework must address both electrical and mechanical aspects of TSV performance, ensuring comprehensive evaluation capabilities.

Key components of the emerging standardization framework include standardized sample preparation procedures, environmental testing conditions, and measurement equipment specifications. Temperature cycling protocols, mechanical stress testing parameters, and electrical characterization methods require precise definition to ensure reproducibility across different testing facilities. The framework also establishes minimum sample sizes and statistical analysis requirements for reliable data interpretation.

Metrology standards play a crucial role in the framework, defining acceptable measurement uncertainties and calibration procedures for testing equipment. Cross-sectional analysis techniques, electrical resistance measurements, and mechanical property assessments must adhere to specified accuracy requirements. The framework incorporates guidelines for data reporting formats and documentation standards to facilitate information sharing among industry stakeholders.

Implementation challenges include harmonizing existing proprietary testing methods with proposed standards and ensuring backward compatibility with legacy evaluation procedures. The framework must accommodate various TSV geometries, materials, and manufacturing processes while maintaining testing consistency. Regular updates and revisions are planned to incorporate technological advances and address emerging reliability concerns in TSV applications.

International standardization bodies, including IEEE, JEDEC, and IPC, have begun preliminary discussions on developing unified testing protocols for TSV structures. These efforts focus on creating standardized test conditions, measurement parameters, and acceptance criteria that can be universally applied across the industry. The framework must address both electrical and mechanical aspects of TSV performance, ensuring comprehensive evaluation capabilities.

Key components of the emerging standardization framework include standardized sample preparation procedures, environmental testing conditions, and measurement equipment specifications. Temperature cycling protocols, mechanical stress testing parameters, and electrical characterization methods require precise definition to ensure reproducibility across different testing facilities. The framework also establishes minimum sample sizes and statistical analysis requirements for reliable data interpretation.

Metrology standards play a crucial role in the framework, defining acceptable measurement uncertainties and calibration procedures for testing equipment. Cross-sectional analysis techniques, electrical resistance measurements, and mechanical property assessments must adhere to specified accuracy requirements. The framework incorporates guidelines for data reporting formats and documentation standards to facilitate information sharing among industry stakeholders.

Implementation challenges include harmonizing existing proprietary testing methods with proposed standards and ensuring backward compatibility with legacy evaluation procedures. The framework must accommodate various TSV geometries, materials, and manufacturing processes while maintaining testing consistency. Regular updates and revisions are planned to incorporate technological advances and address emerging reliability concerns in TSV applications.

Thermal Management Impact on TSV Stability

Thermal management plays a critical role in maintaining TSV electromechanical stability throughout the operational lifecycle of 3D integrated circuits. Temperature variations directly influence the mechanical stress distribution within TSV structures, affecting their long-term reliability and electrical performance. The coefficient of thermal expansion (CTE) mismatch between copper TSVs and silicon substrate creates significant thermomechanical stress during temperature cycling, which can lead to interface delamination, crack propagation, and eventual electrical failure.

The thermal gradient across TSV structures introduces non-uniform stress fields that compromise structural integrity. During high-temperature operations, copper TSVs expand more rapidly than the surrounding silicon, generating compressive stress at the TSV-silicon interface. Conversely, cooling cycles induce tensile stress that can initiate micro-crack formation at weak points such as the TSV bottom and sidewall interfaces. These cyclic stress variations accelerate fatigue mechanisms and reduce the overall electromechanical stability of the TSV array.

Heat dissipation efficiency significantly impacts TSV stability evaluation methodologies. Poor thermal management leads to localized hot spots that create asymmetric stress distributions, making traditional stability assessment approaches less reliable. The thermal resistance of TSV structures affects the temperature profile across the 3D stack, influencing the magnitude and distribution of thermomechanical stress. Effective thermal interface materials and heat spreading techniques can mitigate these effects by reducing temperature gradients and minimizing CTE-induced stress concentrations.

Advanced thermal modeling techniques are essential for predicting TSV stability under various thermal conditions. Finite element analysis incorporating temperature-dependent material properties enables accurate simulation of thermomechanical behavior during operational scenarios. These models must account for the complex interactions between thermal cycling frequency, temperature range, and mechanical stress evolution to provide meaningful stability predictions.

The integration of real-time thermal monitoring systems enhances TSV stability evaluation by providing continuous feedback on temperature distribution and thermal transients. This approach enables dynamic assessment of electromechanical stability under actual operating conditions, improving the accuracy of reliability predictions and enabling proactive thermal management strategies to maintain optimal TSV performance throughout the device lifetime.

The thermal gradient across TSV structures introduces non-uniform stress fields that compromise structural integrity. During high-temperature operations, copper TSVs expand more rapidly than the surrounding silicon, generating compressive stress at the TSV-silicon interface. Conversely, cooling cycles induce tensile stress that can initiate micro-crack formation at weak points such as the TSV bottom and sidewall interfaces. These cyclic stress variations accelerate fatigue mechanisms and reduce the overall electromechanical stability of the TSV array.

Heat dissipation efficiency significantly impacts TSV stability evaluation methodologies. Poor thermal management leads to localized hot spots that create asymmetric stress distributions, making traditional stability assessment approaches less reliable. The thermal resistance of TSV structures affects the temperature profile across the 3D stack, influencing the magnitude and distribution of thermomechanical stress. Effective thermal interface materials and heat spreading techniques can mitigate these effects by reducing temperature gradients and minimizing CTE-induced stress concentrations.

Advanced thermal modeling techniques are essential for predicting TSV stability under various thermal conditions. Finite element analysis incorporating temperature-dependent material properties enables accurate simulation of thermomechanical behavior during operational scenarios. These models must account for the complex interactions between thermal cycling frequency, temperature range, and mechanical stress evolution to provide meaningful stability predictions.

The integration of real-time thermal monitoring systems enhances TSV stability evaluation by providing continuous feedback on temperature distribution and thermal transients. This approach enables dynamic assessment of electromechanical stability under actual operating conditions, improving the accuracy of reliability predictions and enabling proactive thermal management strategies to maintain optimal TSV performance throughout the device lifetime.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!