How to Select DSP Hardware for High-Frequency Applications

FEB 26, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DSP Hardware Evolution and High-Frequency Goals

Digital Signal Processing (DSP) hardware has undergone remarkable transformation since its inception in the 1970s, evolving from basic fixed-point processors to sophisticated multi-core architectures capable of handling complex high-frequency applications. The early DSP chips, such as Texas Instruments' TMS32010, operated at modest clock speeds and were primarily designed for audio processing and simple filtering tasks. These pioneering devices established the foundation for dedicated signal processing hardware, introducing specialized instruction sets optimized for mathematical operations common in signal processing algorithms.

The 1990s marked a significant acceleration in DSP evolution, driven by the telecommunications boom and the emergence of wireless communication standards. Processors began incorporating floating-point arithmetic units, enhanced memory architectures, and specialized peripherals for high-speed data acquisition. Companies like Analog Devices, Motorola, and Texas Instruments competed intensively, pushing clock speeds beyond 100 MHz and introducing innovative features such as dual-MAC (Multiply-Accumulate) units and specialized addressing modes for efficient algorithm implementation.

The transition into the 21st century brought revolutionary changes with the introduction of multi-core DSP architectures and the integration of FPGA (Field-Programmable Gate Array) capabilities. Modern DSP processors now operate at gigahertz frequencies, incorporating advanced features like SIMD (Single Instruction, Multiple Data) processing, dedicated accelerators for specific algorithms, and sophisticated cache hierarchies. The emergence of heterogeneous computing platforms has enabled the combination of traditional DSP cores with ARM processors, creating versatile solutions for complex signal processing applications.

Contemporary high-frequency applications demand unprecedented performance levels, particularly in areas such as 5G communications, radar systems, software-defined radio, and real-time spectrum analysis. These applications require DSP hardware capable of processing signals with bandwidths exceeding several gigahertz while maintaining low latency and high precision. The primary goals include achieving sampling rates in the multi-GSPS (Giga-Samples Per Second) range, implementing complex modulation schemes, and performing real-time beamforming and adaptive filtering operations.

Current technological objectives focus on maximizing throughput while minimizing power consumption, a critical consideration for portable and embedded high-frequency systems. Advanced DSP architectures now target specific performance metrics such as achieving processing delays under microseconds, supporting dynamic reconfiguration for adaptive algorithms, and providing seamless integration with high-speed ADCs and DACs operating at frequencies well into the microwave spectrum.

The 1990s marked a significant acceleration in DSP evolution, driven by the telecommunications boom and the emergence of wireless communication standards. Processors began incorporating floating-point arithmetic units, enhanced memory architectures, and specialized peripherals for high-speed data acquisition. Companies like Analog Devices, Motorola, and Texas Instruments competed intensively, pushing clock speeds beyond 100 MHz and introducing innovative features such as dual-MAC (Multiply-Accumulate) units and specialized addressing modes for efficient algorithm implementation.

The transition into the 21st century brought revolutionary changes with the introduction of multi-core DSP architectures and the integration of FPGA (Field-Programmable Gate Array) capabilities. Modern DSP processors now operate at gigahertz frequencies, incorporating advanced features like SIMD (Single Instruction, Multiple Data) processing, dedicated accelerators for specific algorithms, and sophisticated cache hierarchies. The emergence of heterogeneous computing platforms has enabled the combination of traditional DSP cores with ARM processors, creating versatile solutions for complex signal processing applications.

Contemporary high-frequency applications demand unprecedented performance levels, particularly in areas such as 5G communications, radar systems, software-defined radio, and real-time spectrum analysis. These applications require DSP hardware capable of processing signals with bandwidths exceeding several gigahertz while maintaining low latency and high precision. The primary goals include achieving sampling rates in the multi-GSPS (Giga-Samples Per Second) range, implementing complex modulation schemes, and performing real-time beamforming and adaptive filtering operations.

Current technological objectives focus on maximizing throughput while minimizing power consumption, a critical consideration for portable and embedded high-frequency systems. Advanced DSP architectures now target specific performance metrics such as achieving processing delays under microseconds, supporting dynamic reconfiguration for adaptive algorithms, and providing seamless integration with high-speed ADCs and DACs operating at frequencies well into the microwave spectrum.

Market Demand for High-Frequency DSP Solutions

The telecommunications industry represents the largest segment driving demand for high-frequency DSP solutions, particularly with the global rollout of 5G networks and the development of 6G technologies. Base station infrastructure requires sophisticated DSP hardware capable of processing massive MIMO signals, beamforming algorithms, and carrier aggregation across multiple frequency bands. The transition from sub-6GHz to millimeter-wave frequencies has intensified requirements for DSP processors with enhanced computational capabilities and reduced latency performance.

Radar and defense applications constitute another critical market segment, where high-frequency DSP solutions enable advanced target detection, electronic warfare systems, and synthetic aperture radar processing. Modern military communication systems demand DSP hardware that can operate across wide frequency spectrums while maintaining signal integrity and real-time processing capabilities. The increasing sophistication of autonomous weapon systems and surveillance technologies continues to expand market opportunities in this sector.

The automotive industry has emerged as a rapidly growing market for high-frequency DSP applications, driven by the proliferation of advanced driver assistance systems and autonomous vehicle technologies. Automotive radar systems operating at 77GHz and 79GHz frequencies require specialized DSP processors capable of real-time object detection, velocity measurement, and environmental mapping. Vehicle-to-everything communication protocols further amplify the demand for high-performance DSP solutions in automotive applications.

Medical imaging and diagnostic equipment represent a specialized but lucrative market segment for high-frequency DSP hardware. Ultrasound imaging systems, magnetic resonance imaging equipment, and computed tomography scanners rely on advanced DSP processors to handle complex signal processing algorithms and image reconstruction tasks. The trend toward portable and point-of-care medical devices has created additional demand for power-efficient, high-performance DSP solutions.

Industrial automation and Internet of Things applications are driving increased adoption of high-frequency DSP technologies across manufacturing sectors. Smart factory implementations require DSP hardware capable of processing sensor data, machine vision algorithms, and predictive maintenance analytics in real-time. The integration of artificial intelligence and machine learning capabilities into industrial systems has further expanded the market potential for advanced DSP processors.

The aerospace and satellite communication sectors continue to represent significant market opportunities, particularly with the deployment of low Earth orbit satellite constellations and deep space exploration missions. These applications demand DSP hardware with exceptional reliability, radiation tolerance, and processing capabilities to handle complex communication protocols and signal processing tasks in harsh environmental conditions.

Radar and defense applications constitute another critical market segment, where high-frequency DSP solutions enable advanced target detection, electronic warfare systems, and synthetic aperture radar processing. Modern military communication systems demand DSP hardware that can operate across wide frequency spectrums while maintaining signal integrity and real-time processing capabilities. The increasing sophistication of autonomous weapon systems and surveillance technologies continues to expand market opportunities in this sector.

The automotive industry has emerged as a rapidly growing market for high-frequency DSP applications, driven by the proliferation of advanced driver assistance systems and autonomous vehicle technologies. Automotive radar systems operating at 77GHz and 79GHz frequencies require specialized DSP processors capable of real-time object detection, velocity measurement, and environmental mapping. Vehicle-to-everything communication protocols further amplify the demand for high-performance DSP solutions in automotive applications.

Medical imaging and diagnostic equipment represent a specialized but lucrative market segment for high-frequency DSP hardware. Ultrasound imaging systems, magnetic resonance imaging equipment, and computed tomography scanners rely on advanced DSP processors to handle complex signal processing algorithms and image reconstruction tasks. The trend toward portable and point-of-care medical devices has created additional demand for power-efficient, high-performance DSP solutions.

Industrial automation and Internet of Things applications are driving increased adoption of high-frequency DSP technologies across manufacturing sectors. Smart factory implementations require DSP hardware capable of processing sensor data, machine vision algorithms, and predictive maintenance analytics in real-time. The integration of artificial intelligence and machine learning capabilities into industrial systems has further expanded the market potential for advanced DSP processors.

The aerospace and satellite communication sectors continue to represent significant market opportunities, particularly with the deployment of low Earth orbit satellite constellations and deep space exploration missions. These applications demand DSP hardware with exceptional reliability, radiation tolerance, and processing capabilities to handle complex communication protocols and signal processing tasks in harsh environmental conditions.

Current DSP Hardware Limitations in High-Frequency Apps

Current DSP hardware faces significant constraints when operating in high-frequency applications, primarily stemming from fundamental semiconductor physics and architectural limitations. The most critical bottleneck lies in the maximum clock frequencies achievable by contemporary DSP processors, which typically range from 1-2 GHz for high-performance floating-point units. This frequency ceiling creates substantial challenges when processing signals in the multi-gigahertz range, where real-time processing demands exceed the computational throughput capabilities of traditional DSP architectures.

Analog-to-digital converter integration presents another major limitation in high-frequency DSP systems. While standalone ADCs can achieve sampling rates exceeding 10 GSPS, integrated solutions within DSP platforms are typically constrained to much lower rates due to power consumption, thermal management, and die area considerations. This integration gap forces system designers to rely on external high-speed ADCs, introducing additional latency, power consumption, and board complexity that can compromise overall system performance.

Memory bandwidth and latency issues become increasingly pronounced at high frequencies. Traditional DSP architectures rely heavily on external memory for data storage and coefficient tables, but the memory interface bandwidth often becomes the limiting factor in high-throughput applications. The latency associated with memory access can introduce processing delays that are unacceptable in real-time high-frequency applications, particularly those requiring deterministic response times.

Power consumption and thermal management represent critical constraints that intensify with frequency scaling. High-frequency DSP operations demand increased clock rates and parallel processing units, leading to exponential growth in power dissipation. Current DSP hardware struggles to maintain acceptable power efficiency while delivering the computational performance required for high-frequency signal processing, often resulting in thermal throttling that degrades performance.

Precision and quantization limitations become more apparent in high-frequency applications where signal-to-noise ratios are critical. Many DSP processors utilize fixed-point arithmetic to achieve higher performance, but this approach can introduce quantization errors that accumulate over complex processing chains. While floating-point units offer better precision, they typically operate at lower clock frequencies and consume significantly more power, creating a fundamental trade-off between accuracy and performance.

The architectural rigidity of current DSP platforms also constrains their adaptability to diverse high-frequency applications. Most DSP processors are optimized for specific signal processing tasks, making them less suitable for applications requiring flexible processing pipelines or custom algorithms. This limitation becomes particularly problematic in emerging high-frequency applications such as cognitive radio, advanced radar systems, and high-speed communications protocols that demand adaptive processing capabilities.

Analog-to-digital converter integration presents another major limitation in high-frequency DSP systems. While standalone ADCs can achieve sampling rates exceeding 10 GSPS, integrated solutions within DSP platforms are typically constrained to much lower rates due to power consumption, thermal management, and die area considerations. This integration gap forces system designers to rely on external high-speed ADCs, introducing additional latency, power consumption, and board complexity that can compromise overall system performance.

Memory bandwidth and latency issues become increasingly pronounced at high frequencies. Traditional DSP architectures rely heavily on external memory for data storage and coefficient tables, but the memory interface bandwidth often becomes the limiting factor in high-throughput applications. The latency associated with memory access can introduce processing delays that are unacceptable in real-time high-frequency applications, particularly those requiring deterministic response times.

Power consumption and thermal management represent critical constraints that intensify with frequency scaling. High-frequency DSP operations demand increased clock rates and parallel processing units, leading to exponential growth in power dissipation. Current DSP hardware struggles to maintain acceptable power efficiency while delivering the computational performance required for high-frequency signal processing, often resulting in thermal throttling that degrades performance.

Precision and quantization limitations become more apparent in high-frequency applications where signal-to-noise ratios are critical. Many DSP processors utilize fixed-point arithmetic to achieve higher performance, but this approach can introduce quantization errors that accumulate over complex processing chains. While floating-point units offer better precision, they typically operate at lower clock frequencies and consume significantly more power, creating a fundamental trade-off between accuracy and performance.

The architectural rigidity of current DSP platforms also constrains their adaptability to diverse high-frequency applications. Most DSP processors are optimized for specific signal processing tasks, making them less suitable for applications requiring flexible processing pipelines or custom algorithms. This limitation becomes particularly problematic in emerging high-frequency applications such as cognitive radio, advanced radar systems, and high-speed communications protocols that demand adaptive processing capabilities.

Mainstream DSP Selection Methodologies

01 DSP processor architecture and design

Digital Signal Processors feature specialized architectures optimized for signal processing operations. These architectures include dedicated hardware units for multiplication, accumulation, and data addressing. The designs incorporate parallel processing capabilities, pipelining structures, and specialized instruction sets to efficiently handle real-time signal processing tasks. Advanced architectures may include multiple processing cores, configurable logic blocks, and optimized memory hierarchies to enhance computational performance.- DSP processor architecture and design: Digital Signal Processors feature specialized architectures optimized for signal processing operations. These architectures include dedicated hardware units for mathematical operations, parallel processing capabilities, and optimized instruction sets. The designs focus on high-speed computation, low power consumption, and efficient data handling for real-time signal processing applications.

- DSP hardware acceleration and coprocessing: Hardware acceleration techniques enhance DSP performance through dedicated coprocessors and specialized functional units. These implementations include hardware accelerators for specific algorithms, coprocessing modules for parallel computation, and dedicated circuits for intensive mathematical operations. The acceleration mechanisms improve processing speed and reduce computational burden on the main processor.

- DSP memory architecture and data management: Memory systems in DSP hardware incorporate specialized architectures for efficient data access and storage. These include multi-port memory configurations, cache hierarchies, and direct memory access controllers. The designs optimize data throughput, minimize access latency, and support high-bandwidth requirements for signal processing operations.

- DSP interface and peripheral integration: Interface designs for DSP systems encompass various communication protocols and peripheral connections. These implementations include serial and parallel interfaces, bus architectures, and protocol converters. The integration supports connectivity with external devices, sensors, and other processing units for comprehensive signal processing systems.

- DSP power management and optimization: Power management techniques in DSP hardware focus on reducing energy consumption while maintaining performance. These approaches include dynamic voltage and frequency scaling, clock gating, power domain isolation, and low-power operating modes. The optimization strategies balance processing requirements with energy efficiency for battery-powered and embedded applications.

02 DSP hardware acceleration and coprocessing units

Hardware acceleration modules are integrated into DSP systems to offload specific computational tasks from the main processor. These units include dedicated coprocessors for operations such as Fast Fourier Transform, filtering, and matrix operations. The acceleration hardware provides enhanced performance for computationally intensive algorithms while reducing power consumption and processing latency. These modules can be implemented as fixed-function units or configurable hardware blocks.Expand Specific Solutions03 DSP memory systems and data management

Memory architectures in DSP hardware are designed to support high-bandwidth data access and efficient data movement. These systems incorporate multiple memory banks, cache hierarchies, and direct memory access controllers. The memory organization enables simultaneous access to multiple data streams and minimizes memory access conflicts. Advanced implementations include specialized addressing modes and memory management units optimized for signal processing data patterns.Expand Specific Solutions04 DSP interface and peripheral integration

Interface hardware in DSP systems provides connectivity to external devices and data sources. These interfaces include serial and parallel communication ports, analog-to-digital and digital-to-analog converters, and standard communication protocols. The peripheral integration enables real-time data acquisition, processing, and output. Hardware implementations support various interface standards and provide flexible configuration options for different application requirements.Expand Specific Solutions05 DSP power management and optimization

Power management hardware in DSP systems implements techniques to reduce energy consumption while maintaining performance. These implementations include dynamic voltage and frequency scaling, clock gating, and power domain isolation. The hardware supports multiple operating modes with different power-performance trade-offs. Advanced designs incorporate adaptive power management that adjusts operating parameters based on workload characteristics and thermal conditions.Expand Specific Solutions

Leading DSP Chip Manufacturers and Market Players

The DSP hardware selection landscape for high-frequency applications represents a mature, highly competitive market with significant technological sophistication. The industry has evolved beyond early development stages, with established players like Analog Devices, Intel, Qualcomm, and Samsung Electronics leading through decades of innovation in signal processing architectures. Market dynamics are driven by expanding 5G infrastructure, automotive electronics, and IoT applications, creating substantial growth opportunities. Technology maturity varies significantly across segments, with companies like Microchip Technology and MediaTek focusing on specialized embedded solutions, while Huawei and Qualcomm push advanced mobile processing boundaries. The competitive landscape features both horizontal integration across multiple semiconductor domains and vertical specialization in specific DSP applications, reflecting the diverse requirements of high-frequency signal processing across telecommunications, automotive, and industrial sectors.

Analog Devices, Inc.

Technical Solution: ADI provides comprehensive DSP solutions for high-frequency applications through their SHARC and Blackfin processor families. Their ADSP-SC5xx series offers dual-core ARM Cortex-A5 processors with SHARC+ DSP cores, delivering up to 1.0 GHz processing speeds and specialized floating-point performance for demanding signal processing tasks. The company's DSPs feature advanced on-chip peripherals including high-speed ADCs, DACs, and serial ports optimized for real-time processing. ADI's hardware selection methodology emphasizes matching DSP architecture to specific frequency domain requirements, considering factors like sampling rates, filter complexity, and power consumption constraints in RF and communications applications.

Strengths: Industry-leading floating-point DSP performance, comprehensive development tools, proven reliability in high-frequency applications. Weaknesses: Higher cost compared to competitors, complex development environment for beginners.

Microchip Technology, Inc.

Technical Solution: Microchip's DSP hardware selection methodology for high-frequency applications centers on their dsPIC and PIC32 families with integrated DSP capabilities. Their approach emphasizes cost-effective solutions for mid-range frequency applications, typically supporting sampling rates up to several hundred MHz. The company's selection framework considers factors such as peripheral integration, development complexity, and long-term availability for industrial applications. Microchip's DSPs feature dedicated multiply-accumulate units, barrel shifters, and specialized addressing modes optimized for digital filtering and control algorithms. Their hardware selection tools help engineers evaluate trade-offs between processing performance, power consumption, and system cost. The company provides extensive application notes covering DSP implementation techniques for motor control, power conversion, and audio processing applications where moderate high-frequency performance is required.

Strengths: Cost-effective solutions, excellent peripheral integration, strong support for industrial applications. Weaknesses: Limited performance for highest frequency applications, smaller ecosystem compared to major DSP vendors.

Critical DSP Performance Parameters Analysis

Digital signal processor (DSP) with global and local interconnect architecture and reconfigurable hardware accelerator core

PatentActiveUS12314215B1

Innovation

- A digital signal processor (DSP) with a global and local interconnect architecture, featuring multiple DSP hardware accelerator cores with user-configurable DSP modules and memory-mapped data transfers, enabling efficient data transfer and flexible operation.

Virtual CCAP cable modem termination system with software reconfiguable mac and PHY capability

PatentActiveUS20140150047A1

Innovation

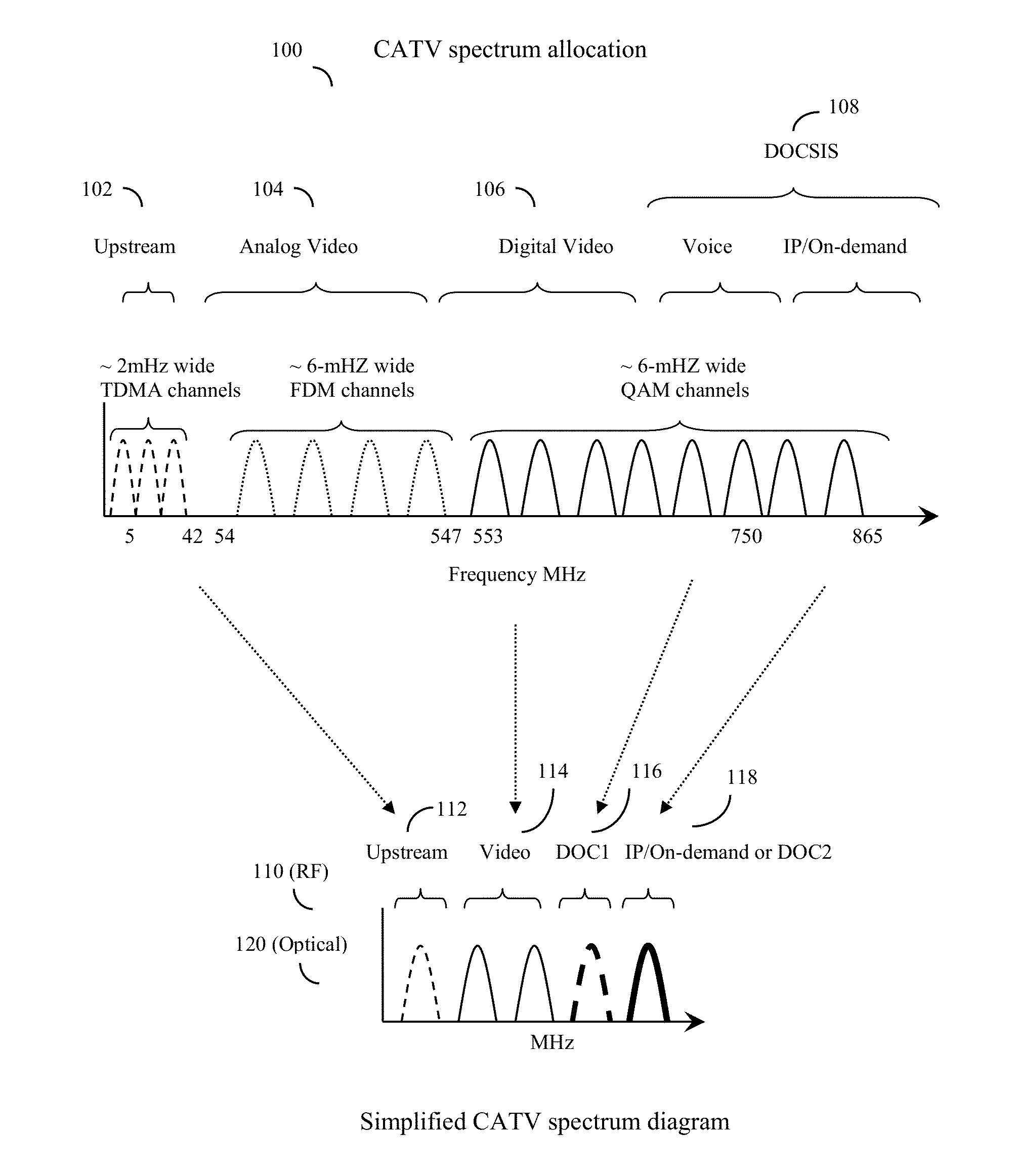

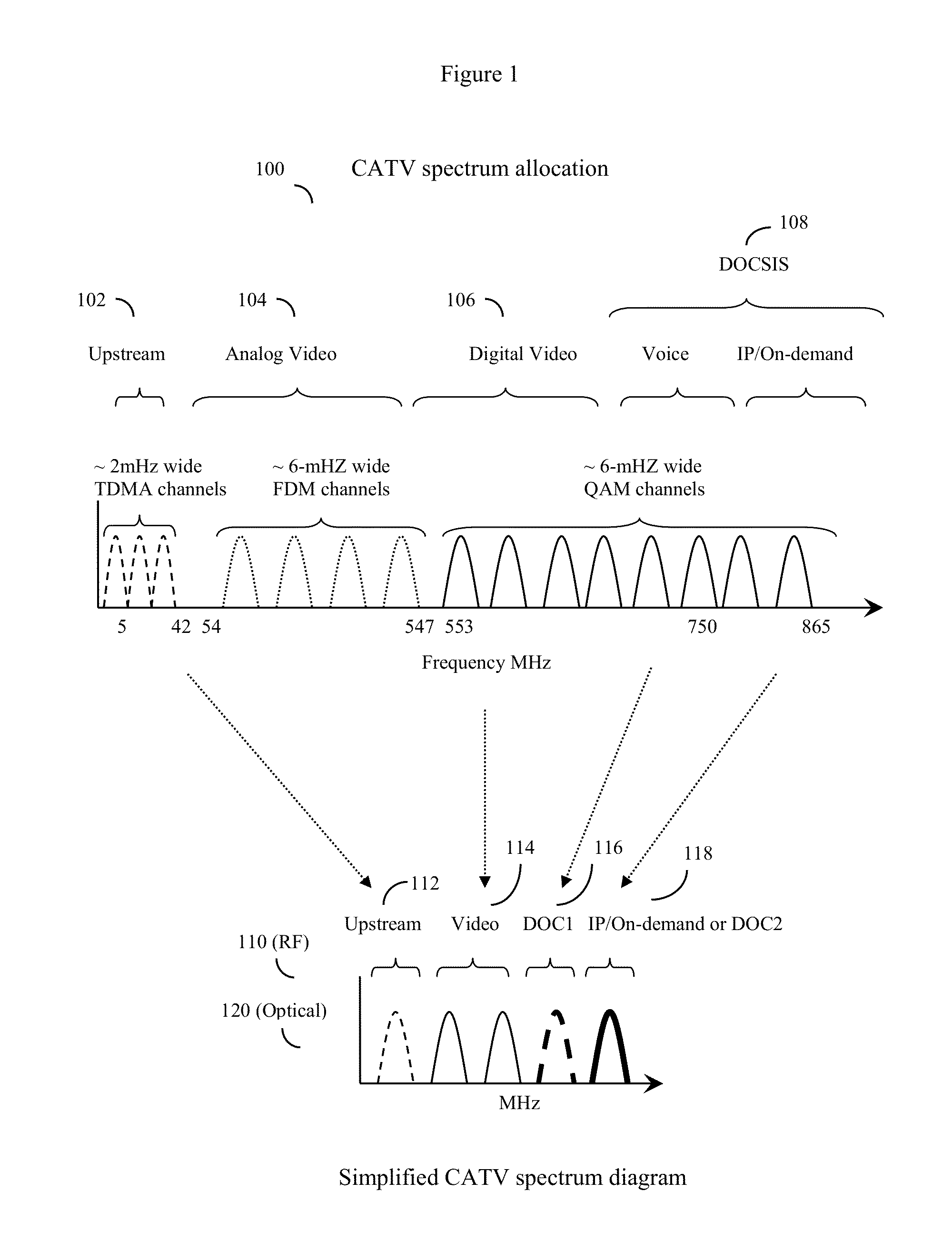

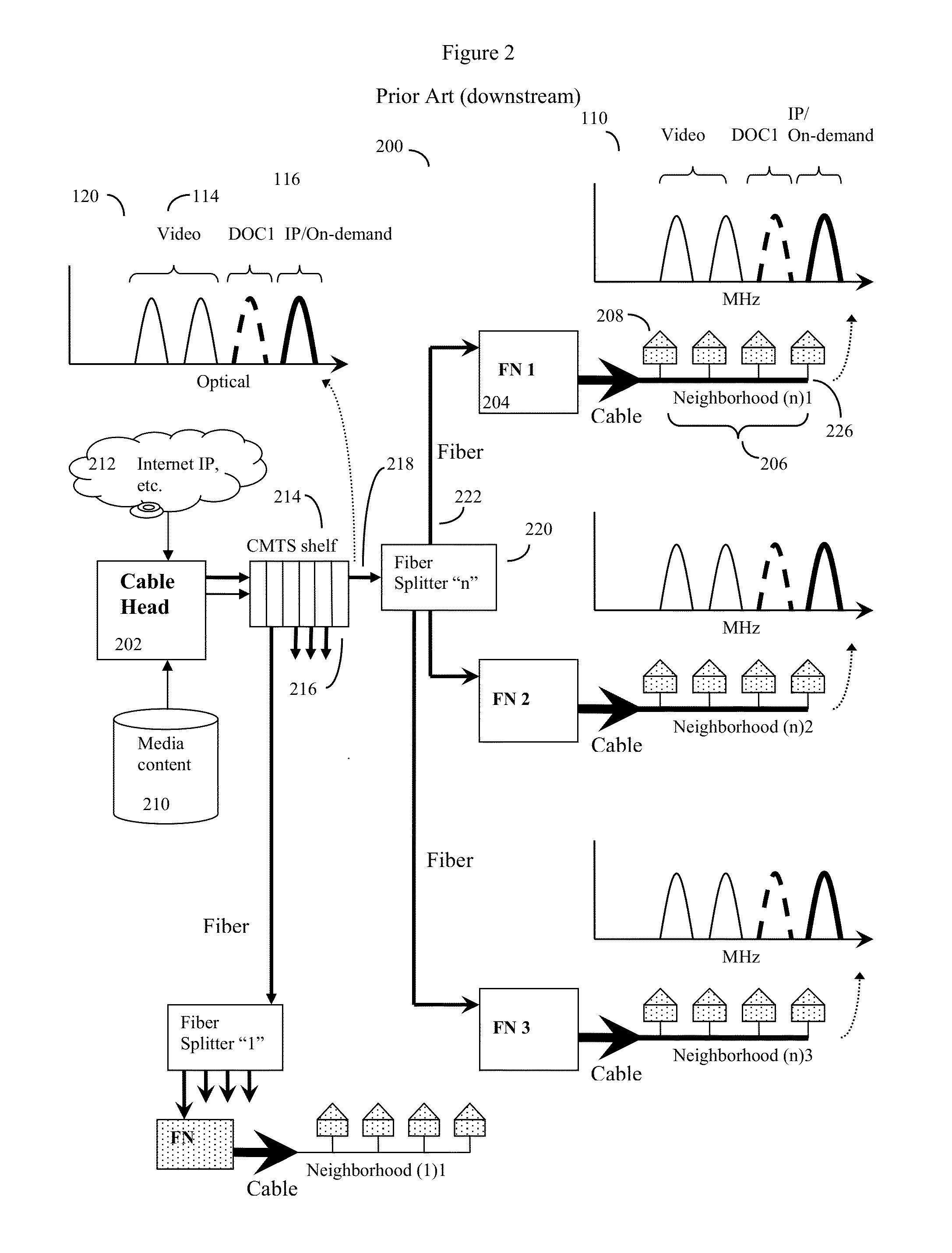

- A distributed Cable Modem Termination System (CMTS) is introduced, utilizing software reconfigurable Field-Programmable Gate Array (FPGA) and Digital Signal Processor (DSP) based RF modulators to dynamically manage and optimize data transmission between coaxial cables and optical fibers, allowing for increased flexibility and efficiency in data delivery by dividing CMTS functions between central and remote nodes, thereby enhancing bandwidth utilization without requiring extensive infrastructure changes.

DSP Hardware Benchmarking and Evaluation Frameworks

Establishing comprehensive benchmarking and evaluation frameworks is essential for systematically assessing DSP hardware performance in high-frequency applications. These frameworks provide standardized methodologies to compare different DSP solutions objectively, ensuring that selection decisions are based on quantifiable metrics rather than vendor specifications alone.

Performance benchmarking frameworks typically encompass multiple evaluation dimensions including computational throughput, latency characteristics, power efficiency, and thermal behavior under various operational conditions. Standard benchmark suites such as BDTI (Berkeley Design Technology Inc.) benchmarks, EEMBC (Embedded Microprocessor Benchmark Consortium) DSP benchmarks, and custom application-specific test vectors form the foundation of rigorous evaluation processes.

Real-time performance evaluation requires specialized testing methodologies that simulate actual high-frequency signal processing scenarios. These frameworks incorporate signal generators, high-speed data acquisition systems, and precision timing measurement equipment to assess DSP performance under realistic operating conditions. Critical metrics include interrupt response times, context switching overhead, and sustained processing rates under continuous data streams.

Multi-criteria evaluation frameworks integrate technical performance metrics with practical implementation considerations. These comprehensive assessment models weight factors such as development complexity, debugging capabilities, software ecosystem maturity, and long-term vendor support alongside raw performance indicators. Decision matrices and scoring algorithms help quantify trade-offs between competing DSP solutions.

Standardized test environments ensure reproducible and comparable results across different DSP platforms. These controlled testing frameworks specify environmental conditions, power supply characteristics, thermal management requirements, and measurement instrumentation configurations. Automated testing suites enable consistent evaluation procedures while reducing human error and measurement variability.

Industry-specific benchmarking frameworks address unique requirements of different high-frequency application domains. Radar processing benchmarks emphasize pulse compression and beamforming algorithms, while communications-focused frameworks prioritize modulation, demodulation, and channel coding performance. Software-defined radio benchmarks evaluate wideband signal processing and adaptive filtering capabilities.

Validation frameworks incorporate statistical analysis methods to ensure measurement reliability and significance. These methodologies account for performance variations, establish confidence intervals, and identify optimal operating points for specific application requirements, providing robust foundations for hardware selection decisions.

Performance benchmarking frameworks typically encompass multiple evaluation dimensions including computational throughput, latency characteristics, power efficiency, and thermal behavior under various operational conditions. Standard benchmark suites such as BDTI (Berkeley Design Technology Inc.) benchmarks, EEMBC (Embedded Microprocessor Benchmark Consortium) DSP benchmarks, and custom application-specific test vectors form the foundation of rigorous evaluation processes.

Real-time performance evaluation requires specialized testing methodologies that simulate actual high-frequency signal processing scenarios. These frameworks incorporate signal generators, high-speed data acquisition systems, and precision timing measurement equipment to assess DSP performance under realistic operating conditions. Critical metrics include interrupt response times, context switching overhead, and sustained processing rates under continuous data streams.

Multi-criteria evaluation frameworks integrate technical performance metrics with practical implementation considerations. These comprehensive assessment models weight factors such as development complexity, debugging capabilities, software ecosystem maturity, and long-term vendor support alongside raw performance indicators. Decision matrices and scoring algorithms help quantify trade-offs between competing DSP solutions.

Standardized test environments ensure reproducible and comparable results across different DSP platforms. These controlled testing frameworks specify environmental conditions, power supply characteristics, thermal management requirements, and measurement instrumentation configurations. Automated testing suites enable consistent evaluation procedures while reducing human error and measurement variability.

Industry-specific benchmarking frameworks address unique requirements of different high-frequency application domains. Radar processing benchmarks emphasize pulse compression and beamforming algorithms, while communications-focused frameworks prioritize modulation, demodulation, and channel coding performance. Software-defined radio benchmarks evaluate wideband signal processing and adaptive filtering capabilities.

Validation frameworks incorporate statistical analysis methods to ensure measurement reliability and significance. These methodologies account for performance variations, establish confidence intervals, and identify optimal operating points for specific application requirements, providing robust foundations for hardware selection decisions.

Power Efficiency Considerations in High-Speed DSP Design

Power efficiency stands as a critical design parameter in high-speed DSP systems, directly impacting thermal management, battery life, and overall system reliability. As processing frequencies increase and computational demands grow, the challenge of maintaining optimal power consumption while delivering required performance becomes increasingly complex. Modern high-frequency DSP applications must balance aggressive performance targets with stringent power budgets, particularly in mobile, automotive, and aerospace applications where thermal constraints and energy availability impose strict limitations.

Dynamic power consumption represents the primary concern in high-speed DSP design, scaling quadratically with supply voltage and linearly with operating frequency. Advanced power management techniques such as dynamic voltage and frequency scaling (DVFS) enable real-time adjustment of operating parameters based on computational workload. Clock gating and power gating strategies selectively disable unused functional units, reducing both dynamic and static power consumption during idle periods.

Architectural considerations play a fundamental role in power efficiency optimization. Parallel processing architectures distribute computational load across multiple lower-frequency cores, often achieving better power efficiency than single high-frequency processors. Pipeline depth optimization balances throughput requirements with power overhead, as deeper pipelines may reduce operating voltage but increase instruction overhead and complexity.

Advanced process technologies offer significant power efficiency improvements through reduced supply voltages and enhanced transistor characteristics. FinFET and SOI technologies provide better control over leakage currents while enabling higher switching speeds. Multi-threshold voltage designs allow selective use of high-performance transistors in critical paths while employing low-leakage devices in non-critical areas.

System-level power optimization encompasses memory hierarchy design, interconnect efficiency, and algorithmic optimization. Efficient cache architectures reduce memory access power, while optimized data flow patterns minimize unnecessary data movement. Algorithm-architecture co-design approaches identify opportunities for computational complexity reduction and hardware acceleration, achieving substantial power savings through specialized processing units and optimized data paths tailored to specific DSP algorithms.

Dynamic power consumption represents the primary concern in high-speed DSP design, scaling quadratically with supply voltage and linearly with operating frequency. Advanced power management techniques such as dynamic voltage and frequency scaling (DVFS) enable real-time adjustment of operating parameters based on computational workload. Clock gating and power gating strategies selectively disable unused functional units, reducing both dynamic and static power consumption during idle periods.

Architectural considerations play a fundamental role in power efficiency optimization. Parallel processing architectures distribute computational load across multiple lower-frequency cores, often achieving better power efficiency than single high-frequency processors. Pipeline depth optimization balances throughput requirements with power overhead, as deeper pipelines may reduce operating voltage but increase instruction overhead and complexity.

Advanced process technologies offer significant power efficiency improvements through reduced supply voltages and enhanced transistor characteristics. FinFET and SOI technologies provide better control over leakage currents while enabling higher switching speeds. Multi-threshold voltage designs allow selective use of high-performance transistors in critical paths while employing low-leakage devices in non-critical areas.

System-level power optimization encompasses memory hierarchy design, interconnect efficiency, and algorithmic optimization. Efficient cache architectures reduce memory access power, while optimized data flow patterns minimize unnecessary data movement. Algorithm-architecture co-design approaches identify opportunities for computational complexity reduction and hardware acceleration, achieving substantial power savings through specialized processing units and optimized data paths tailored to specific DSP algorithms.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!