Compare RISC Solutions for High-Tech Industry Implementation

MAR 26, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RISC Architecture Evolution and Implementation Goals

RISC (Reduced Instruction Set Computer) architecture emerged in the early 1980s as a revolutionary computing paradigm that challenged the prevailing Complex Instruction Set Computer (CISC) approach. The foundational concept originated from research conducted at UC Berkeley and Stanford University, where engineers recognized that simplifying processor instruction sets could dramatically improve performance through enhanced execution efficiency and reduced hardware complexity.

The evolution of RISC architecture has progressed through several distinct phases, beginning with the pioneering Berkeley RISC I and RISC II processors, followed by Stanford's MIPS architecture. These early implementations demonstrated that processors could achieve superior performance by executing simple instructions at higher frequencies rather than complex instructions at lower speeds. The philosophy centered on optimizing the most frequently used operations while relegating complex tasks to software implementations.

Throughout the 1990s and 2000s, RISC architecture matured significantly with the development of advanced features including superscalar execution, out-of-order processing, and sophisticated branch prediction mechanisms. Major architectural families such as ARM, PowerPC, and SPARC emerged during this period, each targeting specific market segments and application requirements. The ARM architecture particularly gained prominence in mobile and embedded systems due to its exceptional power efficiency characteristics.

The contemporary RISC landscape has expanded beyond traditional boundaries, encompassing specialized implementations for artificial intelligence, edge computing, and high-performance computing applications. Modern RISC processors integrate advanced features such as vector processing units, hardware accelerators, and heterogeneous computing capabilities to address diverse computational workloads in high-tech industries.

Current implementation goals for RISC solutions in high-tech industries focus on achieving optimal balance between performance, power consumption, and cost-effectiveness. Organizations seek architectures that can efficiently handle emerging workloads including machine learning inference, real-time data processing, and IoT connectivity while maintaining scalability for future technological demands. The emphasis has shifted toward customizable and extensible architectures that enable domain-specific optimizations.

The strategic objectives driving RISC adoption include reducing total cost of ownership, improving system integration flexibility, and achieving greater control over hardware-software co-design processes. High-tech companies increasingly prioritize architectures that support rapid prototyping, facilitate intellectual property development, and enable differentiation in competitive markets through specialized processing capabilities tailored to specific application requirements.

The evolution of RISC architecture has progressed through several distinct phases, beginning with the pioneering Berkeley RISC I and RISC II processors, followed by Stanford's MIPS architecture. These early implementations demonstrated that processors could achieve superior performance by executing simple instructions at higher frequencies rather than complex instructions at lower speeds. The philosophy centered on optimizing the most frequently used operations while relegating complex tasks to software implementations.

Throughout the 1990s and 2000s, RISC architecture matured significantly with the development of advanced features including superscalar execution, out-of-order processing, and sophisticated branch prediction mechanisms. Major architectural families such as ARM, PowerPC, and SPARC emerged during this period, each targeting specific market segments and application requirements. The ARM architecture particularly gained prominence in mobile and embedded systems due to its exceptional power efficiency characteristics.

The contemporary RISC landscape has expanded beyond traditional boundaries, encompassing specialized implementations for artificial intelligence, edge computing, and high-performance computing applications. Modern RISC processors integrate advanced features such as vector processing units, hardware accelerators, and heterogeneous computing capabilities to address diverse computational workloads in high-tech industries.

Current implementation goals for RISC solutions in high-tech industries focus on achieving optimal balance between performance, power consumption, and cost-effectiveness. Organizations seek architectures that can efficiently handle emerging workloads including machine learning inference, real-time data processing, and IoT connectivity while maintaining scalability for future technological demands. The emphasis has shifted toward customizable and extensible architectures that enable domain-specific optimizations.

The strategic objectives driving RISC adoption include reducing total cost of ownership, improving system integration flexibility, and achieving greater control over hardware-software co-design processes. High-tech companies increasingly prioritize architectures that support rapid prototyping, facilitate intellectual property development, and enable differentiation in competitive markets through specialized processing capabilities tailored to specific application requirements.

High-Tech Industry Demand for RISC Solutions

The high-tech industry's demand for RISC solutions has experienced unprecedented growth driven by the convergence of artificial intelligence, edge computing, and Internet of Things applications. Traditional x86 architectures face increasing limitations in power efficiency and performance per watt metrics, creating substantial market opportunities for RISC-based processors. This shift represents a fundamental transformation in computing paradigms, where energy efficiency and specialized workload optimization take precedence over raw computational power.

Data center operators and cloud service providers constitute the largest demand segment, seeking RISC solutions to reduce operational costs and improve thermal management. The proliferation of containerized applications and microservices architectures aligns perfectly with RISC processors' lightweight design philosophy. Major hyperscale companies are actively evaluating RISC alternatives to reduce dependency on traditional processor vendors while achieving better total cost of ownership.

Mobile and embedded systems markets demonstrate particularly strong adoption patterns for RISC architectures. The exponential growth of smart devices, autonomous vehicles, and industrial automation systems requires processors that deliver optimal performance within strict power budgets. RISC solutions excel in these applications by providing deterministic performance characteristics and simplified instruction sets that enable more predictable real-time behavior.

The artificial intelligence and machine learning sector represents an emerging high-growth demand area for specialized RISC implementations. Custom silicon designs based on RISC architectures enable companies to optimize inference engines and training accelerators for specific neural network topologies. This customization capability provides significant competitive advantages in rapidly evolving AI markets where algorithmic innovations require corresponding hardware optimizations.

Enterprise software vendors increasingly recognize RISC processors' potential for improving application performance while reducing infrastructure costs. The open-source nature of many RISC instruction set architectures enables greater flexibility in processor design and reduces licensing expenses compared to proprietary alternatives. This economic advantage becomes particularly compelling for companies developing specialized computing appliances or embedded systems requiring long-term support commitments.

Telecommunications infrastructure modernization drives additional demand as network operators transition to software-defined networking and network function virtualization architectures. RISC processors offer superior packet processing capabilities and lower latency characteristics essential for next-generation communication systems. The industry's shift toward disaggregated hardware architectures further amplifies demand for flexible, efficient processor solutions that can adapt to diverse networking workloads.

Data center operators and cloud service providers constitute the largest demand segment, seeking RISC solutions to reduce operational costs and improve thermal management. The proliferation of containerized applications and microservices architectures aligns perfectly with RISC processors' lightweight design philosophy. Major hyperscale companies are actively evaluating RISC alternatives to reduce dependency on traditional processor vendors while achieving better total cost of ownership.

Mobile and embedded systems markets demonstrate particularly strong adoption patterns for RISC architectures. The exponential growth of smart devices, autonomous vehicles, and industrial automation systems requires processors that deliver optimal performance within strict power budgets. RISC solutions excel in these applications by providing deterministic performance characteristics and simplified instruction sets that enable more predictable real-time behavior.

The artificial intelligence and machine learning sector represents an emerging high-growth demand area for specialized RISC implementations. Custom silicon designs based on RISC architectures enable companies to optimize inference engines and training accelerators for specific neural network topologies. This customization capability provides significant competitive advantages in rapidly evolving AI markets where algorithmic innovations require corresponding hardware optimizations.

Enterprise software vendors increasingly recognize RISC processors' potential for improving application performance while reducing infrastructure costs. The open-source nature of many RISC instruction set architectures enables greater flexibility in processor design and reduces licensing expenses compared to proprietary alternatives. This economic advantage becomes particularly compelling for companies developing specialized computing appliances or embedded systems requiring long-term support commitments.

Telecommunications infrastructure modernization drives additional demand as network operators transition to software-defined networking and network function virtualization architectures. RISC processors offer superior packet processing capabilities and lower latency characteristics essential for next-generation communication systems. The industry's shift toward disaggregated hardware architectures further amplifies demand for flexible, efficient processor solutions that can adapt to diverse networking workloads.

Current RISC Ecosystem Status and Challenges

The RISC-V ecosystem has experienced remarkable growth since its inception at UC Berkeley in 2010, evolving from an academic research project into a commercially viable alternative to proprietary instruction set architectures. The open-source nature of RISC-V has attracted significant industry attention, with over 3,000 members joining the RISC-V International organization by 2024. Major technology companies including Google, Intel, Nvidia, and Qualcomm have invested heavily in RISC-V development, signaling strong market confidence in the architecture's potential.

Current market adoption shows promising momentum across multiple sectors. The embedded systems market has emerged as the primary driver, with RISC-V processors gaining traction in IoT devices, microcontrollers, and edge computing applications. Data centers and high-performance computing represent emerging opportunities, though adoption remains limited compared to established x86 and ARM architectures. The automotive industry has shown particular interest, with several manufacturers exploring RISC-V for autonomous driving and infotainment systems.

Despite positive trends, the RISC-V ecosystem faces significant technical and commercial challenges. Software ecosystem maturity remains a critical bottleneck, with limited availability of optimized compilers, debuggers, and development tools compared to established architectures. The fragmentation risk poses another concern, as the modular nature of RISC-V allows for numerous custom extensions, potentially creating compatibility issues across different implementations.

Performance optimization represents a persistent challenge, particularly for high-performance computing applications. While RISC-V demonstrates competitive performance in specific use cases, achieving parity with mature x86 and ARM processors in general-purpose computing requires substantial engineering investment. The lack of standardized performance benchmarks across different RISC-V implementations complicates objective performance evaluation for potential adopters.

Market penetration barriers include established vendor relationships and switching costs associated with migrating from existing architectures. Enterprise customers often hesitate to adopt RISC-V due to concerns about long-term support, ecosystem stability, and the availability of skilled developers. Additionally, the current shortage of production-ready, high-performance RISC-V processors limits immediate deployment options for demanding applications.

The geographic distribution of RISC-V development shows concentration in North America, Europe, and Asia, with China demonstrating particularly aggressive adoption driven by strategic independence considerations. However, this geographic fragmentation sometimes leads to duplicated efforts and inconsistent development priorities, potentially slowing overall ecosystem maturation.

Current market adoption shows promising momentum across multiple sectors. The embedded systems market has emerged as the primary driver, with RISC-V processors gaining traction in IoT devices, microcontrollers, and edge computing applications. Data centers and high-performance computing represent emerging opportunities, though adoption remains limited compared to established x86 and ARM architectures. The automotive industry has shown particular interest, with several manufacturers exploring RISC-V for autonomous driving and infotainment systems.

Despite positive trends, the RISC-V ecosystem faces significant technical and commercial challenges. Software ecosystem maturity remains a critical bottleneck, with limited availability of optimized compilers, debuggers, and development tools compared to established architectures. The fragmentation risk poses another concern, as the modular nature of RISC-V allows for numerous custom extensions, potentially creating compatibility issues across different implementations.

Performance optimization represents a persistent challenge, particularly for high-performance computing applications. While RISC-V demonstrates competitive performance in specific use cases, achieving parity with mature x86 and ARM processors in general-purpose computing requires substantial engineering investment. The lack of standardized performance benchmarks across different RISC-V implementations complicates objective performance evaluation for potential adopters.

Market penetration barriers include established vendor relationships and switching costs associated with migrating from existing architectures. Enterprise customers often hesitate to adopt RISC-V due to concerns about long-term support, ecosystem stability, and the availability of skilled developers. Additionally, the current shortage of production-ready, high-performance RISC-V processors limits immediate deployment options for demanding applications.

The geographic distribution of RISC-V development shows concentration in North America, Europe, and Asia, with China demonstrating particularly aggressive adoption driven by strategic independence considerations. However, this geographic fragmentation sometimes leads to duplicated efforts and inconsistent development priorities, potentially slowing overall ecosystem maturation.

Mainstream RISC Implementation Approaches

01 RISC processor architecture and instruction set design

RISC (Reduced Instruction Set Computer) architecture focuses on simplified instruction sets that execute in a single clock cycle. This approach emphasizes a streamlined set of instructions that can be processed more efficiently, leading to improved performance and reduced complexity in processor design. The architecture typically features load-store operations, fixed-length instructions, and a large number of general-purpose registers to optimize execution speed.- RISC processor architecture and instruction set design: RISC (Reduced Instruction Set Computer) architecture focuses on simplified instruction sets that execute in a single clock cycle. This approach emphasizes a streamlined set of instructions that can be processed more efficiently, leading to improved performance and reduced complexity in processor design. The architecture typically features load-store operations, fixed-length instructions, and a large number of general-purpose registers to optimize execution speed.

- RISC-based microprocessor implementation and optimization: Implementation techniques for RISC-based microprocessors involve hardware optimization strategies to maximize throughput and minimize latency. These solutions include pipeline optimization, branch prediction mechanisms, and cache management systems. The focus is on achieving high performance through efficient hardware utilization and parallel processing capabilities while maintaining low power consumption.

- RISC processor security and protection mechanisms: Security solutions for RISC processors incorporate various protection mechanisms to safeguard against unauthorized access and malicious attacks. These include memory protection units, secure boot processes, and hardware-based encryption capabilities. The implementations focus on maintaining system integrity while ensuring that security features do not significantly impact processor performance.

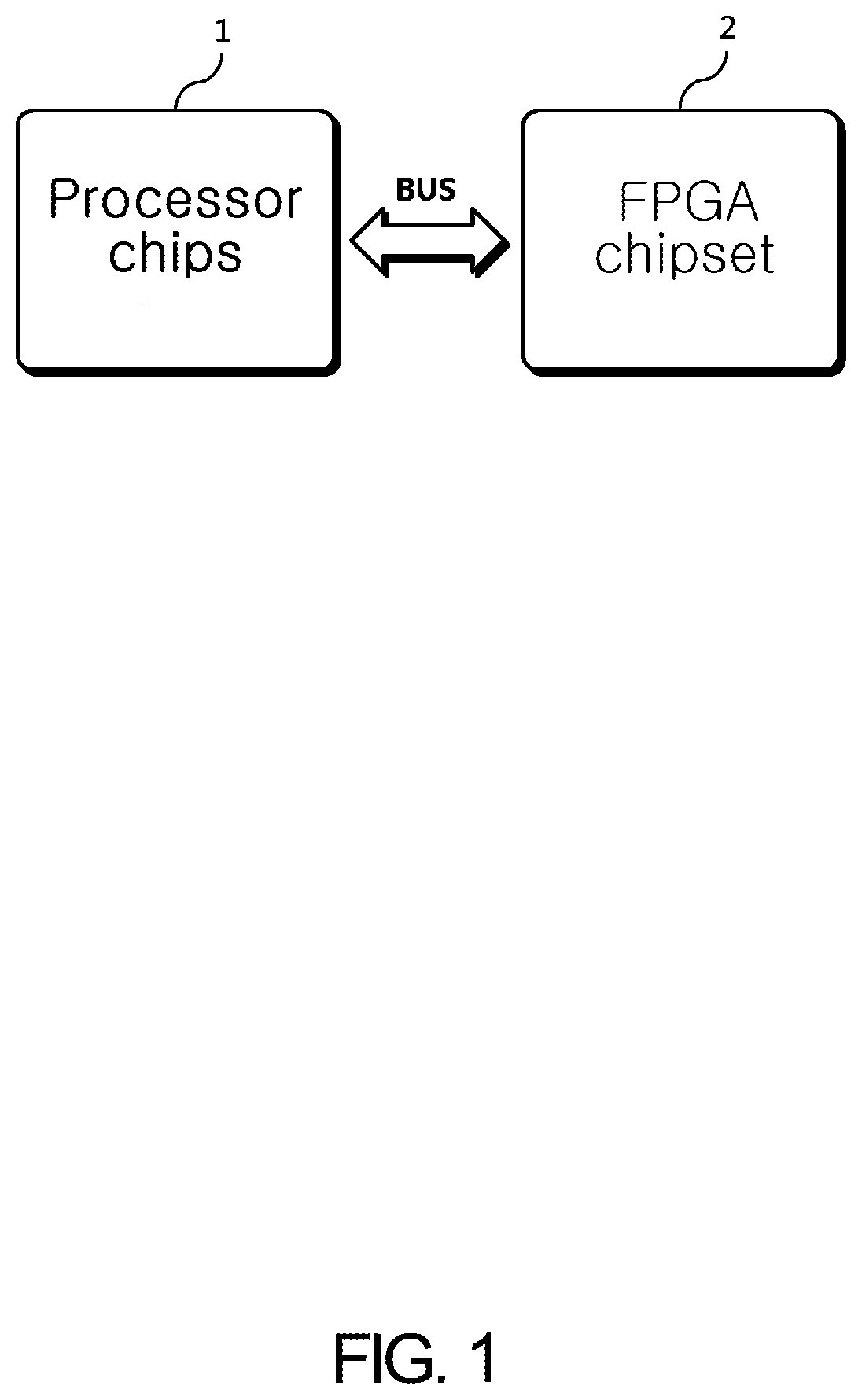

- RISC system integration and communication interfaces: Integration solutions for RISC-based systems address the challenges of connecting processors with peripheral devices and external systems. These solutions encompass bus architectures, interrupt handling mechanisms, and input-output management systems. The focus is on creating efficient communication pathways that enable seamless data transfer while maintaining system responsiveness and reliability.

- Advanced RISC computing applications and system-on-chip solutions: Modern RISC computing solutions extend to complex system-on-chip implementations that integrate multiple functional units on a single chip. These advanced applications include embedded systems, mobile computing platforms, and specialized processing units. The solutions emphasize scalability, energy efficiency, and the ability to handle diverse workloads while maintaining the core principles of RISC architecture.

02 RISC-based microprocessor implementation and optimization

Implementation techniques for RISC-based microprocessors involve hardware optimization strategies to maximize throughput and minimize latency. These solutions include pipeline optimization, branch prediction mechanisms, and cache management systems. The focus is on achieving high performance through efficient hardware utilization and parallel processing capabilities while maintaining low power consumption.Expand Specific Solutions03 RISC processor security and protection mechanisms

Security solutions for RISC processors incorporate various protection mechanisms to safeguard against unauthorized access and malicious attacks. These include memory protection units, secure boot processes, and hardware-based encryption capabilities. The implementations focus on maintaining system integrity while ensuring that security features do not significantly impact processor performance.Expand Specific Solutions04 RISC system integration and communication interfaces

Integration solutions for RISC-based systems address the challenges of connecting processors with peripheral devices and external systems. These solutions encompass bus architectures, communication protocols, and interface standards that enable efficient data transfer and system interoperability. The focus is on creating scalable and flexible system architectures that can accommodate various application requirements.Expand Specific Solutions05 Advanced RISC computing applications and specialized implementations

Specialized RISC implementations target specific application domains such as embedded systems, mobile computing, and high-performance computing. These solutions adapt the core RISC principles to meet particular performance, power, and functionality requirements. Innovations include domain-specific instruction extensions, custom accelerators, and optimized compiler technologies that enhance overall system efficiency for targeted use cases.Expand Specific Solutions

Major RISC Vendors and Market Players

The RISC solutions market for high-tech industry implementation is experiencing rapid growth, driven by increasing demand for energy-efficient, customizable processors across IoT, automotive, and edge computing applications. The industry is in an expansion phase with significant market momentum, as traditional x86 dominance faces challenges from open-source RISC-V architecture adoption. Technology maturity varies considerably among key players: established semiconductor giants like Intel, Samsung Electronics, and Taiwan Semiconductor Manufacturing demonstrate advanced implementation capabilities, while specialized firms such as Loongson Technology and Zaram Technology focus on niche RISC applications. Companies like Huawei Technologies and Infineon Technologies are integrating RISC solutions into broader system architectures, indicating mainstream adoption. The competitive landscape shows a mix of mature foundries, emerging RISC-V specialists, and traditional players adapting their portfolios, suggesting the technology is transitioning from early adoption to broader commercial deployment across diverse high-tech sectors.

Intel Corp.

Technical Solution: Intel has developed comprehensive RISC-V solutions including the Intel Horse Creek platform, which integrates RISC-V cores with x86 architecture for hybrid computing environments. Their approach focuses on leveraging RISC-V for specialized workloads while maintaining x86 compatibility for legacy applications. Intel's RISC-V implementation emphasizes security features, hardware-based encryption, and advanced memory management capabilities. The company has also invested in RISC-V ecosystem development through partnerships and open-source contributions, particularly in compiler toolchains and development frameworks for high-tech industry applications.

Strengths: Strong ecosystem support, proven enterprise-grade reliability, extensive development tools and resources. Weaknesses: Higher cost compared to pure RISC-V solutions, potential vendor lock-in concerns.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has implemented RISC-V architecture in their semiconductor solutions, particularly focusing on IoT and embedded applications within high-tech manufacturing environments. Their RISC-V cores are integrated into system-on-chip designs for smart factory automation, industrial sensors, and edge computing devices. Samsung's approach emphasizes low-power consumption and real-time processing capabilities, with custom instruction set extensions optimized for specific industrial applications. The company has developed proprietary RISC-V-based microcontrollers that support advanced connectivity protocols and security features required in modern high-tech industry implementations.

Strengths: Advanced semiconductor manufacturing capabilities, strong integration with memory solutions, proven track record in consumer and industrial electronics. Weaknesses: Limited open-source contributions, primarily focused on internal product development.

Key RISC Patents and Technical Innovations

RISC-v implemented processor with hardware acceleration supporting user defined instruction set and method thereof

PatentActiveUS20210365266A1

Innovation

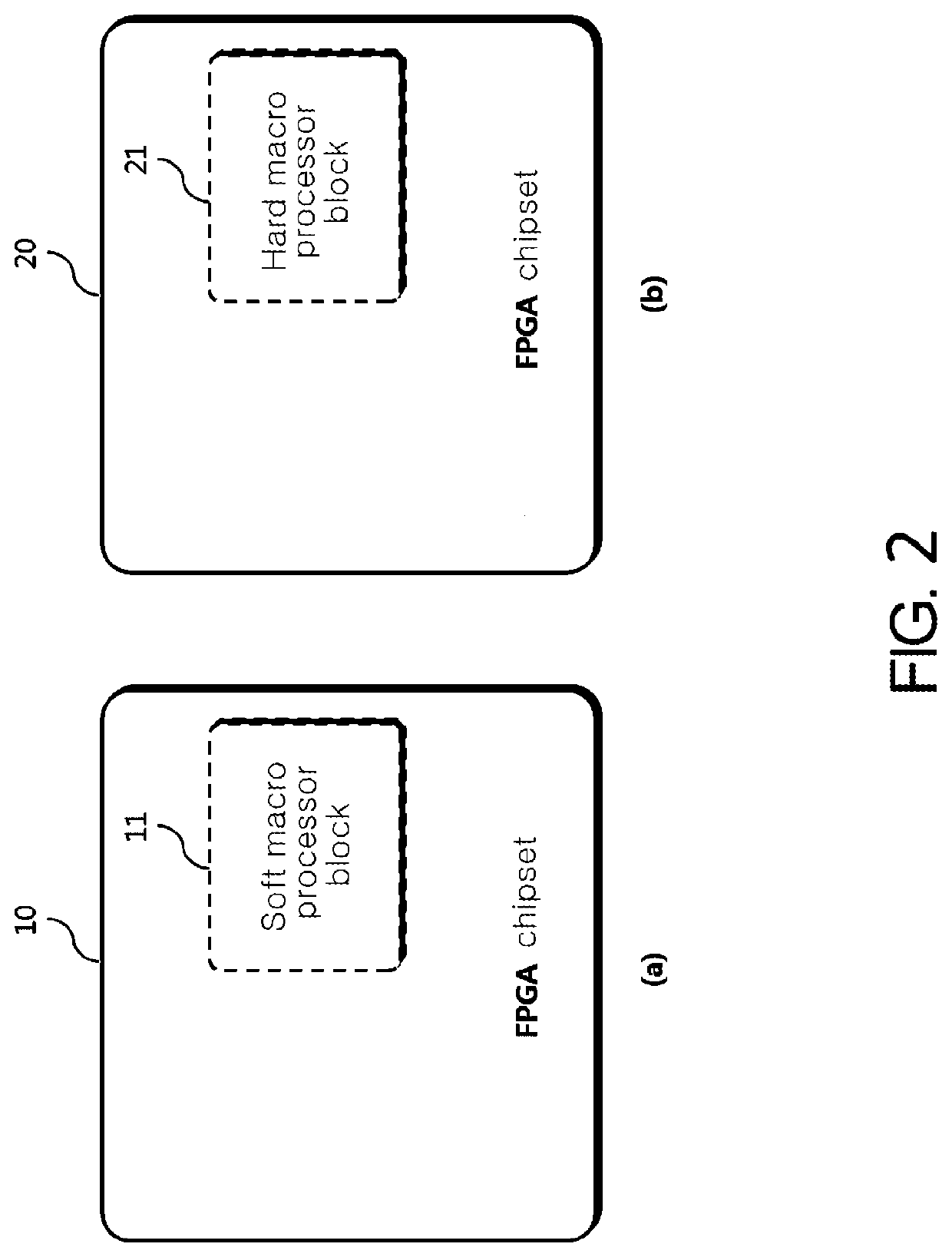

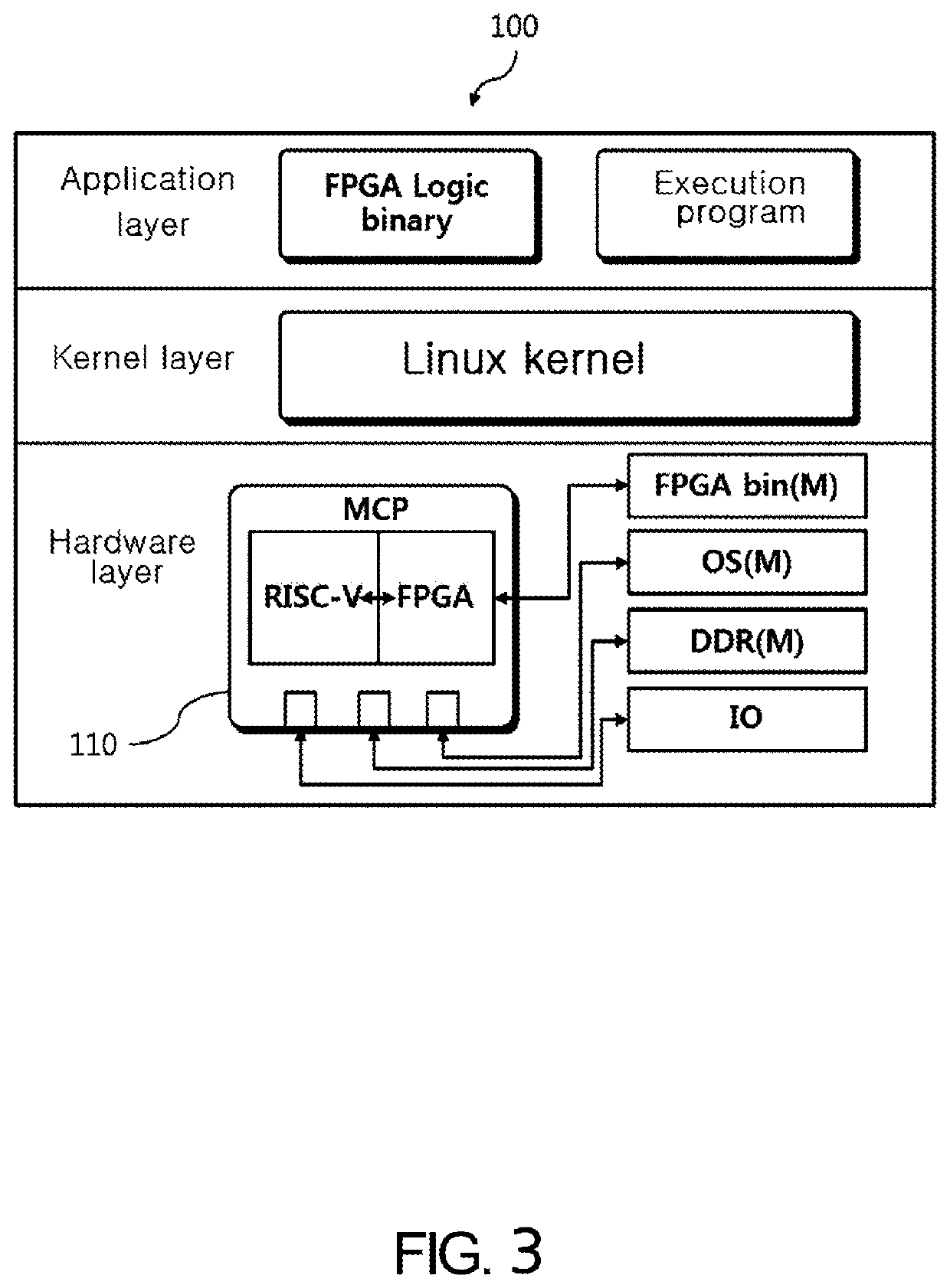

- A hardware high-speed computation device combining RISC-V processors with FPGAs, allowing for user-defined instruction sets to be executed within a single chip, enabling flexible configuration and modification of user-defined instructions without changing the basic ISA, thereby supporting special-purpose computations and external IC control through an interlocking configuration.

Supporting large-word operations in a reduced instruction set computer ("risc") processor

PatentActiveGB2626110A

Innovation

- Introduction of Special Purpose Execution Unit (SPU) with registers having word widths greater than CPU registers, enabling RISC processors to handle large-word operations efficiently.

- Implementation of state-master bits synchronization mechanism between SPU and CPU states, ensuring coherent data flow and state management in large-word operations.

- Flexible result storage architecture allowing operations results to be stored in either CPU registers or alternative SPU registers based on operational needs.

RISC Performance Benchmarking Methodologies

Establishing comprehensive performance benchmarking methodologies for RISC solutions requires a multi-dimensional approach that addresses the unique characteristics of high-tech industry applications. Traditional benchmarking frameworks often fall short when evaluating RISC architectures due to their simplified instruction sets and specialized optimization strategies. A robust methodology must incorporate both synthetic and real-world workload assessments to provide meaningful performance insights.

The foundation of effective RISC benchmarking lies in workload characterization that reflects actual high-tech industry scenarios. This includes compute-intensive tasks such as machine learning inference, signal processing, cryptographic operations, and real-time data analytics. Standard benchmark suites like SPEC CPU, CoreMark, and Dhrystone provide baseline measurements, but industry-specific benchmarks focusing on parallel processing capabilities, memory bandwidth utilization, and power efficiency metrics offer more relevant insights for deployment decisions.

Performance evaluation frameworks must consider multiple metrics beyond raw computational throughput. Key performance indicators include instructions per cycle (IPC), memory latency sensitivity, cache efficiency, and thermal characteristics under sustained workloads. Energy efficiency measurements, expressed as performance per watt, become particularly critical for edge computing and mobile applications where power constraints significantly impact system design choices.

Standardized testing environments ensure reproducible and comparable results across different RISC implementations. This involves controlling variables such as compiler optimization levels, memory configurations, operating system overhead, and thermal conditions. Cross-platform compatibility testing validates performance consistency across different deployment scenarios, from embedded systems to high-performance computing clusters.

Advanced benchmarking methodologies incorporate statistical analysis techniques to account for performance variability and measurement uncertainty. Monte Carlo simulations and confidence interval calculations provide robust performance characterizations that support informed decision-making. Additionally, scalability testing evaluates how RISC solutions perform under varying core counts and memory configurations, essential for understanding deployment flexibility in diverse high-tech applications.

The foundation of effective RISC benchmarking lies in workload characterization that reflects actual high-tech industry scenarios. This includes compute-intensive tasks such as machine learning inference, signal processing, cryptographic operations, and real-time data analytics. Standard benchmark suites like SPEC CPU, CoreMark, and Dhrystone provide baseline measurements, but industry-specific benchmarks focusing on parallel processing capabilities, memory bandwidth utilization, and power efficiency metrics offer more relevant insights for deployment decisions.

Performance evaluation frameworks must consider multiple metrics beyond raw computational throughput. Key performance indicators include instructions per cycle (IPC), memory latency sensitivity, cache efficiency, and thermal characteristics under sustained workloads. Energy efficiency measurements, expressed as performance per watt, become particularly critical for edge computing and mobile applications where power constraints significantly impact system design choices.

Standardized testing environments ensure reproducible and comparable results across different RISC implementations. This involves controlling variables such as compiler optimization levels, memory configurations, operating system overhead, and thermal conditions. Cross-platform compatibility testing validates performance consistency across different deployment scenarios, from embedded systems to high-performance computing clusters.

Advanced benchmarking methodologies incorporate statistical analysis techniques to account for performance variability and measurement uncertainty. Monte Carlo simulations and confidence interval calculations provide robust performance characterizations that support informed decision-making. Additionally, scalability testing evaluates how RISC solutions perform under varying core counts and memory configurations, essential for understanding deployment flexibility in diverse high-tech applications.

Industry Standards for RISC Solution Evaluation

The evaluation of RISC solutions for high-tech industry implementation requires adherence to established industry standards that ensure compatibility, performance, and long-term viability. These standards serve as critical benchmarks for organizations seeking to make informed decisions about RISC architecture adoption across various application domains.

IEEE standards play a fundamental role in RISC solution evaluation, particularly IEEE 1754 for 32-bit microprocessor architecture and IEEE 1596 for scalable coherent interface specifications. These standards establish baseline requirements for instruction set architecture consistency, memory management protocols, and inter-processor communication mechanisms. Compliance with these standards ensures that RISC implementations can integrate seamlessly with existing enterprise infrastructure while maintaining predictable performance characteristics.

The Open Group's architectural frameworks provide comprehensive guidelines for evaluating RISC solutions within enterprise contexts. Their TOGAF methodology emphasizes the importance of aligning RISC implementations with business objectives, technical requirements, and operational constraints. This framework mandates thorough assessment of power consumption metrics, thermal management capabilities, and scalability potential before deployment decisions.

ISO/IEC 25010 quality model standards establish specific criteria for evaluating RISC solution reliability, maintainability, and portability. These standards require quantitative assessment of mean time between failures, error recovery mechanisms, and cross-platform compatibility. High-tech industries particularly benefit from these standardized evaluation metrics when comparing different RISC vendors and architectures.

Industry-specific standards such as JEDEC for semiconductor specifications and ANSI/TIA standards for telecommunications applications provide domain-specific evaluation criteria. These standards address specialized requirements including real-time processing capabilities, security implementations, and environmental operating conditions that are critical for high-tech industry deployments.

Benchmark standards like SPEC CPU and CoreMark offer standardized performance evaluation methodologies that enable objective comparison between RISC solutions. These benchmarks provide quantitative metrics for computational throughput, energy efficiency, and workload-specific performance characteristics, facilitating data-driven decision-making processes for technology adoption.

IEEE standards play a fundamental role in RISC solution evaluation, particularly IEEE 1754 for 32-bit microprocessor architecture and IEEE 1596 for scalable coherent interface specifications. These standards establish baseline requirements for instruction set architecture consistency, memory management protocols, and inter-processor communication mechanisms. Compliance with these standards ensures that RISC implementations can integrate seamlessly with existing enterprise infrastructure while maintaining predictable performance characteristics.

The Open Group's architectural frameworks provide comprehensive guidelines for evaluating RISC solutions within enterprise contexts. Their TOGAF methodology emphasizes the importance of aligning RISC implementations with business objectives, technical requirements, and operational constraints. This framework mandates thorough assessment of power consumption metrics, thermal management capabilities, and scalability potential before deployment decisions.

ISO/IEC 25010 quality model standards establish specific criteria for evaluating RISC solution reliability, maintainability, and portability. These standards require quantitative assessment of mean time between failures, error recovery mechanisms, and cross-platform compatibility. High-tech industries particularly benefit from these standardized evaluation metrics when comparing different RISC vendors and architectures.

Industry-specific standards such as JEDEC for semiconductor specifications and ANSI/TIA standards for telecommunications applications provide domain-specific evaluation criteria. These standards address specialized requirements including real-time processing capabilities, security implementations, and environmental operating conditions that are critical for high-tech industry deployments.

Benchmark standards like SPEC CPU and CoreMark offer standardized performance evaluation methodologies that enable objective comparison between RISC solutions. These benchmarks provide quantitative metrics for computational throughput, energy efficiency, and workload-specific performance characteristics, facilitating data-driven decision-making processes for technology adoption.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!