Determine RISC's Suitability for Complex Data Analytics

MAR 26, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RISC Architecture Analytics Background and Objectives

RISC (Reduced Instruction Set Computer) architecture emerged in the 1980s as a revolutionary approach to processor design, fundamentally challenging the prevailing Complex Instruction Set Computer (CISC) paradigm. The architecture was conceived on the principle that simpler, more uniform instructions could execute faster and more efficiently than complex, variable-length instructions. This design philosophy emphasized streamlined instruction sets, uniform instruction formats, and optimized pipeline execution.

The evolution of RISC architecture has been marked by continuous refinement and adaptation to emerging computational demands. Early implementations focused primarily on general-purpose computing tasks, demonstrating significant performance improvements in traditional workloads. However, the landscape of computational requirements has dramatically shifted toward data-intensive applications, machine learning algorithms, and complex analytics workloads that demand specialized processing capabilities.

Contemporary data analytics presents unique computational challenges that differ substantially from traditional computing paradigms. These workloads typically involve massive datasets, parallel processing requirements, memory-intensive operations, and specialized mathematical computations. The characteristics of modern analytics include irregular memory access patterns, high bandwidth requirements, and the need for efficient handling of both structured and unstructured data formats.

The primary objective of this technical investigation is to comprehensively evaluate RISC architecture's capability to address the computational demands of complex data analytics applications. This assessment encompasses examining the architectural strengths and limitations when processing large-scale datasets, analyzing performance characteristics under analytics-specific workloads, and identifying potential optimization opportunities within the RISC framework.

Furthermore, this research aims to establish benchmarks for RISC performance in analytics contexts, comparing efficiency metrics against specialized analytics processors and traditional CISC implementations. The investigation seeks to determine whether RISC's inherent design principles of simplicity and efficiency translate effectively to the complex, data-heavy computational patterns characteristic of modern analytics applications.

The ultimate goal is to provide definitive guidance on RISC architecture's viability as a foundation for next-generation analytics computing platforms, identifying specific use cases where RISC excels and areas requiring architectural enhancements or complementary technologies.

The evolution of RISC architecture has been marked by continuous refinement and adaptation to emerging computational demands. Early implementations focused primarily on general-purpose computing tasks, demonstrating significant performance improvements in traditional workloads. However, the landscape of computational requirements has dramatically shifted toward data-intensive applications, machine learning algorithms, and complex analytics workloads that demand specialized processing capabilities.

Contemporary data analytics presents unique computational challenges that differ substantially from traditional computing paradigms. These workloads typically involve massive datasets, parallel processing requirements, memory-intensive operations, and specialized mathematical computations. The characteristics of modern analytics include irregular memory access patterns, high bandwidth requirements, and the need for efficient handling of both structured and unstructured data formats.

The primary objective of this technical investigation is to comprehensively evaluate RISC architecture's capability to address the computational demands of complex data analytics applications. This assessment encompasses examining the architectural strengths and limitations when processing large-scale datasets, analyzing performance characteristics under analytics-specific workloads, and identifying potential optimization opportunities within the RISC framework.

Furthermore, this research aims to establish benchmarks for RISC performance in analytics contexts, comparing efficiency metrics against specialized analytics processors and traditional CISC implementations. The investigation seeks to determine whether RISC's inherent design principles of simplicity and efficiency translate effectively to the complex, data-heavy computational patterns characteristic of modern analytics applications.

The ultimate goal is to provide definitive guidance on RISC architecture's viability as a foundation for next-generation analytics computing platforms, identifying specific use cases where RISC excels and areas requiring architectural enhancements or complementary technologies.

Market Demand for RISC-based Analytics Solutions

The market demand for RISC-based analytics solutions is experiencing significant growth driven by the increasing need for energy-efficient computing architectures in data-intensive applications. Organizations across various sectors are seeking alternatives to traditional x86 processors to address rising computational costs and power consumption challenges in their analytics workloads.

Enterprise data centers represent a primary market segment, where companies are evaluating RISC architectures to reduce operational expenses while maintaining analytical performance. The growing emphasis on sustainable computing practices has intensified interest in power-efficient processors that can handle complex data processing tasks without compromising throughput or accuracy.

Cloud service providers constitute another crucial market segment, as they face mounting pressure to optimize infrastructure costs while scaling analytics capabilities. The demand stems from their need to support diverse customer workloads ranging from real-time stream processing to large-scale machine learning model training, where RISC processors could offer compelling price-performance advantages.

The financial services industry shows particular interest in RISC-based solutions for risk analytics, algorithmic trading, and fraud detection systems. These applications require consistent low-latency performance and high computational efficiency, making RISC architectures attractive for their predictable execution patterns and reduced power requirements.

Telecommunications companies are exploring RISC processors for network analytics and edge computing scenarios, where space and power constraints make traditional server architectures impractical. The shift toward 5G networks and IoT deployments has created demand for distributed analytics capabilities that can operate efficiently in resource-constrained environments.

Research institutions and academic organizations represent an emerging market segment, particularly those conducting large-scale scientific computing and data analysis projects. Budget constraints and sustainability goals drive their interest in cost-effective, energy-efficient computing solutions that can support complex analytical workloads.

The automotive industry's transition toward autonomous vehicles and connected car technologies has generated demand for RISC-based analytics solutions capable of processing sensor data and performing real-time decision-making tasks. These applications require specialized computing architectures optimized for specific analytical workflows rather than general-purpose processing.

Market adoption faces challenges including software ecosystem maturity, developer familiarity, and integration complexity with existing analytics infrastructure. However, growing vendor support and improving software toolchains are gradually addressing these barriers, expanding the addressable market for RISC-based analytics solutions.

Enterprise data centers represent a primary market segment, where companies are evaluating RISC architectures to reduce operational expenses while maintaining analytical performance. The growing emphasis on sustainable computing practices has intensified interest in power-efficient processors that can handle complex data processing tasks without compromising throughput or accuracy.

Cloud service providers constitute another crucial market segment, as they face mounting pressure to optimize infrastructure costs while scaling analytics capabilities. The demand stems from their need to support diverse customer workloads ranging from real-time stream processing to large-scale machine learning model training, where RISC processors could offer compelling price-performance advantages.

The financial services industry shows particular interest in RISC-based solutions for risk analytics, algorithmic trading, and fraud detection systems. These applications require consistent low-latency performance and high computational efficiency, making RISC architectures attractive for their predictable execution patterns and reduced power requirements.

Telecommunications companies are exploring RISC processors for network analytics and edge computing scenarios, where space and power constraints make traditional server architectures impractical. The shift toward 5G networks and IoT deployments has created demand for distributed analytics capabilities that can operate efficiently in resource-constrained environments.

Research institutions and academic organizations represent an emerging market segment, particularly those conducting large-scale scientific computing and data analysis projects. Budget constraints and sustainability goals drive their interest in cost-effective, energy-efficient computing solutions that can support complex analytical workloads.

The automotive industry's transition toward autonomous vehicles and connected car technologies has generated demand for RISC-based analytics solutions capable of processing sensor data and performing real-time decision-making tasks. These applications require specialized computing architectures optimized for specific analytical workflows rather than general-purpose processing.

Market adoption faces challenges including software ecosystem maturity, developer familiarity, and integration complexity with existing analytics infrastructure. However, growing vendor support and improving software toolchains are gradually addressing these barriers, expanding the addressable market for RISC-based analytics solutions.

Current RISC Limitations in Complex Data Processing

RISC architectures face significant computational bottlenecks when handling complex data analytics workloads. The simplified instruction set, while beneficial for general-purpose computing, creates performance gaps in data-intensive operations. Traditional RISC processors struggle with the massive parallel computations required for machine learning algorithms, statistical modeling, and large-scale data transformations. The instruction pipeline optimization that makes RISC efficient for sequential tasks becomes a limitation when processing requires extensive vectorization and parallel execution paths.

Memory bandwidth constraints represent another critical limitation in RISC-based data processing systems. Complex analytics workloads demand high-throughput memory access patterns, often requiring simultaneous reads and writes across multiple data streams. RISC architectures typically feature simpler memory hierarchies compared to specialized processors, resulting in bottlenecks when handling large datasets that exceed cache capacities. This limitation becomes particularly pronounced in real-time analytics scenarios where data must be processed continuously without buffering delays.

The lack of specialized instruction sets for mathematical operations poses substantial challenges for data analytics applications. Unlike x86 processors with extensive SIMD capabilities or dedicated AI accelerators with tensor processing units, RISC processors rely on basic arithmetic instructions for complex mathematical computations. Operations such as matrix multiplications, floating-point intensive calculations, and cryptographic functions require multiple instruction cycles, significantly impacting overall processing throughput for analytics workloads.

Scalability limitations emerge when RISC systems attempt to handle enterprise-level data processing requirements. The architectural simplicity that enables power efficiency and cost-effectiveness becomes counterproductive when scaling to handle petabyte-scale datasets or supporting hundreds of concurrent analytical queries. Multi-core RISC implementations often struggle with inter-core communication overhead and cache coherency issues that become magnified in data-intensive environments.

Integration challenges with existing data analytics ecosystems further compound RISC limitations. Many established analytics frameworks and libraries are optimized for x86 architectures, requiring significant adaptation or recompilation for RISC platforms. This compatibility gap creates additional development overhead and potential performance degradation when porting existing analytics solutions to RISC-based infrastructure, limiting adoption in enterprise environments where legacy system integration is crucial.

Memory bandwidth constraints represent another critical limitation in RISC-based data processing systems. Complex analytics workloads demand high-throughput memory access patterns, often requiring simultaneous reads and writes across multiple data streams. RISC architectures typically feature simpler memory hierarchies compared to specialized processors, resulting in bottlenecks when handling large datasets that exceed cache capacities. This limitation becomes particularly pronounced in real-time analytics scenarios where data must be processed continuously without buffering delays.

The lack of specialized instruction sets for mathematical operations poses substantial challenges for data analytics applications. Unlike x86 processors with extensive SIMD capabilities or dedicated AI accelerators with tensor processing units, RISC processors rely on basic arithmetic instructions for complex mathematical computations. Operations such as matrix multiplications, floating-point intensive calculations, and cryptographic functions require multiple instruction cycles, significantly impacting overall processing throughput for analytics workloads.

Scalability limitations emerge when RISC systems attempt to handle enterprise-level data processing requirements. The architectural simplicity that enables power efficiency and cost-effectiveness becomes counterproductive when scaling to handle petabyte-scale datasets or supporting hundreds of concurrent analytical queries. Multi-core RISC implementations often struggle with inter-core communication overhead and cache coherency issues that become magnified in data-intensive environments.

Integration challenges with existing data analytics ecosystems further compound RISC limitations. Many established analytics frameworks and libraries are optimized for x86 architectures, requiring significant adaptation or recompilation for RISC platforms. This compatibility gap creates additional development overhead and potential performance degradation when porting existing analytics solutions to RISC-based infrastructure, limiting adoption in enterprise environments where legacy system integration is crucial.

Existing RISC Solutions for Data Analytics Applications

01 RISC processor architecture design and instruction set optimization

RISC (Reduced Instruction Set Computer) architecture focuses on simplifying instruction sets to improve processing efficiency. This approach involves designing processors with a limited number of simple instructions that can be executed in a single clock cycle, enabling faster execution and reduced complexity. The architecture emphasizes load-store operations, register-based computations, and pipelining techniques to enhance performance. Optimization strategies include instruction scheduling, register allocation, and minimizing memory access latency.- RISC processor architecture design and instruction set optimization: RISC (Reduced Instruction Set Computer) architecture focuses on simplified instruction sets to improve processing efficiency. The design emphasizes a small set of simple instructions that can be executed in a single clock cycle, enabling faster processing speeds and reduced complexity. This approach allows for optimized pipeline execution and improved performance in embedded systems and general-purpose computing applications.

- RISC processor implementation in embedded systems and microcontrollers: RISC architectures are particularly suitable for embedded systems and microcontroller applications due to their power efficiency and simplified design. The reduced instruction set allows for smaller chip sizes, lower power consumption, and cost-effective manufacturing. These processors are widely used in consumer electronics, automotive systems, and IoT devices where resource constraints and energy efficiency are critical factors.

- RISC-based data processing and computational methods: RISC processors enable efficient data processing through streamlined computational methods and optimized instruction execution. The architecture supports parallel processing capabilities and efficient memory access patterns, making it suitable for applications requiring high-throughput data processing. Advanced techniques include pipelining, superscalar execution, and branch prediction to maximize computational efficiency.

- RISC processor integration with specialized hardware accelerators: Modern RISC implementations often incorporate specialized hardware accelerators and coprocessors to enhance performance for specific tasks. This integration allows the main RISC core to handle general-purpose computing while delegating specialized operations to dedicated hardware units. Such hybrid architectures are particularly effective in applications requiring both flexibility and high performance in specific computational domains.

- RISC processor security features and system reliability: Security and reliability considerations in RISC processor design include hardware-based protection mechanisms, secure boot processes, and fault-tolerant architectures. These features ensure system integrity and protect against various security threats while maintaining the performance advantages of RISC architecture. Implementation includes memory protection units, secure execution environments, and error detection and correction mechanisms.

02 RISC-based microprocessor implementation and hardware configuration

Implementation of RISC principles in microprocessor design involves specific hardware configurations that support efficient instruction execution. This includes the development of specialized execution units, optimized data paths, and cache memory systems. The hardware architecture is designed to support parallel processing capabilities and efficient instruction decoding mechanisms. Various configurations enable different performance characteristics suitable for specific applications.Expand Specific Solutions03 RISC processor application in embedded systems and mobile devices

RISC processors are particularly suitable for embedded systems and mobile computing applications due to their power efficiency and compact design. The architecture's simplicity allows for reduced power consumption while maintaining adequate processing capabilities. Applications include smartphones, tablets, IoT devices, and other portable electronics where battery life and thermal management are critical considerations. The scalability of RISC designs enables customization for various performance and power requirements.Expand Specific Solutions04 RISC processor performance enhancement through compiler optimization

Compiler technology plays a crucial role in maximizing RISC processor performance by generating optimized code that takes advantage of the architecture's characteristics. Advanced compilation techniques include instruction scheduling to minimize pipeline stalls, efficient register allocation to reduce memory access, and loop optimization strategies. The compiler must understand the specific constraints and capabilities of the RISC architecture to produce highly efficient executable code that fully utilizes available hardware resources.Expand Specific Solutions05 RISC architecture evolution and modern implementations

Modern RISC architectures have evolved to incorporate advanced features while maintaining core design principles. Recent developments include multi-core configurations, enhanced vector processing capabilities, and improved memory management systems. Contemporary implementations balance the traditional RISC philosophy with practical requirements for complex computing tasks. Innovations address challenges in areas such as security, virtualization support, and integration with heterogeneous computing environments.Expand Specific Solutions

Key Players in RISC Analytics Processor Market

The RISC architecture's suitability for complex data analytics represents a rapidly evolving competitive landscape characterized by early-to-mature stage development with significant growth potential. The market demonstrates substantial scale driven by increasing demand for efficient processing in AI and big data applications. Technology maturity varies significantly across players, with established giants like IBM, Qualcomm, and Texas Instruments leading in proven RISC implementations, while emerging companies such as Loongson Technology and various Chinese semiconductor firms are advancing specialized solutions. Academic institutions including Wuhan University and Beijing University of Posts & Telecommunications contribute foundational research, creating a diverse ecosystem spanning from hardware manufacturers like Taiwan Semiconductor Manufacturing to software specialists like Inspur. This multi-tiered competition indicates strong market validation for RISC's analytics capabilities.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive RISC-V solutions for complex data analytics through their Power architecture evolution and RISC-V research initiatives. Their approach focuses on optimizing RISC-V cores for high-performance computing workloads by implementing advanced vector processing units, custom instruction extensions for mathematical operations, and sophisticated memory hierarchy designs. IBM's RISC-V implementation includes specialized accelerators for machine learning inference, parallel processing capabilities for big data workloads, and optimized compiler toolchains that can efficiently translate complex analytics algorithms into RISC-V assembly code. Their solution demonstrates significant performance improvements in matrix operations, statistical computations, and data transformation tasks commonly found in analytics pipelines.

Strengths: Extensive experience in enterprise-grade processor design, strong compiler optimization capabilities, proven track record in high-performance computing. Weaknesses: Higher development costs, complex implementation requiring specialized expertise.

Loongson Technology Corp. Ltd.

Technical Solution: Loongson has developed RISC-V based processors specifically designed for data center and high-performance computing applications including complex data analytics. Their solution features multi-core RISC-V architectures with advanced vector processing capabilities, optimized cache hierarchies, and high-bandwidth memory interfaces suitable for large-scale data processing workloads. The company's RISC-V implementation includes specialized instruction extensions for mathematical computations, parallel processing support for distributed analytics tasks, and optimized interconnect technologies for multi-processor systems. Loongson's approach emphasizes creating cost-effective alternatives to traditional x86 processors while maintaining compatibility with standard analytics software frameworks and providing competitive performance for computational intensive tasks.

Strengths: Focus on high-performance computing applications, cost-effective processor solutions, strong government and enterprise support in China. Weaknesses: Limited global market presence, ecosystem maturity compared to established architectures, potential compatibility challenges with international software standards.

Core RISC Innovations for Analytics Performance

Data processing method and processor

PatentInactiveCN101122851A

Innovation

- By detecting the write port status of the register file, if there is no idle port, the data in the pipeline is cached, and the address mapping of the data is implemented through the buffer queue to reduce the number of write ports and prioritize using idle ports for writing.

Energy efficient processing device

PatentInactiveUS20090228686A1

Innovation

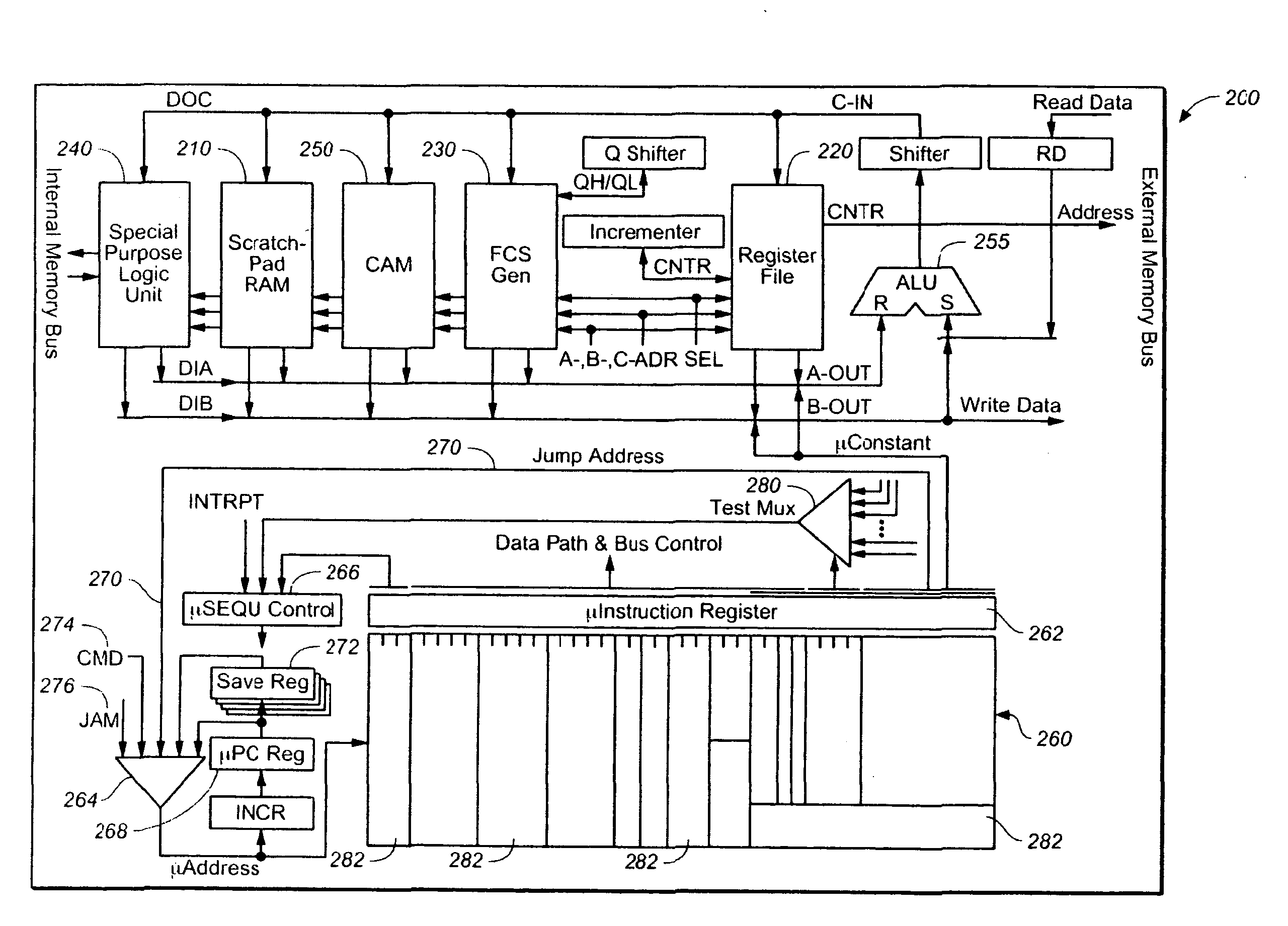

- A network processor with a microcoded architecture employing non-opcode-oriented, fully decoded microcode instructions that do not require an instruction decoder, utilizing a programmable microsequencer for state management and control, and a data manipulation subsystem controlled by fully decoded microinstructions, resulting in reduced power consumption and compact size.

Energy Efficiency Standards for Analytics Processors

Energy efficiency has emerged as a critical design criterion for analytics processors, particularly as data centers face mounting pressure to reduce power consumption while maintaining computational performance. The exponential growth in data processing demands has necessitated the establishment of comprehensive energy efficiency standards that can guide processor design and deployment decisions for complex analytics workloads.

Current industry standards for analytics processor energy efficiency are primarily measured through metrics such as Performance per Watt (GOPS/W), Total Cost of Ownership (TCO), and Power Usage Effectiveness (PUE). Leading organizations including IEEE, SPEC, and Green500 have developed benchmarking frameworks specifically tailored for evaluating energy consumption in high-performance computing environments. These standards typically assess processors under various workload conditions, including machine learning inference, database queries, and real-time stream processing scenarios.

RISC-V processors demonstrate significant advantages in meeting emerging energy efficiency standards due to their streamlined instruction set architecture and modular design philosophy. The reduced instruction complexity inherently leads to lower power consumption per operation, while the open-source nature enables custom optimizations for specific analytics workloads. Recent implementations of RISC-V cores have achieved energy efficiency ratings of 50-100 GOPS/W for integer operations and 20-40 GFLOPS/W for floating-point computations, positioning them competitively against traditional x86 and ARM architectures.

The modular extension capability of RISC-V allows for targeted energy optimizations through custom instruction sets designed for analytics operations. Vector extensions and specialized accelerator units can be integrated seamlessly, enabling processors to achieve higher computational density while maintaining strict power budgets. This architectural flexibility proves particularly valuable in meeting diverse energy efficiency requirements across different analytics applications.

Regulatory frameworks are increasingly incorporating mandatory energy efficiency thresholds for data center processors. The European Union's Energy Efficiency Directive and similar initiatives in Asia-Pacific regions are driving adoption of standardized measurement protocols. These regulations typically require processors to demonstrate minimum efficiency levels of 10 GOPS/W for general-purpose analytics tasks, with higher thresholds expected for specialized workloads such as neural network inference and scientific computing applications.

Current industry standards for analytics processor energy efficiency are primarily measured through metrics such as Performance per Watt (GOPS/W), Total Cost of Ownership (TCO), and Power Usage Effectiveness (PUE). Leading organizations including IEEE, SPEC, and Green500 have developed benchmarking frameworks specifically tailored for evaluating energy consumption in high-performance computing environments. These standards typically assess processors under various workload conditions, including machine learning inference, database queries, and real-time stream processing scenarios.

RISC-V processors demonstrate significant advantages in meeting emerging energy efficiency standards due to their streamlined instruction set architecture and modular design philosophy. The reduced instruction complexity inherently leads to lower power consumption per operation, while the open-source nature enables custom optimizations for specific analytics workloads. Recent implementations of RISC-V cores have achieved energy efficiency ratings of 50-100 GOPS/W for integer operations and 20-40 GFLOPS/W for floating-point computations, positioning them competitively against traditional x86 and ARM architectures.

The modular extension capability of RISC-V allows for targeted energy optimizations through custom instruction sets designed for analytics operations. Vector extensions and specialized accelerator units can be integrated seamlessly, enabling processors to achieve higher computational density while maintaining strict power budgets. This architectural flexibility proves particularly valuable in meeting diverse energy efficiency requirements across different analytics applications.

Regulatory frameworks are increasingly incorporating mandatory energy efficiency thresholds for data center processors. The European Union's Energy Efficiency Directive and similar initiatives in Asia-Pacific regions are driving adoption of standardized measurement protocols. These regulations typically require processors to demonstrate minimum efficiency levels of 10 GOPS/W for general-purpose analytics tasks, with higher thresholds expected for specialized workloads such as neural network inference and scientific computing applications.

RISC vs CISC Performance Benchmarking Framework

Establishing a comprehensive performance benchmarking framework for RISC versus CISC architectures in complex data analytics requires systematic evaluation methodologies that capture the nuanced performance characteristics of both architectural paradigms. The framework must encompass multiple dimensions of performance measurement, including computational throughput, memory bandwidth utilization, energy efficiency, and scalability metrics specific to data-intensive workloads.

The benchmarking methodology should incorporate standardized data analytics workloads that represent real-world scenarios, including machine learning training algorithms, statistical computations, graph processing, and large-scale data transformations. These workloads must be carefully selected to stress different aspects of processor architecture, from instruction-level parallelism to memory hierarchy efficiency, ensuring comprehensive coverage of performance-critical scenarios in data analytics applications.

Performance metrics collection should focus on both macro-level indicators such as execution time and throughput, as well as micro-architectural metrics including cache hit rates, branch prediction accuracy, instruction retirement rates, and memory access patterns. The framework must also capture power consumption profiles and thermal characteristics, as these factors significantly impact the total cost of ownership in data center deployments where analytics workloads typically execute.

Standardization of testing environments becomes crucial for meaningful comparisons between RISC and CISC implementations. The framework should specify consistent compiler optimization levels, memory configurations, and system software stacks to eliminate variables that could skew results. Additionally, the methodology must account for different implementation scales, from single-core performance to multi-socket system configurations that reflect typical analytics deployment scenarios.

The benchmarking framework should incorporate statistical rigor through multiple test iterations, confidence interval calculations, and variance analysis to ensure result reliability. Furthermore, the framework must be adaptable to emerging workload patterns and new processor implementations, maintaining relevance as both RISC and CISC architectures continue evolving to address the growing demands of complex data analytics applications.

The benchmarking methodology should incorporate standardized data analytics workloads that represent real-world scenarios, including machine learning training algorithms, statistical computations, graph processing, and large-scale data transformations. These workloads must be carefully selected to stress different aspects of processor architecture, from instruction-level parallelism to memory hierarchy efficiency, ensuring comprehensive coverage of performance-critical scenarios in data analytics applications.

Performance metrics collection should focus on both macro-level indicators such as execution time and throughput, as well as micro-architectural metrics including cache hit rates, branch prediction accuracy, instruction retirement rates, and memory access patterns. The framework must also capture power consumption profiles and thermal characteristics, as these factors significantly impact the total cost of ownership in data center deployments where analytics workloads typically execute.

Standardization of testing environments becomes crucial for meaningful comparisons between RISC and CISC implementations. The framework should specify consistent compiler optimization levels, memory configurations, and system software stacks to eliminate variables that could skew results. Additionally, the methodology must account for different implementation scales, from single-core performance to multi-socket system configurations that reflect typical analytics deployment scenarios.

The benchmarking framework should incorporate statistical rigor through multiple test iterations, confidence interval calculations, and variance analysis to ensure result reliability. Furthermore, the framework must be adaptable to emerging workload patterns and new processor implementations, maintaining relevance as both RISC and CISC architectures continue evolving to address the growing demands of complex data analytics applications.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!