Implement Scalable Systems with Microcontroller Networks

FEB 25, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Microcontroller Network System Background and Objectives

Microcontroller networks have emerged as a fundamental paradigm in modern embedded systems, driven by the increasing demand for distributed intelligence and autonomous operation across diverse applications. The evolution from single-chip solutions to interconnected microcontroller ecosystems represents a significant shift in system architecture philosophy, enabling unprecedented levels of scalability, redundancy, and computational efficiency.

The historical development of microcontroller networks traces back to the early industrial automation systems of the 1980s, where simple point-to-point communication protocols facilitated basic data exchange between control units. The introduction of fieldbus technologies in the 1990s marked a pivotal moment, establishing standardized communication frameworks that enabled multiple microcontrollers to operate cohesively within larger systems. This foundation paved the way for contemporary mesh networks, wireless sensor networks, and Internet of Things implementations.

Current technological trends indicate a convergence toward heterogeneous microcontroller networks that combine various processing capabilities, communication protocols, and power management strategies. The integration of edge computing principles with traditional embedded systems has created new opportunities for distributed processing architectures, where computational loads are dynamically allocated across network nodes based on resource availability and task requirements.

The primary technical objectives of scalable microcontroller network systems encompass several critical dimensions. Performance scalability requires networks to maintain operational efficiency as node counts increase, ensuring that communication overhead does not compromise system responsiveness. Functional scalability demands that new capabilities can be seamlessly integrated without disrupting existing operations, supporting modular system expansion and feature enhancement.

Reliability objectives focus on implementing fault-tolerant mechanisms that enable continued operation despite individual node failures. This includes developing robust routing algorithms, redundant communication pathways, and distributed decision-making protocols that prevent single points of failure from compromising entire network functionality.

Energy efficiency represents another crucial objective, particularly for battery-powered or energy-harvesting applications. Networks must optimize power consumption through intelligent sleep scheduling, adaptive transmission power control, and efficient data aggregation techniques that minimize unnecessary communication overhead.

Interoperability goals emphasize the development of standardized interfaces and protocols that enable seamless integration of microcontrollers from different manufacturers and generations. This objective supports long-term system maintainability and reduces vendor lock-in risks while facilitating technology migration and upgrade pathways.

Security objectives address the growing concerns regarding network vulnerability and data integrity in distributed systems. Implementation of lightweight cryptographic protocols, secure key distribution mechanisms, and intrusion detection capabilities ensures that scalable networks maintain robust protection against malicious attacks and unauthorized access attempts.

The historical development of microcontroller networks traces back to the early industrial automation systems of the 1980s, where simple point-to-point communication protocols facilitated basic data exchange between control units. The introduction of fieldbus technologies in the 1990s marked a pivotal moment, establishing standardized communication frameworks that enabled multiple microcontrollers to operate cohesively within larger systems. This foundation paved the way for contemporary mesh networks, wireless sensor networks, and Internet of Things implementations.

Current technological trends indicate a convergence toward heterogeneous microcontroller networks that combine various processing capabilities, communication protocols, and power management strategies. The integration of edge computing principles with traditional embedded systems has created new opportunities for distributed processing architectures, where computational loads are dynamically allocated across network nodes based on resource availability and task requirements.

The primary technical objectives of scalable microcontroller network systems encompass several critical dimensions. Performance scalability requires networks to maintain operational efficiency as node counts increase, ensuring that communication overhead does not compromise system responsiveness. Functional scalability demands that new capabilities can be seamlessly integrated without disrupting existing operations, supporting modular system expansion and feature enhancement.

Reliability objectives focus on implementing fault-tolerant mechanisms that enable continued operation despite individual node failures. This includes developing robust routing algorithms, redundant communication pathways, and distributed decision-making protocols that prevent single points of failure from compromising entire network functionality.

Energy efficiency represents another crucial objective, particularly for battery-powered or energy-harvesting applications. Networks must optimize power consumption through intelligent sleep scheduling, adaptive transmission power control, and efficient data aggregation techniques that minimize unnecessary communication overhead.

Interoperability goals emphasize the development of standardized interfaces and protocols that enable seamless integration of microcontrollers from different manufacturers and generations. This objective supports long-term system maintainability and reduces vendor lock-in risks while facilitating technology migration and upgrade pathways.

Security objectives address the growing concerns regarding network vulnerability and data integrity in distributed systems. Implementation of lightweight cryptographic protocols, secure key distribution mechanisms, and intrusion detection capabilities ensures that scalable networks maintain robust protection against malicious attacks and unauthorized access attempts.

Market Demand for Scalable Microcontroller Solutions

The global market for scalable microcontroller solutions is experiencing unprecedented growth driven by the proliferation of Internet of Things (IoT) applications across multiple industries. Smart home automation, industrial IoT implementations, and connected vehicle systems are creating substantial demand for distributed computing architectures that can efficiently scale from small sensor networks to enterprise-level deployments.

Industrial automation represents one of the most significant demand drivers, where manufacturers require flexible microcontroller networks capable of monitoring and controlling complex production processes. These systems must accommodate varying scales of operation, from single production lines to entire manufacturing facilities, while maintaining real-time responsiveness and reliability.

The healthcare sector is emerging as a critical market segment, particularly for remote patient monitoring and smart medical device networks. Healthcare providers increasingly demand scalable solutions that can seamlessly integrate multiple monitoring devices while ensuring data security and regulatory compliance. The aging global population and rising healthcare costs are accelerating adoption of distributed monitoring systems.

Smart city initiatives worldwide are generating substantial demand for scalable microcontroller networks in traffic management, environmental monitoring, and public safety applications. Municipal governments require systems that can start with pilot deployments and expand to city-wide implementations without requiring complete infrastructure overhauls.

Consumer electronics markets are driving demand for scalable home automation solutions, where microcontroller networks must accommodate diverse device ecosystems while providing seamless user experiences. The growing adoption of voice assistants and smart appliances is creating opportunities for integrated control systems.

Agricultural technology presents emerging opportunities, with precision farming applications requiring scalable sensor networks for soil monitoring, irrigation control, and crop management. These systems must operate reliably in challenging environmental conditions while providing cost-effective scalability for farms of varying sizes.

The automotive industry's transition toward connected and autonomous vehicles is creating demand for sophisticated microcontroller networks capable of processing distributed sensor data while maintaining safety-critical performance standards. Vehicle manufacturers require solutions that can scale across different vehicle platforms and model years.

Energy management applications, including smart grid implementations and renewable energy systems, represent growing market segments where scalable microcontroller networks enable efficient power distribution and consumption optimization across diverse infrastructure scales.

Industrial automation represents one of the most significant demand drivers, where manufacturers require flexible microcontroller networks capable of monitoring and controlling complex production processes. These systems must accommodate varying scales of operation, from single production lines to entire manufacturing facilities, while maintaining real-time responsiveness and reliability.

The healthcare sector is emerging as a critical market segment, particularly for remote patient monitoring and smart medical device networks. Healthcare providers increasingly demand scalable solutions that can seamlessly integrate multiple monitoring devices while ensuring data security and regulatory compliance. The aging global population and rising healthcare costs are accelerating adoption of distributed monitoring systems.

Smart city initiatives worldwide are generating substantial demand for scalable microcontroller networks in traffic management, environmental monitoring, and public safety applications. Municipal governments require systems that can start with pilot deployments and expand to city-wide implementations without requiring complete infrastructure overhauls.

Consumer electronics markets are driving demand for scalable home automation solutions, where microcontroller networks must accommodate diverse device ecosystems while providing seamless user experiences. The growing adoption of voice assistants and smart appliances is creating opportunities for integrated control systems.

Agricultural technology presents emerging opportunities, with precision farming applications requiring scalable sensor networks for soil monitoring, irrigation control, and crop management. These systems must operate reliably in challenging environmental conditions while providing cost-effective scalability for farms of varying sizes.

The automotive industry's transition toward connected and autonomous vehicles is creating demand for sophisticated microcontroller networks capable of processing distributed sensor data while maintaining safety-critical performance standards. Vehicle manufacturers require solutions that can scale across different vehicle platforms and model years.

Energy management applications, including smart grid implementations and renewable energy systems, represent growing market segments where scalable microcontroller networks enable efficient power distribution and consumption optimization across diverse infrastructure scales.

Current State and Challenges of MCU Network Scalability

Microcontroller networks have evolved significantly from simple point-to-point communications to complex distributed systems capable of handling thousands of interconnected nodes. Current implementations primarily utilize established protocols such as CAN bus, Zigbee, LoRaWAN, and Thread, each offering distinct advantages for specific application domains. Industrial automation systems commonly deploy CAN-based networks supporting up to 2032 nodes, while IoT applications increasingly rely on mesh networking protocols like Zigbee 3.0 that can theoretically scale to 65,000 devices per network.

The geographical distribution of MCU network technology development shows concentrated expertise in North America, Europe, and East Asia. Silicon Valley leads in wireless protocol innovation, while European manufacturers excel in industrial-grade wired solutions. Asian markets, particularly China and South Korea, dominate in manufacturing scalable MCU hardware platforms and cost-effective networking solutions.

Contemporary MCU networks face several critical scalability constraints that limit widespread deployment. Processing power limitations represent the most fundamental challenge, as traditional 8-bit and 16-bit microcontrollers struggle with complex routing algorithms and protocol stack management required for large-scale networks. Memory constraints further compound this issue, with typical MCUs offering only 32KB to 512KB of flash memory, insufficient for storing extensive routing tables and network topology information.

Network congestion emerges as node density increases, particularly in wireless implementations where spectrum sharing becomes problematic. Current collision avoidance mechanisms introduce significant latency penalties, with some networks experiencing exponential performance degradation beyond 100 active nodes. Power management presents another substantial hurdle, especially for battery-powered nodes where frequent communication protocols can drain power reserves within weeks rather than the desired multi-year operational periods.

Protocol overhead constitutes a major efficiency bottleneck in existing solutions. Traditional networking stacks consume 40-60% of available processing cycles on resource-constrained MCUs, leaving insufficient computational capacity for application-specific tasks. Additionally, most current protocols lack dynamic reconfiguration capabilities, requiring manual intervention when network topology changes occur.

Interoperability challenges persist across different vendor ecosystems, with proprietary extensions limiting seamless integration between MCU platforms from different manufacturers. Security implementation remains inadequate in many deployments, as cryptographic operations demand computational resources that many MCUs cannot spare while maintaining real-time performance requirements.

The geographical distribution of MCU network technology development shows concentrated expertise in North America, Europe, and East Asia. Silicon Valley leads in wireless protocol innovation, while European manufacturers excel in industrial-grade wired solutions. Asian markets, particularly China and South Korea, dominate in manufacturing scalable MCU hardware platforms and cost-effective networking solutions.

Contemporary MCU networks face several critical scalability constraints that limit widespread deployment. Processing power limitations represent the most fundamental challenge, as traditional 8-bit and 16-bit microcontrollers struggle with complex routing algorithms and protocol stack management required for large-scale networks. Memory constraints further compound this issue, with typical MCUs offering only 32KB to 512KB of flash memory, insufficient for storing extensive routing tables and network topology information.

Network congestion emerges as node density increases, particularly in wireless implementations where spectrum sharing becomes problematic. Current collision avoidance mechanisms introduce significant latency penalties, with some networks experiencing exponential performance degradation beyond 100 active nodes. Power management presents another substantial hurdle, especially for battery-powered nodes where frequent communication protocols can drain power reserves within weeks rather than the desired multi-year operational periods.

Protocol overhead constitutes a major efficiency bottleneck in existing solutions. Traditional networking stacks consume 40-60% of available processing cycles on resource-constrained MCUs, leaving insufficient computational capacity for application-specific tasks. Additionally, most current protocols lack dynamic reconfiguration capabilities, requiring manual intervention when network topology changes occur.

Interoperability challenges persist across different vendor ecosystems, with proprietary extensions limiting seamless integration between MCU platforms from different manufacturers. Security implementation remains inadequate in many deployments, as cryptographic operations demand computational resources that many MCUs cannot spare while maintaining real-time performance requirements.

Existing Scalable Microcontroller Network Solutions

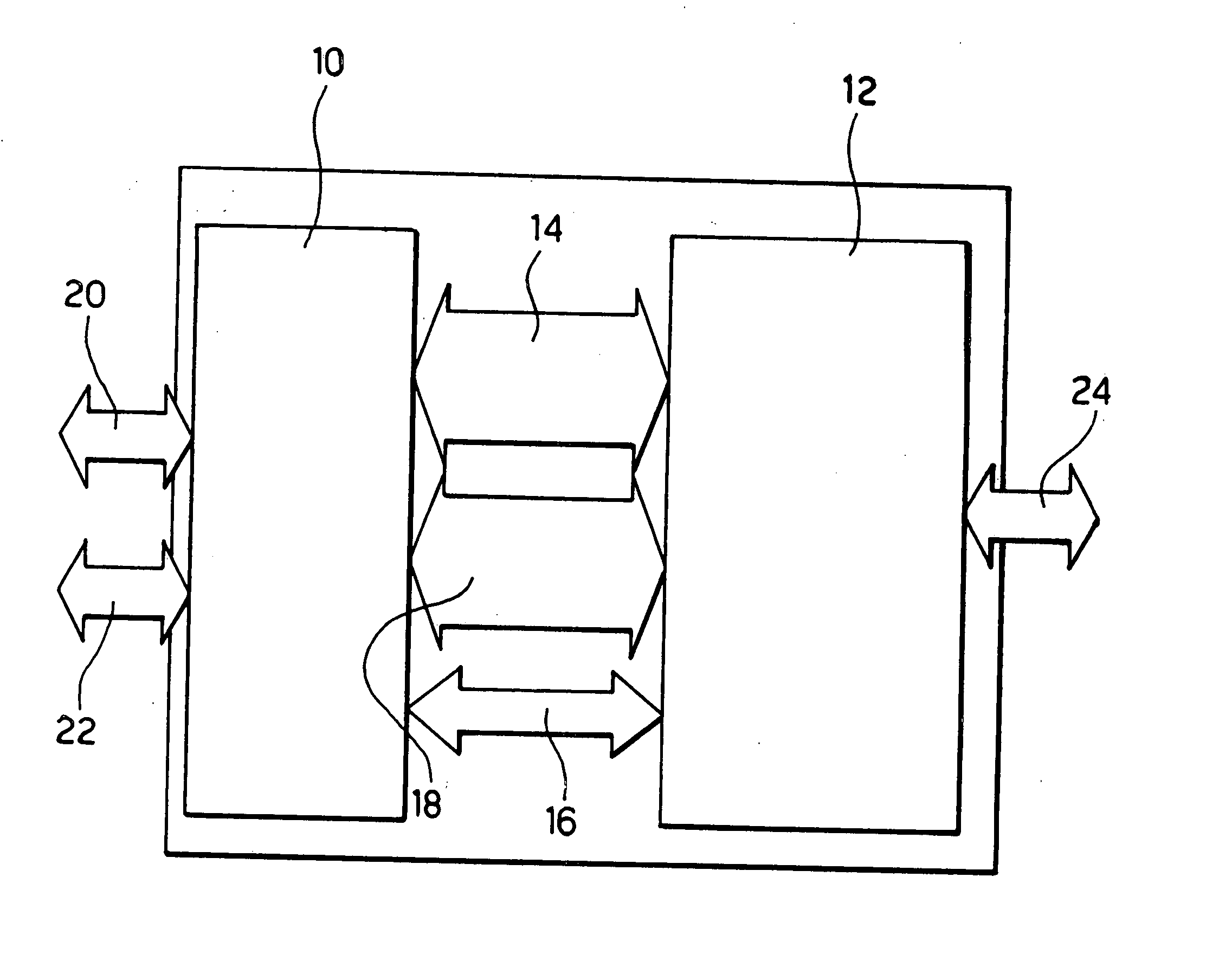

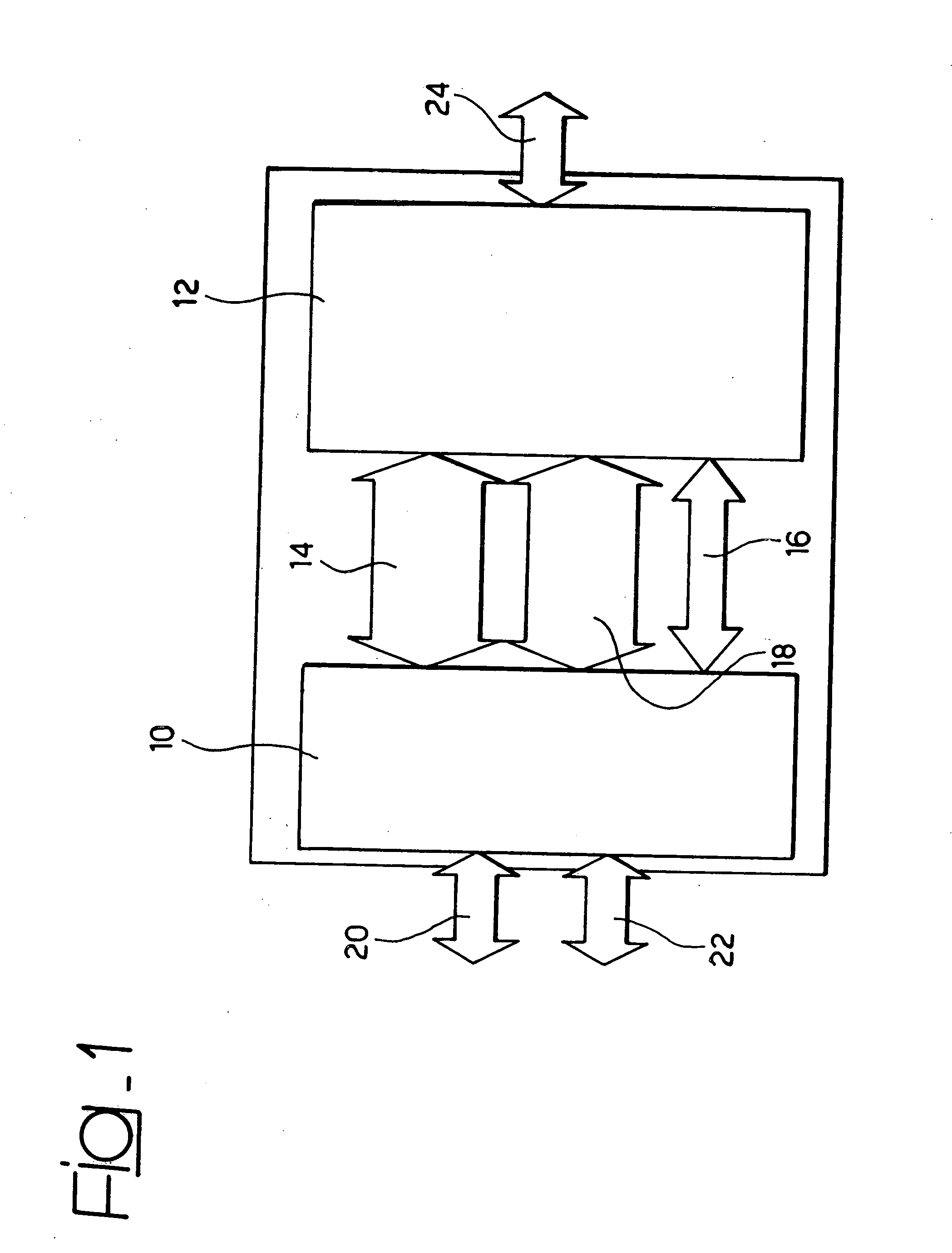

01 Hierarchical network architecture for scalability

Implementing hierarchical or layered network architectures enables microcontroller networks to scale efficiently by organizing devices into clusters or zones. This approach reduces communication overhead and allows for distributed processing across multiple levels. Master-slave configurations and multi-tier architectures facilitate management of large numbers of nodes while maintaining system performance and reducing bottlenecks in data transmission.- Hierarchical network architecture for scalability: Implementing hierarchical or layered network architectures enables microcontroller networks to scale efficiently by organizing devices into clusters or zones. This approach reduces communication overhead and allows for distributed processing, where local controllers manage subsets of devices while coordinating with higher-level controllers. The hierarchical structure facilitates easier network expansion and improves overall system performance by limiting broadcast domains and optimizing data flow paths.

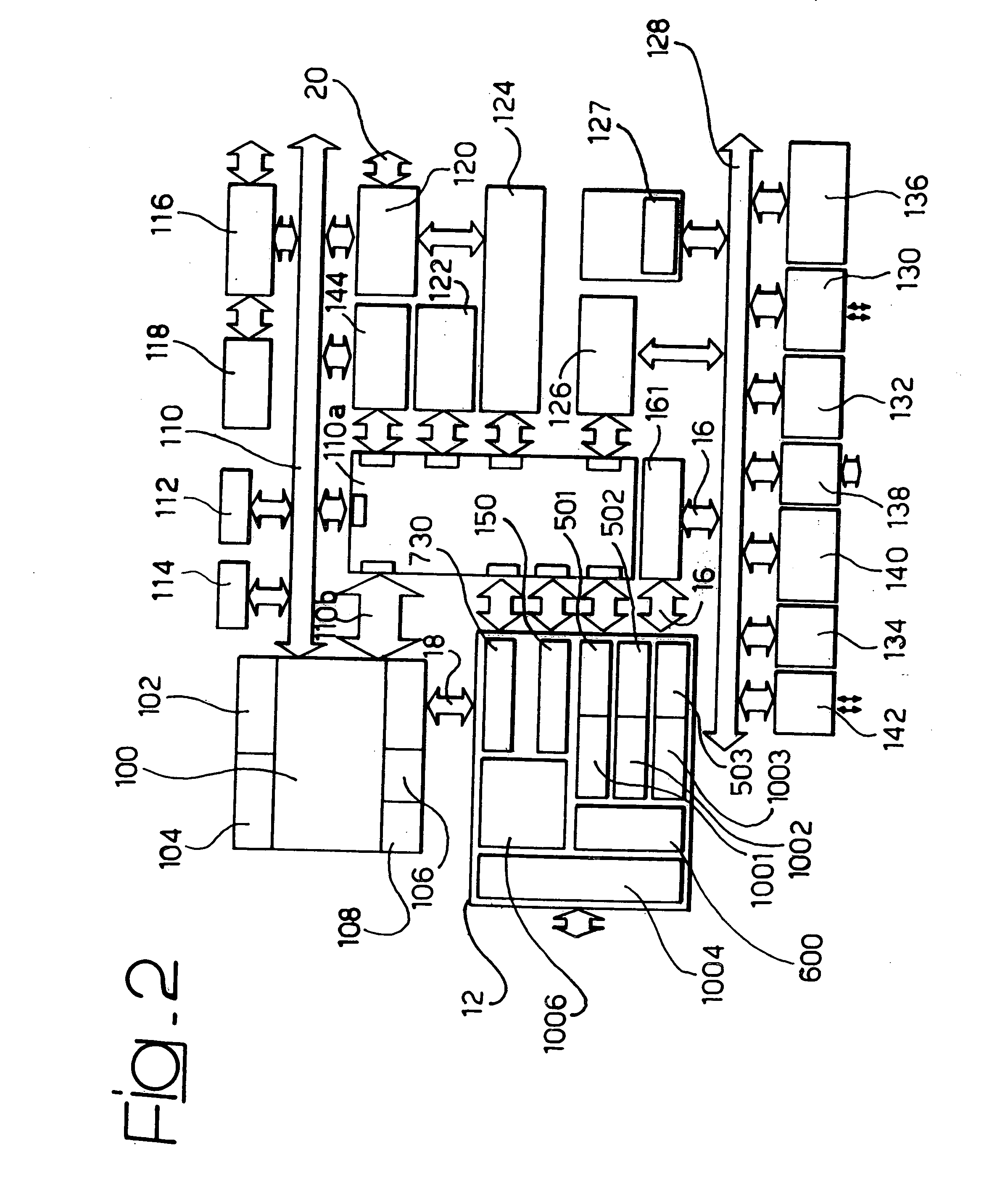

- Dynamic addressing and routing protocols: Scalable microcontroller networks employ dynamic addressing schemes and adaptive routing protocols that automatically configure network parameters as devices are added or removed. These mechanisms enable self-organizing networks that can accommodate varying numbers of nodes without manual reconfiguration. Advanced routing algorithms optimize communication paths based on network topology changes, ensuring efficient data transmission even as the network grows in size and complexity.

- Distributed processing and load balancing: Enhancing scalability through distributed processing architectures where computational tasks are shared among multiple microcontrollers rather than centralized in a single controller. Load balancing techniques distribute network traffic and processing demands across available resources, preventing bottlenecks and ensuring consistent performance as the network expands. This approach allows systems to handle increased data volumes and more complex operations without degrading response times.

- Modular communication protocols and interfaces: Utilizing modular and standardized communication protocols that support flexible network configurations and easy integration of additional microcontroller nodes. These protocols provide scalable data exchange mechanisms with efficient bandwidth utilization and support for various network topologies. Standardized interfaces enable interoperability between different microcontroller types and facilitate seamless network expansion without requiring extensive system redesign.

- Resource management and bandwidth optimization: Implementing intelligent resource management strategies that optimize bandwidth allocation, memory usage, and processing power across the microcontroller network. These techniques include data compression, priority-based scheduling, and efficient buffer management to maximize network capacity. Advanced bandwidth optimization methods ensure that critical communications maintain quality of service even as network size increases, while non-critical data is handled efficiently to prevent congestion.

02 Dynamic addressing and node management

Scalable microcontroller networks employ dynamic addressing schemes and automatic node discovery mechanisms to accommodate varying numbers of devices. These systems support plug-and-play functionality, allowing nodes to join or leave the network without manual reconfiguration. Address allocation protocols and self-organizing capabilities enable networks to expand seamlessly while maintaining unique identification for each microcontroller.Expand Specific Solutions03 Bandwidth optimization and traffic management

Techniques for optimizing bandwidth utilization include implementing priority-based scheduling, data aggregation, and efficient routing protocols. These methods prevent network congestion as the number of microcontrollers increases. Traffic shaping mechanisms and quality of service implementations ensure critical data transmission while managing communication loads across expanding networks.Expand Specific Solutions04 Modular and distributed processing architecture

Scalability is achieved through modular system designs that distribute processing tasks across multiple microcontrollers rather than relying on centralized control. This approach allows for incremental expansion by adding processing modules as needed. Distributed computing frameworks enable parallel processing and load balancing, ensuring system performance scales proportionally with network size.Expand Specific Solutions05 Power-efficient communication protocols

Scalable microcontroller networks implement low-power communication protocols and sleep mode coordination to manage energy consumption as network size grows. These protocols include duty cycling, wake-on-demand mechanisms, and energy-aware routing that extend battery life while supporting large numbers of nodes. Power management strategies ensure sustainable operation in expanded network configurations.Expand Specific Solutions

Key Players in MCU and Network System Industry

The microcontroller networks market for scalable systems is in a mature growth phase, driven by increasing IoT adoption and edge computing demands. The market demonstrates significant scale with established players like Intel Corp., Qualcomm Inc., and Apple Inc. leading processor innovation, while IBM and Hewlett Packard Enterprise provide enterprise infrastructure solutions. Technology maturity varies across segments, with companies like STMicroelectronics and Ambiq Micro advancing ultra-low-power microcontroller designs, and Mitsubishi Electric and Continental Teves focusing on industrial automation applications. The competitive landscape shows strong patent activity from major semiconductor firms, research institutions like University of California and Princeton University driving innovation, and specialized players like LED Smart Inc. integrating AI and IoT capabilities into microcontroller networks, indicating a technologically diverse and rapidly evolving ecosystem.

Intel Corp.

Technical Solution: Intel provides comprehensive microcontroller solutions through their 8051-based architecture and x86-based embedded processors for scalable network systems. Their approach leverages Intel Quark processors and Edison modules that enable distributed computing across microcontroller networks with integrated WiFi and Bluetooth connectivity. The platform supports real-time operating systems and provides development tools for network topology management, load balancing, and fault tolerance in distributed microcontroller environments. Intel's solution includes hardware abstraction layers that facilitate seamless communication between heterogeneous microcontroller nodes, enabling dynamic scaling based on computational demands and network traffic patterns.

Strengths: Established ecosystem with comprehensive development tools, strong performance optimization, and robust industrial-grade reliability. Weaknesses: Higher power consumption compared to ARM-based alternatives, relatively higher cost for large-scale deployments.

International Business Machines Corp.

Technical Solution: IBM's approach to scalable microcontroller networks focuses on edge computing integration with their Watson IoT platform and cognitive computing capabilities. Their solution implements distributed intelligence across microcontroller clusters using lightweight AI inference engines and adaptive networking protocols. The system employs dynamic resource allocation algorithms that automatically distribute computational loads across available microcontroller nodes while maintaining system coherence. IBM integrates blockchain-based security mechanisms for secure inter-node communication and implements predictive maintenance algorithms that monitor network health and performance metrics. Their platform supports hybrid cloud-edge architectures where microcontroller networks can seamlessly interface with cloud-based analytics and machine learning services.

Strengths: Advanced AI integration capabilities, enterprise-grade security features, and strong cloud connectivity. Weaknesses: Complex implementation requiring specialized expertise, potentially overkill for simple applications.

Core Technologies in Distributed MCU Systems

Architecture for dynamically reconfigurable system-on-chip arrangements, related methods and computer program product

PatentActiveUS20070088537A1

Innovation

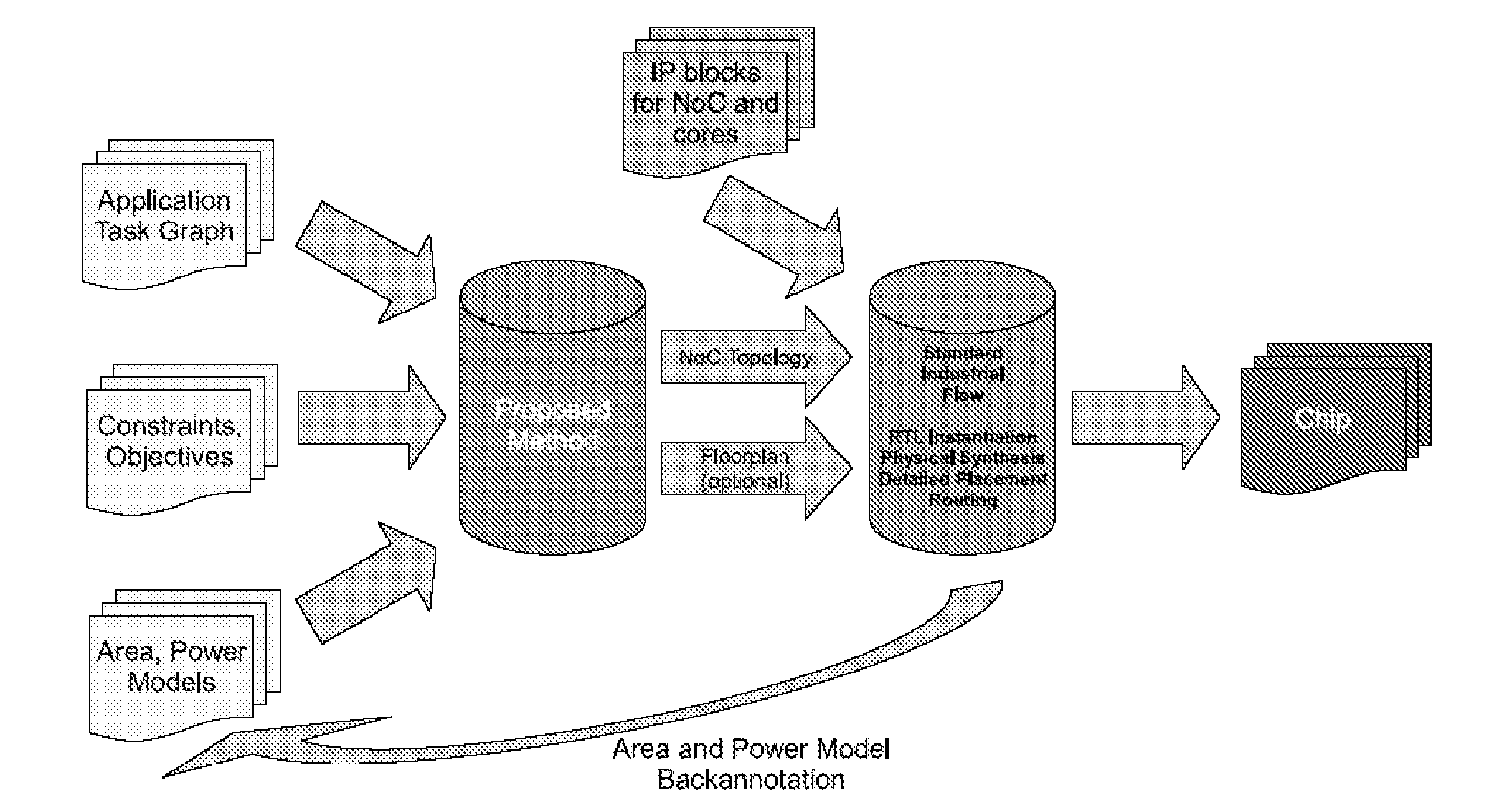

- A System-on-Chip (SoC) architecture integrating an ARM-based processor with three embedded FPGAs and a Network-On-Chip (NoC) that allows for scalable and flexible mapping of computational kernels, enabling independent programming of eFPGAs and communication through a message-passing architecture, supporting different levels of computational granularity.

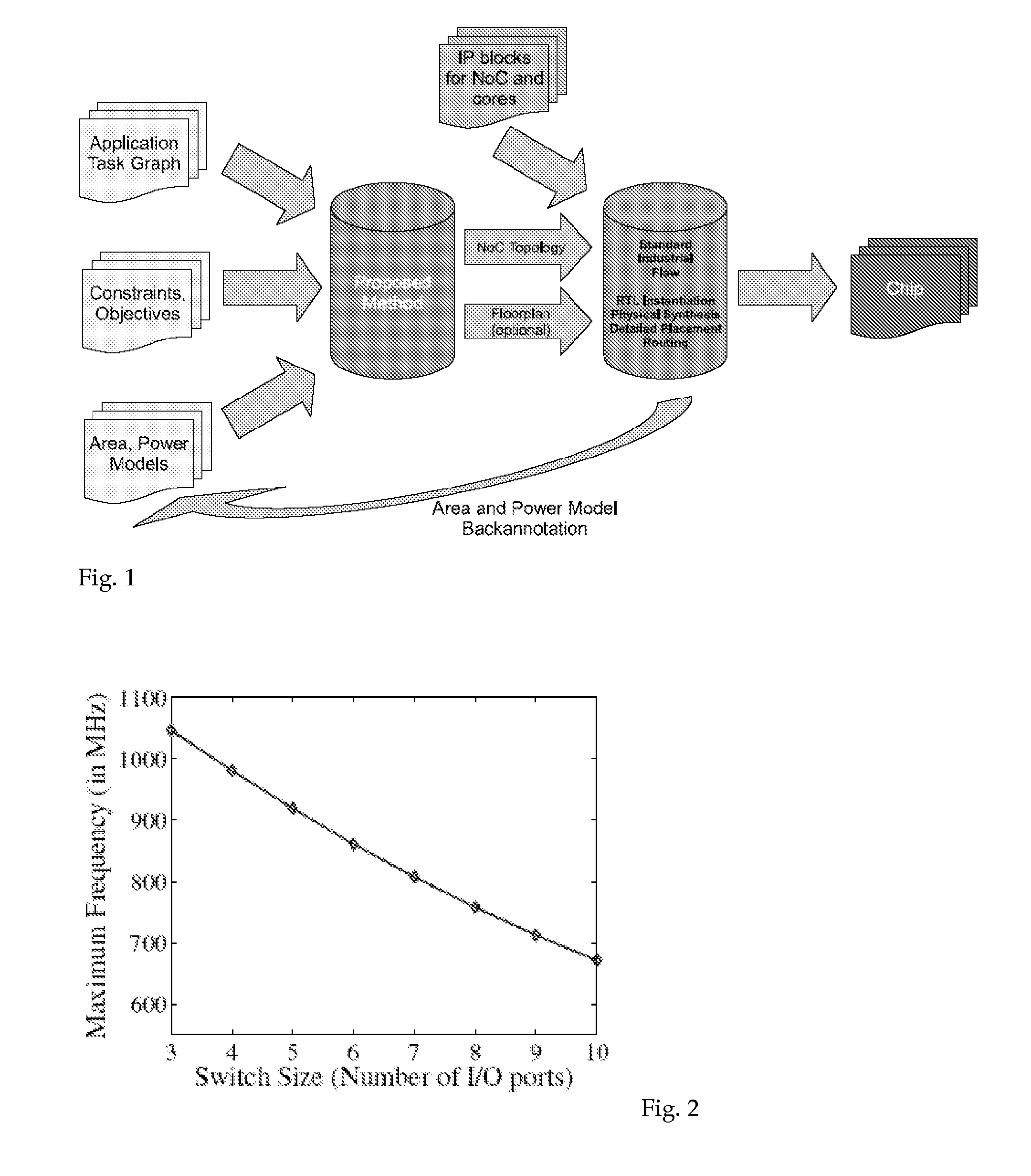

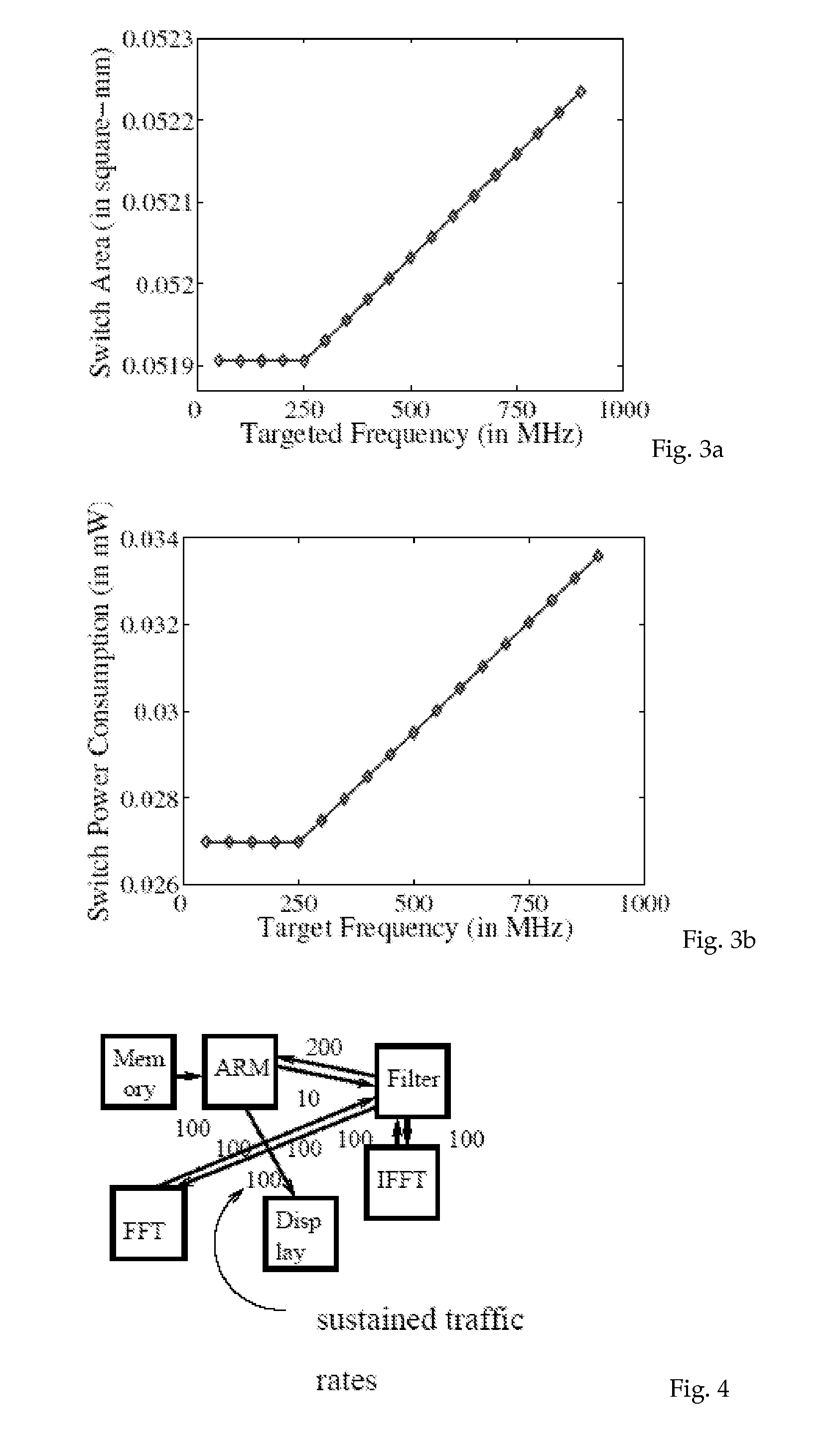

Method to design network-on-chip (NOC) - based communication systems

PatentActiveUS20090313592A1

Innovation

- A method for synthesizing application-specific NoC architectures that optimizes topology by modeling communication characteristics, configuring switches, establishing physical connectivity, calculating and iterating on various metrics such as power consumption, area, and speed to choose the optimal path, ensuring deadlock freedom without special hardware mechanisms, and integrating floorplan-aware design for accurate timing and power estimation.

Edge Computing Integration with MCU Networks

The integration of edge computing with microcontroller networks represents a paradigm shift in distributed computing architectures, enabling real-time data processing capabilities at the network periphery. This convergence addresses the growing demand for low-latency applications while reducing bandwidth requirements and enhancing system responsiveness in IoT deployments.

Edge computing integration transforms traditional MCU networks from simple data collection nodes into intelligent processing units capable of executing complex algorithms locally. Modern microcontrollers equipped with enhanced computational resources, including ARM Cortex-M series processors and specialized AI accelerators, can now handle machine learning inference, signal processing, and decision-making tasks previously reserved for cloud-based systems.

The architectural framework for edge-enabled MCU networks typically employs a hierarchical structure where individual microcontrollers serve as edge nodes, intermediate gateways provide aggregation and coordination functions, and cloud services handle long-term analytics and model updates. This distributed approach enables dynamic load balancing and fault tolerance while maintaining system scalability.

Key enabling technologies include lightweight containerization platforms specifically designed for resource-constrained environments, such as Docker variants optimized for embedded systems. These platforms facilitate seamless deployment and management of edge applications across heterogeneous MCU networks while ensuring consistent execution environments.

Communication protocols play a crucial role in edge integration, with emerging standards like MQTT-SN, CoAP, and specialized mesh networking protocols enabling efficient data exchange between edge nodes. These protocols incorporate features such as message prioritization, quality of service guarantees, and adaptive routing to optimize network performance under varying conditions.

Security considerations become paramount in edge-integrated MCU networks, requiring implementation of distributed authentication mechanisms, encrypted communication channels, and secure boot processes. Hardware security modules and trusted execution environments provide additional protection layers for sensitive edge computations.

The integration also necessitates sophisticated orchestration frameworks that can dynamically allocate computational tasks based on node capabilities, network conditions, and application requirements. These frameworks employ machine learning algorithms to predict optimal task placement and resource utilization patterns, ensuring efficient system operation across diverse deployment scenarios.

Edge computing integration transforms traditional MCU networks from simple data collection nodes into intelligent processing units capable of executing complex algorithms locally. Modern microcontrollers equipped with enhanced computational resources, including ARM Cortex-M series processors and specialized AI accelerators, can now handle machine learning inference, signal processing, and decision-making tasks previously reserved for cloud-based systems.

The architectural framework for edge-enabled MCU networks typically employs a hierarchical structure where individual microcontrollers serve as edge nodes, intermediate gateways provide aggregation and coordination functions, and cloud services handle long-term analytics and model updates. This distributed approach enables dynamic load balancing and fault tolerance while maintaining system scalability.

Key enabling technologies include lightweight containerization platforms specifically designed for resource-constrained environments, such as Docker variants optimized for embedded systems. These platforms facilitate seamless deployment and management of edge applications across heterogeneous MCU networks while ensuring consistent execution environments.

Communication protocols play a crucial role in edge integration, with emerging standards like MQTT-SN, CoAP, and specialized mesh networking protocols enabling efficient data exchange between edge nodes. These protocols incorporate features such as message prioritization, quality of service guarantees, and adaptive routing to optimize network performance under varying conditions.

Security considerations become paramount in edge-integrated MCU networks, requiring implementation of distributed authentication mechanisms, encrypted communication channels, and secure boot processes. Hardware security modules and trusted execution environments provide additional protection layers for sensitive edge computations.

The integration also necessitates sophisticated orchestration frameworks that can dynamically allocate computational tasks based on node capabilities, network conditions, and application requirements. These frameworks employ machine learning algorithms to predict optimal task placement and resource utilization patterns, ensuring efficient system operation across diverse deployment scenarios.

Power Management Strategies for Large-Scale MCU Systems

Power management represents one of the most critical challenges in large-scale microcontroller networks, where thousands of interconnected MCU nodes must operate efficiently while maintaining system-wide performance and reliability. The complexity increases exponentially as network size grows, demanding sophisticated strategies that balance individual node autonomy with coordinated system behavior.

Dynamic voltage and frequency scaling (DVFS) emerges as a fundamental approach for large-scale MCU deployments. This technique allows individual microcontrollers to adjust their operating parameters based on real-time computational demands and network conditions. Advanced implementations incorporate predictive algorithms that anticipate workload changes, enabling proactive power adjustments before performance degradation occurs. Machine learning models trained on historical usage patterns can optimize DVFS decisions across the entire network.

Hierarchical power management architectures provide scalable solutions for massive MCU networks. These systems organize nodes into clusters with designated power coordinators that manage local energy distribution and consumption policies. Regional power managers oversee multiple clusters, creating a tree-like structure that enables efficient decision-making without overwhelming central controllers. This approach reduces communication overhead while maintaining global optimization capabilities.

Sleep mode orchestration becomes increasingly complex in large networks where nodes must coordinate their dormant periods to maintain network connectivity and data flow. Advanced scheduling algorithms ensure that critical communication paths remain active while maximizing the number of nodes in low-power states. Time-synchronized wake-up protocols enable coordinated network activities while minimizing unnecessary power consumption during idle periods.

Energy harvesting integration offers promising opportunities for sustainable large-scale MCU networks. Distributed energy collection from solar, thermal, and kinetic sources can supplement traditional power supplies, reducing overall energy requirements. Smart energy routing protocols dynamically distribute harvested power across the network based on real-time demand and availability, creating resilient power ecosystems that adapt to environmental conditions.

Adaptive load balancing strategies redistribute computational tasks across the network to optimize power consumption patterns. These systems monitor individual node energy levels and processing capabilities, dynamically migrating workloads from power-constrained nodes to those with abundant energy resources. This approach extends overall network lifetime while maintaining performance requirements across diverse operational scenarios.

Dynamic voltage and frequency scaling (DVFS) emerges as a fundamental approach for large-scale MCU deployments. This technique allows individual microcontrollers to adjust their operating parameters based on real-time computational demands and network conditions. Advanced implementations incorporate predictive algorithms that anticipate workload changes, enabling proactive power adjustments before performance degradation occurs. Machine learning models trained on historical usage patterns can optimize DVFS decisions across the entire network.

Hierarchical power management architectures provide scalable solutions for massive MCU networks. These systems organize nodes into clusters with designated power coordinators that manage local energy distribution and consumption policies. Regional power managers oversee multiple clusters, creating a tree-like structure that enables efficient decision-making without overwhelming central controllers. This approach reduces communication overhead while maintaining global optimization capabilities.

Sleep mode orchestration becomes increasingly complex in large networks where nodes must coordinate their dormant periods to maintain network connectivity and data flow. Advanced scheduling algorithms ensure that critical communication paths remain active while maximizing the number of nodes in low-power states. Time-synchronized wake-up protocols enable coordinated network activities while minimizing unnecessary power consumption during idle periods.

Energy harvesting integration offers promising opportunities for sustainable large-scale MCU networks. Distributed energy collection from solar, thermal, and kinetic sources can supplement traditional power supplies, reducing overall energy requirements. Smart energy routing protocols dynamically distribute harvested power across the network based on real-time demand and availability, creating resilient power ecosystems that adapt to environmental conditions.

Adaptive load balancing strategies redistribute computational tasks across the network to optimize power consumption patterns. These systems monitor individual node energy levels and processing capabilities, dynamically migrating workloads from power-constrained nodes to those with abundant energy resources. This approach extends overall network lifetime while maintaining performance requirements across diverse operational scenarios.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!