Optimize Microcontroller Power Draw for Efficiency

FEB 25, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Microcontroller Power Optimization Background and Objectives

Microcontroller power optimization has emerged as a critical technological imperative driven by the exponential growth of battery-powered embedded systems and Internet of Things (IoT) devices. The evolution from simple 8-bit controllers to sophisticated 32-bit ARM Cortex-M processors has dramatically expanded computational capabilities while simultaneously intensifying power consumption challenges. Early microcontrollers operated with minimal power management features, relying primarily on basic sleep modes and clock gating techniques.

The technological landscape has transformed significantly over the past decade, with power efficiency becoming a primary design constraint rather than an afterthought. Modern applications demand extended battery life spanning months or years, particularly in remote sensing, wearable devices, and industrial monitoring systems. This shift has necessitated fundamental changes in both hardware architecture and software development methodologies.

Contemporary microcontroller designs incorporate sophisticated power management units featuring multiple sleep states, dynamic voltage and frequency scaling, and granular peripheral control. Advanced fabrication processes have enabled sub-threshold operation and ultra-low leakage designs, while maintaining computational performance. The integration of energy harvesting capabilities and adaptive power management algorithms represents the current frontier of development.

The primary technical objectives center on achieving sub-microampere average current consumption while maintaining system responsiveness and functionality. Key targets include extending battery life by 5-10x compared to conventional implementations, reducing standby current to nanowatt levels, and optimizing active mode efficiency through intelligent workload management. These objectives must be balanced against real-time performance requirements and system reliability constraints.

Future development trajectories focus on machine learning-driven power management, where embedded AI algorithms predict and adapt to usage patterns. The convergence of advanced semiconductor technologies, including FinFET processes and emerging memory architectures, promises further efficiency gains. Additionally, system-level optimization approaches integrating hardware-software co-design methodologies are becoming essential for achieving breakthrough power performance in next-generation embedded applications.

The technological landscape has transformed significantly over the past decade, with power efficiency becoming a primary design constraint rather than an afterthought. Modern applications demand extended battery life spanning months or years, particularly in remote sensing, wearable devices, and industrial monitoring systems. This shift has necessitated fundamental changes in both hardware architecture and software development methodologies.

Contemporary microcontroller designs incorporate sophisticated power management units featuring multiple sleep states, dynamic voltage and frequency scaling, and granular peripheral control. Advanced fabrication processes have enabled sub-threshold operation and ultra-low leakage designs, while maintaining computational performance. The integration of energy harvesting capabilities and adaptive power management algorithms represents the current frontier of development.

The primary technical objectives center on achieving sub-microampere average current consumption while maintaining system responsiveness and functionality. Key targets include extending battery life by 5-10x compared to conventional implementations, reducing standby current to nanowatt levels, and optimizing active mode efficiency through intelligent workload management. These objectives must be balanced against real-time performance requirements and system reliability constraints.

Future development trajectories focus on machine learning-driven power management, where embedded AI algorithms predict and adapt to usage patterns. The convergence of advanced semiconductor technologies, including FinFET processes and emerging memory architectures, promises further efficiency gains. Additionally, system-level optimization approaches integrating hardware-software co-design methodologies are becoming essential for achieving breakthrough power performance in next-generation embedded applications.

Market Demand for Low-Power Microcontroller Solutions

The global microcontroller market is experiencing unprecedented growth driven by the proliferation of Internet of Things devices, wearable technology, and battery-powered applications. This expansion has created substantial demand for energy-efficient microcontroller solutions that can operate for extended periods without frequent battery replacements or charging cycles.

Consumer electronics represent the largest segment driving low-power microcontroller adoption. Smartwatches, fitness trackers, wireless earbuds, and portable medical devices require microcontrollers that can maintain functionality while consuming minimal power. The wearable technology sector particularly emphasizes ultra-low power consumption to achieve multi-day or multi-week battery life, making power optimization a critical purchasing criterion.

Industrial automation and smart manufacturing applications constitute another significant demand driver. Wireless sensor networks deployed in factories, warehouses, and remote monitoring systems require microcontrollers capable of operating autonomously for months or years. These applications often involve harsh environments where battery replacement is costly or impractical, intensifying the need for power-efficient solutions.

The automotive industry presents growing opportunities for low-power microcontrollers, especially in electric vehicles and advanced driver assistance systems. Battery management systems, tire pressure monitoring, and keyless entry systems demand microcontrollers that minimize parasitic power draw to preserve vehicle battery life. As electric vehicle adoption accelerates, automotive manufacturers increasingly prioritize components that maximize driving range through reduced power consumption.

Smart home and building automation markets are expanding rapidly, creating demand for battery-powered sensors, smart locks, and environmental monitoring devices. These applications require microcontrollers that can maintain wireless connectivity while operating on coin cell batteries for several years. Energy harvesting applications in this sector further emphasize the importance of ultra-low power operation.

Healthcare and medical device markets represent high-value segments where power efficiency directly impacts patient care and device usability. Implantable devices, continuous glucose monitors, and remote patient monitoring systems require microcontrollers with exceptional power efficiency to minimize surgical interventions and improve patient compliance.

The competitive landscape reflects this market demand, with semiconductor manufacturers investing heavily in low-power microcontroller development. Advanced process technologies, specialized low-power design techniques, and integrated power management features have become standard differentiators in product portfolios, demonstrating the market's clear preference for energy-efficient solutions.

Consumer electronics represent the largest segment driving low-power microcontroller adoption. Smartwatches, fitness trackers, wireless earbuds, and portable medical devices require microcontrollers that can maintain functionality while consuming minimal power. The wearable technology sector particularly emphasizes ultra-low power consumption to achieve multi-day or multi-week battery life, making power optimization a critical purchasing criterion.

Industrial automation and smart manufacturing applications constitute another significant demand driver. Wireless sensor networks deployed in factories, warehouses, and remote monitoring systems require microcontrollers capable of operating autonomously for months or years. These applications often involve harsh environments where battery replacement is costly or impractical, intensifying the need for power-efficient solutions.

The automotive industry presents growing opportunities for low-power microcontrollers, especially in electric vehicles and advanced driver assistance systems. Battery management systems, tire pressure monitoring, and keyless entry systems demand microcontrollers that minimize parasitic power draw to preserve vehicle battery life. As electric vehicle adoption accelerates, automotive manufacturers increasingly prioritize components that maximize driving range through reduced power consumption.

Smart home and building automation markets are expanding rapidly, creating demand for battery-powered sensors, smart locks, and environmental monitoring devices. These applications require microcontrollers that can maintain wireless connectivity while operating on coin cell batteries for several years. Energy harvesting applications in this sector further emphasize the importance of ultra-low power operation.

Healthcare and medical device markets represent high-value segments where power efficiency directly impacts patient care and device usability. Implantable devices, continuous glucose monitors, and remote patient monitoring systems require microcontrollers with exceptional power efficiency to minimize surgical interventions and improve patient compliance.

The competitive landscape reflects this market demand, with semiconductor manufacturers investing heavily in low-power microcontroller development. Advanced process technologies, specialized low-power design techniques, and integrated power management features have become standard differentiators in product portfolios, demonstrating the market's clear preference for energy-efficient solutions.

Current Power Consumption Challenges in MCU Design

Modern microcontroller designs face unprecedented power consumption challenges as applications demand increasingly sophisticated functionality while maintaining extended battery life. The fundamental tension between computational performance and energy efficiency has become a critical bottleneck in embedded system development, particularly in IoT devices, wearable electronics, and remote sensing applications where power sources are severely constrained.

Static power consumption represents one of the most persistent challenges in contemporary MCU architectures. Leakage currents through transistor junctions continue to flow even when devices are in sleep or standby modes, creating a baseline power draw that accumulates significantly over extended operational periods. As semiconductor manufacturing processes shrink to smaller geometries, gate oxide thickness decreases, exacerbating leakage phenomena and making static power management increasingly complex.

Dynamic power consumption during active operation presents equally formidable obstacles. The relationship between clock frequency, supply voltage, and power consumption follows quadratic scaling laws, meaning that performance improvements often come at disproportionate energy costs. Traditional approaches of simply increasing clock speeds to enhance processing capability have reached practical limits due to thermal constraints and battery capacity restrictions.

Clock domain management across multiple subsystems introduces additional complexity layers. Modern MCUs integrate diverse functional blocks including analog-to-digital converters, communication peripherals, memory controllers, and processing cores, each with distinct power profiles and operational requirements. Coordinating these subsystems to minimize unnecessary power consumption while maintaining system responsiveness requires sophisticated power management strategies that many current designs struggle to implement effectively.

Memory subsystem power consumption poses particular challenges as data storage and retrieval operations consume substantial energy. Flash memory programming and erase cycles demand high voltage levels, while SRAM retention requires continuous power supply. The trade-offs between memory access speed, capacity, and power efficiency create design constraints that limit overall system optimization potential.

Peripheral interface power management remains problematic as communication protocols often require continuous monitoring or periodic wake-up cycles. Radio frequency modules, sensor interfaces, and external communication buses contribute significantly to overall power budgets, especially in applications requiring real-time responsiveness or frequent data transmission.

Temperature-dependent power variations further complicate optimization efforts as semiconductor characteristics change across operational temperature ranges. Power consumption patterns that appear optimal under laboratory conditions may prove inadequate in real-world deployment scenarios where environmental factors significantly impact device behavior and energy efficiency performance.

Static power consumption represents one of the most persistent challenges in contemporary MCU architectures. Leakage currents through transistor junctions continue to flow even when devices are in sleep or standby modes, creating a baseline power draw that accumulates significantly over extended operational periods. As semiconductor manufacturing processes shrink to smaller geometries, gate oxide thickness decreases, exacerbating leakage phenomena and making static power management increasingly complex.

Dynamic power consumption during active operation presents equally formidable obstacles. The relationship between clock frequency, supply voltage, and power consumption follows quadratic scaling laws, meaning that performance improvements often come at disproportionate energy costs. Traditional approaches of simply increasing clock speeds to enhance processing capability have reached practical limits due to thermal constraints and battery capacity restrictions.

Clock domain management across multiple subsystems introduces additional complexity layers. Modern MCUs integrate diverse functional blocks including analog-to-digital converters, communication peripherals, memory controllers, and processing cores, each with distinct power profiles and operational requirements. Coordinating these subsystems to minimize unnecessary power consumption while maintaining system responsiveness requires sophisticated power management strategies that many current designs struggle to implement effectively.

Memory subsystem power consumption poses particular challenges as data storage and retrieval operations consume substantial energy. Flash memory programming and erase cycles demand high voltage levels, while SRAM retention requires continuous power supply. The trade-offs between memory access speed, capacity, and power efficiency create design constraints that limit overall system optimization potential.

Peripheral interface power management remains problematic as communication protocols often require continuous monitoring or periodic wake-up cycles. Radio frequency modules, sensor interfaces, and external communication buses contribute significantly to overall power budgets, especially in applications requiring real-time responsiveness or frequent data transmission.

Temperature-dependent power variations further complicate optimization efforts as semiconductor characteristics change across operational temperature ranges. Power consumption patterns that appear optimal under laboratory conditions may prove inadequate in real-world deployment scenarios where environmental factors significantly impact device behavior and energy efficiency performance.

Existing Power Optimization Techniques for MCUs

01 Power management modes and sleep states

Microcontrollers can implement various power management modes including sleep, deep sleep, and standby states to reduce power consumption during idle periods. These modes allow selective shutdown of peripheral circuits and clock domains while maintaining essential functions. Wake-up mechanisms can be triggered by external interrupts or timers to resume normal operation when needed.- Power management modes and sleep states: Microcontrollers can implement various power management modes including sleep, deep sleep, and standby states to reduce power consumption during idle periods. These modes allow selective shutdown of peripheral circuits and clock domains while maintaining essential functions. Wake-up mechanisms can be triggered by external interrupts or internal timers to resume normal operation when needed.

- Dynamic voltage and frequency scaling: Power draw can be optimized by dynamically adjusting the operating voltage and clock frequency based on processing requirements. The microcontroller monitors workload and automatically scales voltage and frequency to match performance needs, reducing power consumption during low-demand periods. This technique balances performance requirements with energy efficiency.

- Power supply regulation and distribution: Efficient power supply circuits including voltage regulators, power switches, and distribution networks help minimize power losses in microcontroller systems. Multiple power domains can be independently controlled to selectively power down unused sections. Advanced regulation techniques maintain stable voltage levels while reducing quiescent current and improving overall power efficiency.

- Clock gating and power domain isolation: Power consumption can be reduced by selectively disabling clock signals to inactive functional blocks through clock gating techniques. Power domain isolation allows complete shutdown of unused circuit sections while preventing leakage currents. These methods enable fine-grained control over power distribution across different microcontroller subsystems.

- Low-power peripheral and interface design: Microcontroller peripherals and communication interfaces can be designed with low-power operation modes to minimize current draw during data transfer and processing. Techniques include duty-cycled operation, reduced drive strength, and optimized protocol implementations. Power-aware peripheral design ensures that interface circuits consume minimal energy while maintaining functionality.

02 Dynamic voltage and frequency scaling

Power draw can be optimized by dynamically adjusting the operating voltage and clock frequency based on processing requirements. The microcontroller can scale down voltage and frequency during low-demand periods and increase them when higher performance is needed. This adaptive approach balances performance requirements with power efficiency.Expand Specific Solutions03 Clock gating and power domain isolation

Selective clock gating techniques disable clock signals to unused functional blocks within the microcontroller to eliminate dynamic power consumption. Power domain isolation allows independent control of voltage supplies to different circuit sections, enabling complete shutdown of inactive domains while maintaining operation in active areas.Expand Specific Solutions04 Low-power peripheral design and control

Peripheral circuits such as timers, communication interfaces, and analog-to-digital converters can be designed with low-power operation modes. Individual peripherals can be enabled or disabled based on application requirements, and their operating parameters can be configured to minimize current consumption while maintaining necessary functionality.Expand Specific Solutions05 Power monitoring and measurement circuits

Integrated power monitoring circuits enable real-time measurement of current consumption and voltage levels within the microcontroller system. These measurement capabilities allow for power profiling, optimization of software routines, and implementation of adaptive power management strategies based on actual consumption patterns.Expand Specific Solutions

Key Players in Low-Power Microcontroller Industry

The microcontroller power optimization market is experiencing rapid growth driven by the proliferation of IoT devices and battery-powered applications, with the industry transitioning from early adoption to mainstream implementation. Market expansion is fueled by increasing demand for ultra-low-power solutions across automotive, industrial, and consumer electronics sectors. Technology maturity varies significantly among key players: established semiconductor giants like Intel, Qualcomm, Samsung Electronics, and Renesas Electronics lead with advanced power management architectures and extensive IP portfolios. Specialized companies such as Ambiq Micro pioneer ultra-low-power innovations, while Microchip Technology and Etron Technology focus on optimized microcontroller designs. Traditional industrial leaders including Siemens, Bosch, and ABB integrate power-efficient solutions into broader automation systems. Emerging players like Shanghai Sillumin Semiconductor and Eeasy Technology contribute innovative approaches, particularly in AI-enhanced power management. The competitive landscape shows consolidation around proven low-power architectures, with differentiation occurring through specialized applications and integrated system solutions.

Ambiq Micro, Inc.

Technical Solution: Ambiq Micro specializes in ultra-low power microcontrollers using their proprietary Subthreshold Power Optimized Technology (SPOT) platform. Their Apollo series MCUs operate in the subthreshold voltage region, achieving power consumption as low as 6 microamps per MHz while maintaining full functionality. The technology enables always-on applications by utilizing advanced power gating, dynamic voltage scaling, and intelligent sleep modes. Their MCUs feature multiple power domains that can be independently controlled, allowing selective shutdown of unused peripherals. The company's approach combines hardware-level optimizations with software-configurable power management, enabling battery life extensions of 10x compared to traditional MCUs in IoT applications.

Strengths: Industry-leading ultra-low power consumption, proven SPOT technology, excellent for battery-powered IoT devices. Weaknesses: Limited processing power compared to higher-performance MCUs, smaller ecosystem than major competitors.

Intel Corp.

Technical Solution: Intel's microcontroller power optimization focuses on their Quark and Atom-based embedded processors, implementing advanced 14nm and 10nm process technologies with sophisticated power management units (PMUs). Their approach utilizes dynamic frequency and voltage scaling (DVFS), where the processor automatically adjusts clock speeds and voltages based on workload demands. Intel's Enhanced SpeedStep technology can reduce power consumption by up to 50% during low-activity periods. The architecture includes multiple C-states for deep sleep modes, intelligent turbo boost for performance scaling, and integrated power gates that can shut down unused functional units. Their MCUs also feature thermal design power (TDP) optimization and real-time power monitoring capabilities for adaptive power management.

Strengths: Advanced process technology, sophisticated power management features, strong performance-per-watt ratio. Weaknesses: Higher cost compared to dedicated MCU vendors, complex architecture may be overkill for simple applications.

Core Innovations in Ultra-Low Power MCU Design

Power Reduction in Microcontrollers

PatentActiveUS20100229011A1

Innovation

- Implementing a clock control system that allows specific peripheral modules to reactivate their clocks in response to internal or external trigger events, using an event handler and clock generator to resume clock generation only for the requesting modules, minimizing overall power consumption.

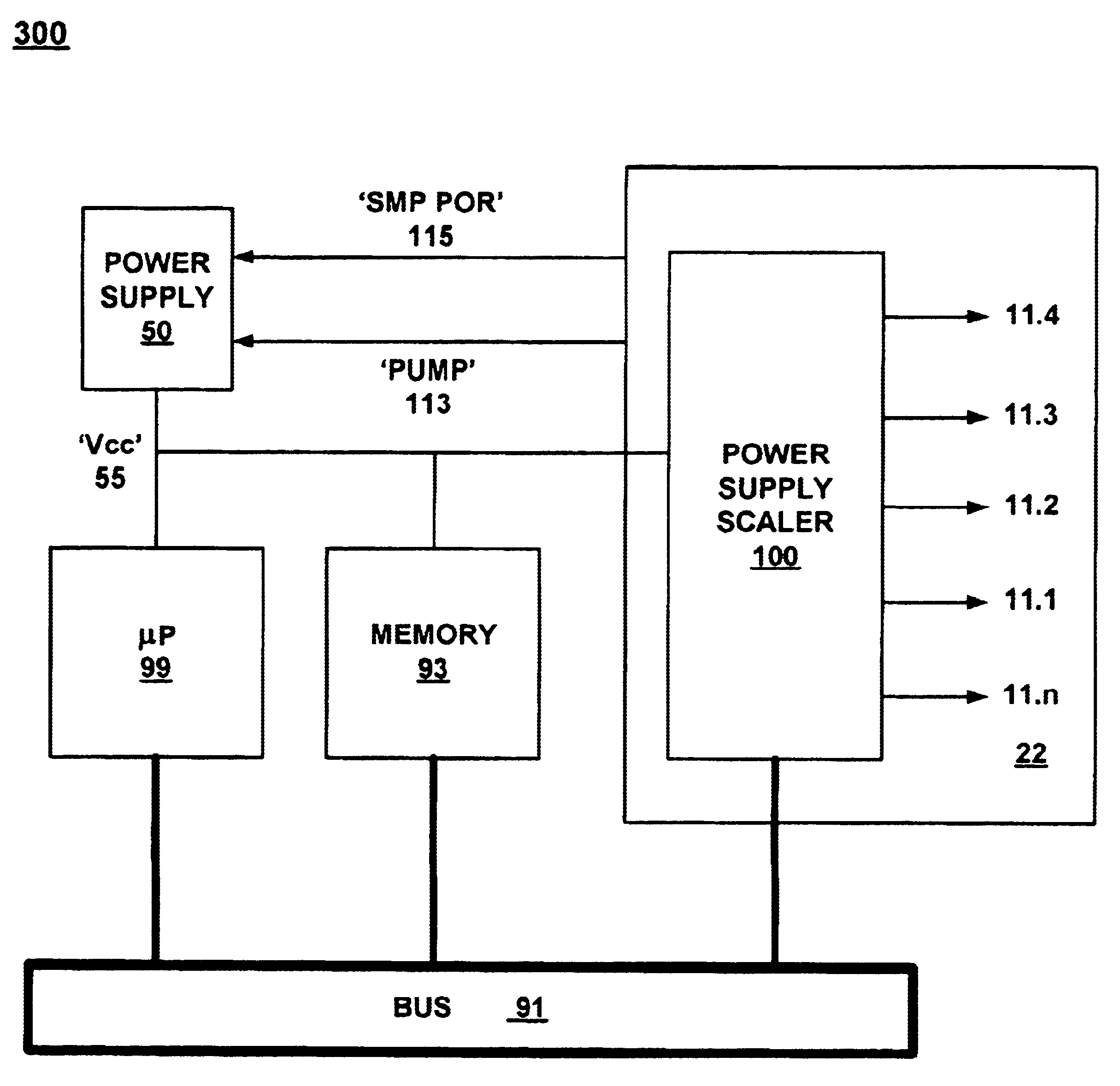

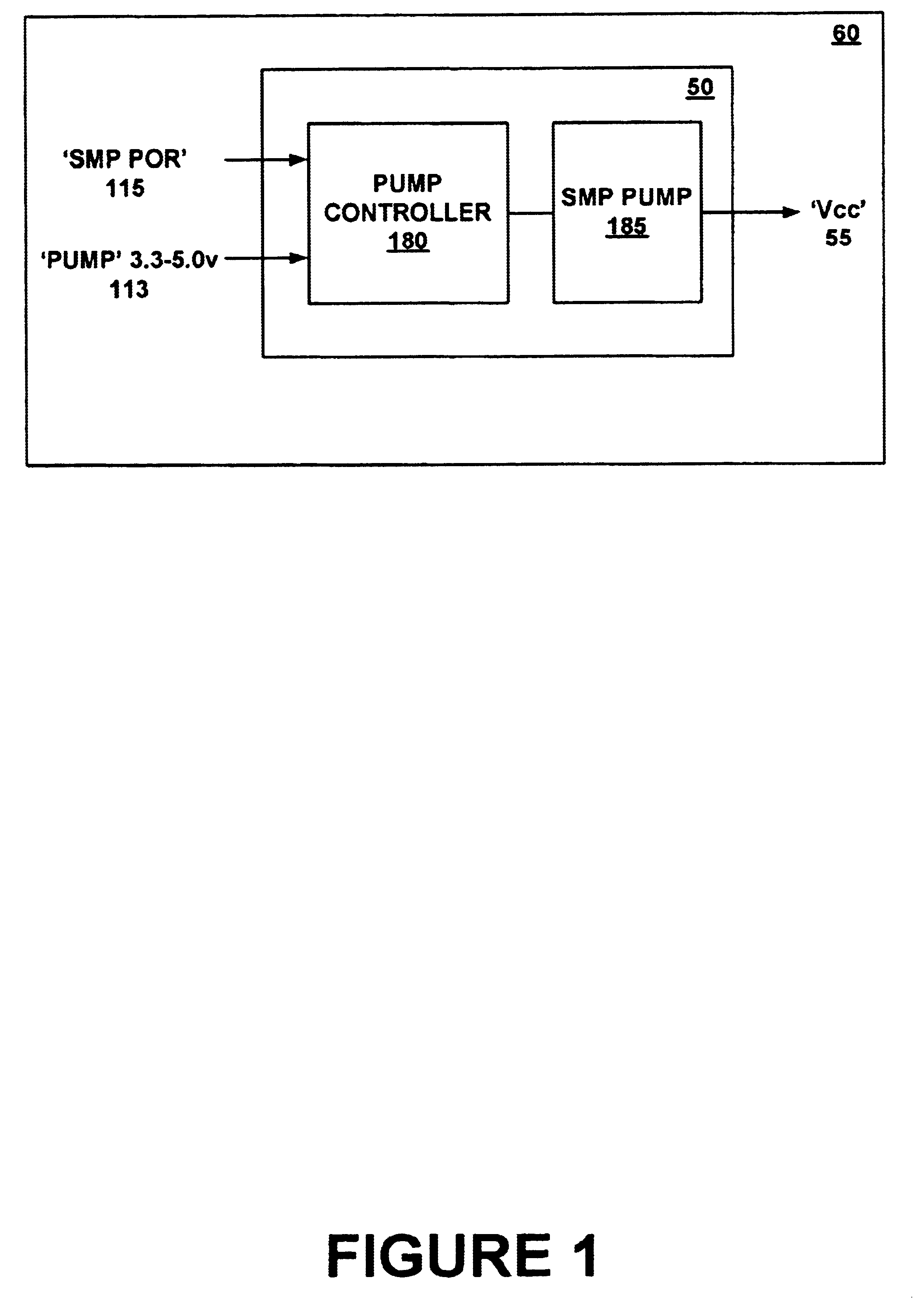

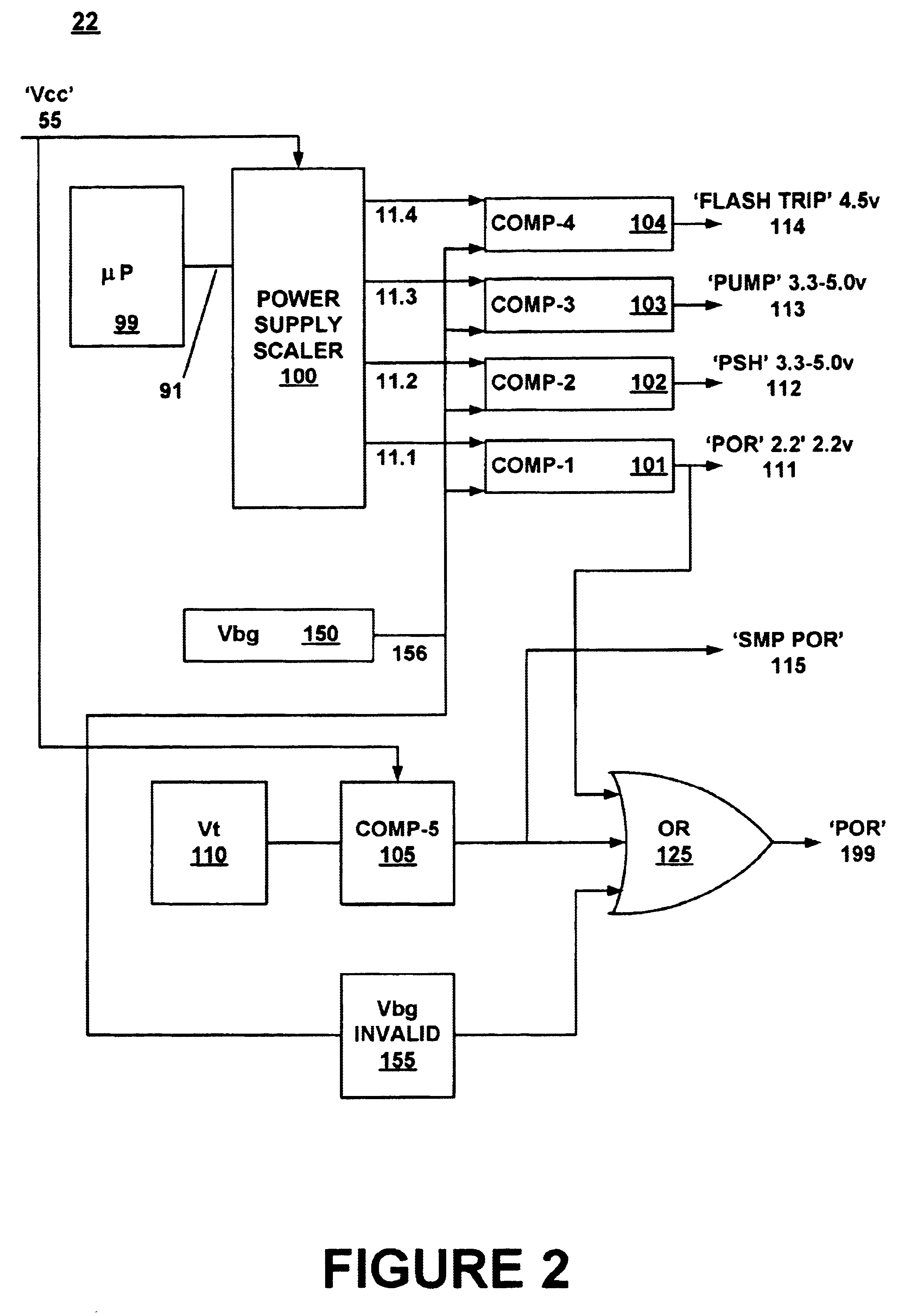

Method and system for interaction between a processor and a power on reset circuit to dynamically control power states in a microcontroller

PatentInactiveUS6854067B1

Innovation

- A method and system that dynamically controls microcontroller power states by interacting between a processor and a power on reset (POR) circuit to optimize switch mode pump (SMP) output, utilizing existing POR circuitry and processor resources without additional system demands.

Energy Efficiency Standards for Embedded Systems

Energy efficiency standards for embedded systems have evolved significantly over the past decade, driven by the proliferation of IoT devices and battery-powered applications. These standards establish critical benchmarks for microcontroller power consumption, defining acceptable operational parameters that balance performance requirements with energy conservation objectives.

The IEEE 1149.1 standard, commonly known as JTAG, has been extended to include power management specifications that enable standardized low-power testing and debugging protocols. This extension allows developers to validate power optimization implementations across different microcontroller architectures while maintaining compliance with established testing methodologies.

ENERGY STAR specifications have expanded beyond traditional computing devices to encompass embedded systems, particularly those deployed in smart building applications. These specifications mandate specific power consumption thresholds during active, idle, and sleep modes, with particular emphasis on wake-up latency and power transition efficiency. Microcontrollers must demonstrate compliance through standardized testing procedures that measure power draw across various operational scenarios.

The IEC 62430 standard addresses environmentally conscious design for electrical and electronic products, establishing lifecycle energy consumption metrics that directly impact microcontroller selection and optimization strategies. This standard requires comprehensive power profiling throughout the device operational lifecycle, influencing design decisions regarding clock frequency scaling, peripheral management, and sleep mode implementation.

Industry-specific standards such as ISO 26262 for automotive applications incorporate functional safety requirements that intersect with power efficiency mandates. These standards necessitate fail-safe power management systems that maintain critical functionality while optimizing overall energy consumption, creating complex design constraints for automotive microcontroller implementations.

The USB-IF Power Delivery specification has established standardized power negotiation protocols that embedded systems must support when interfacing with external power sources. This standard defines specific power state transitions and communication protocols that microcontrollers must implement to achieve optimal power utilization while maintaining interoperability with various power delivery systems.

Emerging standards from organizations like the Green Electronics Council are developing comprehensive energy efficiency metrics specifically targeting embedded systems in consumer electronics, establishing performance benchmarks that will significantly influence future microcontroller power optimization strategies and implementation approaches.

The IEEE 1149.1 standard, commonly known as JTAG, has been extended to include power management specifications that enable standardized low-power testing and debugging protocols. This extension allows developers to validate power optimization implementations across different microcontroller architectures while maintaining compliance with established testing methodologies.

ENERGY STAR specifications have expanded beyond traditional computing devices to encompass embedded systems, particularly those deployed in smart building applications. These specifications mandate specific power consumption thresholds during active, idle, and sleep modes, with particular emphasis on wake-up latency and power transition efficiency. Microcontrollers must demonstrate compliance through standardized testing procedures that measure power draw across various operational scenarios.

The IEC 62430 standard addresses environmentally conscious design for electrical and electronic products, establishing lifecycle energy consumption metrics that directly impact microcontroller selection and optimization strategies. This standard requires comprehensive power profiling throughout the device operational lifecycle, influencing design decisions regarding clock frequency scaling, peripheral management, and sleep mode implementation.

Industry-specific standards such as ISO 26262 for automotive applications incorporate functional safety requirements that intersect with power efficiency mandates. These standards necessitate fail-safe power management systems that maintain critical functionality while optimizing overall energy consumption, creating complex design constraints for automotive microcontroller implementations.

The USB-IF Power Delivery specification has established standardized power negotiation protocols that embedded systems must support when interfacing with external power sources. This standard defines specific power state transitions and communication protocols that microcontrollers must implement to achieve optimal power utilization while maintaining interoperability with various power delivery systems.

Emerging standards from organizations like the Green Electronics Council are developing comprehensive energy efficiency metrics specifically targeting embedded systems in consumer electronics, establishing performance benchmarks that will significantly influence future microcontroller power optimization strategies and implementation approaches.

Sustainability Impact of Power-Optimized MCU Design

The optimization of microcontroller power consumption represents a critical pathway toward achieving broader sustainability objectives in the electronics industry. Power-optimized MCU designs directly contribute to reduced energy consumption across countless applications, from IoT devices to automotive systems, creating a cascading effect that significantly impacts global energy usage patterns.

Environmental benefits manifest through multiple channels when implementing power-efficient microcontroller architectures. Reduced operational power requirements translate to lower electricity consumption throughout device lifecycles, particularly impactful in battery-powered applications where extended operational periods reduce replacement frequency. This reduction in battery turnover directly decreases electronic waste generation and minimizes the environmental burden associated with battery manufacturing and disposal processes.

The carbon footprint reduction achieved through optimized MCU power draw extends beyond individual device operation. Data centers hosting millions of connected devices experience substantial energy savings when each endpoint consumes less power. Conservative estimates suggest that widespread adoption of power-optimized microcontrollers could reduce global electronics-related energy consumption by 15-20% within the next decade, contributing meaningfully to international carbon reduction targets.

Economic sustainability emerges as manufacturers adopt power-efficient designs, creating cost advantages that incentivize broader market adoption. Lower operational costs for end-users drive demand for energy-efficient products, establishing positive feedback loops that accelerate sustainable technology deployment. This market dynamic encourages continued investment in power optimization research and development.

Long-term sustainability implications include reduced strain on electrical grid infrastructure and decreased dependency on fossil fuel-based energy generation. As renewable energy sources become more prevalent, power-optimized devices maximize the effectiveness of clean energy investments by requiring less generation capacity to support equivalent functionality.

The circular economy benefits from extended device lifespans enabled by efficient power management, reducing replacement cycles and associated manufacturing impacts. Power optimization technologies also enable new applications in energy-harvesting scenarios, where devices can operate entirely on ambient energy sources, representing the ultimate sustainability achievement in microcontroller applications.

Environmental benefits manifest through multiple channels when implementing power-efficient microcontroller architectures. Reduced operational power requirements translate to lower electricity consumption throughout device lifecycles, particularly impactful in battery-powered applications where extended operational periods reduce replacement frequency. This reduction in battery turnover directly decreases electronic waste generation and minimizes the environmental burden associated with battery manufacturing and disposal processes.

The carbon footprint reduction achieved through optimized MCU power draw extends beyond individual device operation. Data centers hosting millions of connected devices experience substantial energy savings when each endpoint consumes less power. Conservative estimates suggest that widespread adoption of power-optimized microcontrollers could reduce global electronics-related energy consumption by 15-20% within the next decade, contributing meaningfully to international carbon reduction targets.

Economic sustainability emerges as manufacturers adopt power-efficient designs, creating cost advantages that incentivize broader market adoption. Lower operational costs for end-users drive demand for energy-efficient products, establishing positive feedback loops that accelerate sustainable technology deployment. This market dynamic encourages continued investment in power optimization research and development.

Long-term sustainability implications include reduced strain on electrical grid infrastructure and decreased dependency on fossil fuel-based energy generation. As renewable energy sources become more prevalent, power-optimized devices maximize the effectiveness of clean energy investments by requiring less generation capacity to support equivalent functionality.

The circular economy benefits from extended device lifespans enabled by efficient power management, reducing replacement cycles and associated manufacturing impacts. Power optimization technologies also enable new applications in energy-harvesting scenarios, where devices can operate entirely on ambient energy sources, representing the ultimate sustainability achievement in microcontroller applications.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!