Multi Chip Module vs SoC: Performance in IoT Devices

MAR 12, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

MCM vs SoC IoT Performance Challenges and Goals

The Internet of Things ecosystem faces a fundamental architectural decision between Multi Chip Module (MCM) and System-on-Chip (SoC) implementations, each presenting distinct performance characteristics that directly impact device functionality, power consumption, and market viability. As IoT deployments scale exponentially across industrial, consumer, and infrastructure applications, the choice between these two integration approaches has become increasingly critical for achieving optimal performance metrics.

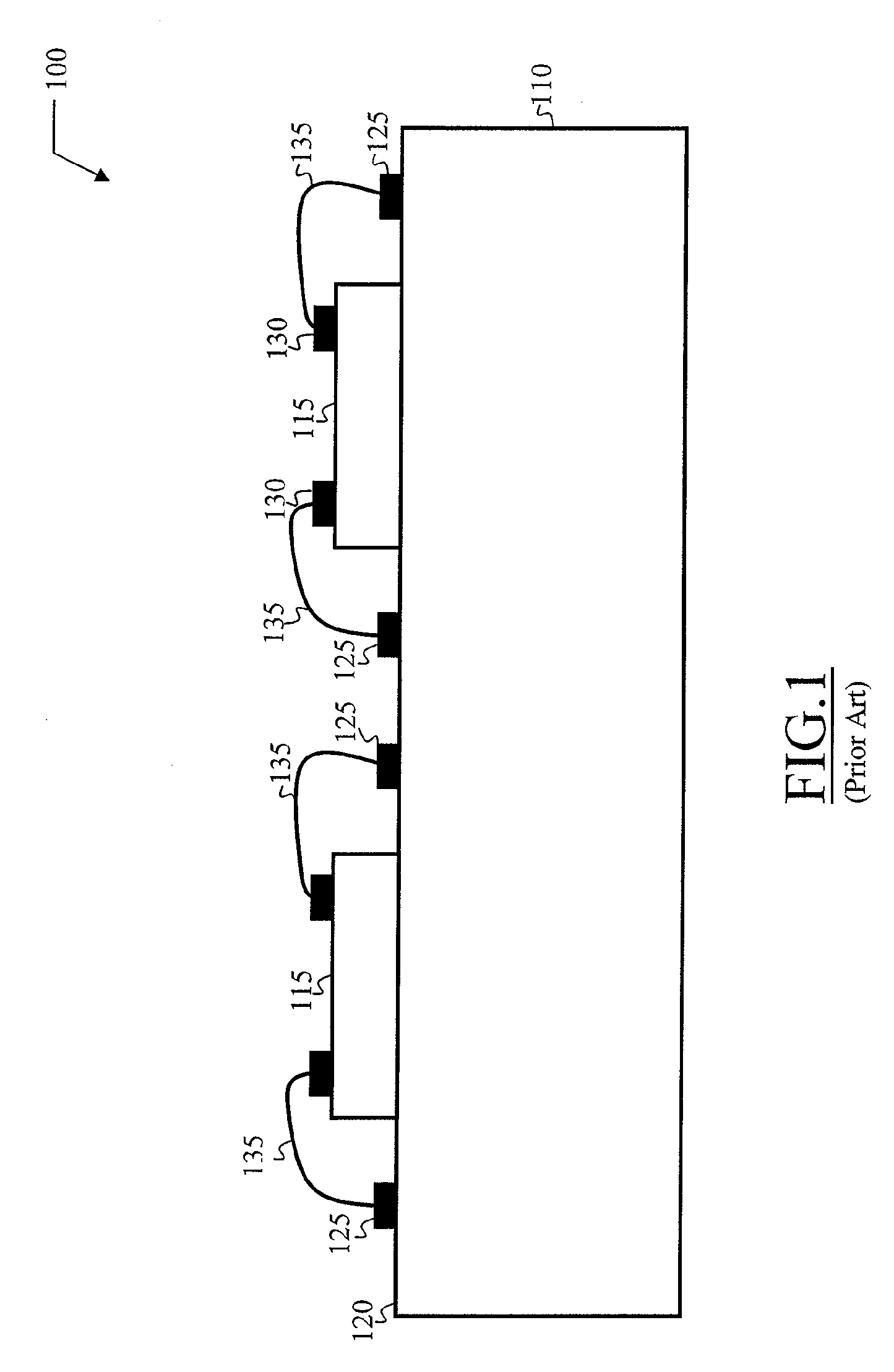

The evolution of semiconductor packaging technologies has transformed from discrete component assemblies to highly integrated solutions, driven by the relentless demand for miniaturization, enhanced functionality, and improved power efficiency. MCM technology emerged as an intermediate solution, enabling the integration of multiple specialized chips within a single package while maintaining design flexibility and manufacturing cost advantages. Conversely, SoC technology represents the pinnacle of integration, consolidating entire system functionality onto a single silicon die.

Historical development patterns reveal that MCM solutions initially dominated complex system implementations due to yield advantages and design modularity. However, advancing lithography processes and design methodologies have progressively shifted the balance toward SoC implementations, particularly in high-volume consumer applications where cost optimization and form factor constraints are paramount.

The primary technical objective centers on optimizing the performance-power-cost triangle while addressing the unique constraints of IoT applications. These devices typically operate under severe power budgets, require extended operational lifespans, and must maintain reliable connectivity across diverse environmental conditions. Performance optimization encompasses multiple dimensions including computational throughput, real-time response capabilities, energy efficiency, and thermal management.

Contemporary IoT applications demand increasingly sophisticated processing capabilities to handle edge computing tasks, machine learning inference, and complex sensor fusion algorithms. This computational complexity must be balanced against stringent power consumption requirements, as many IoT devices rely on battery power or energy harvesting mechanisms. The architectural choice between MCM and SoC directly influences the achievable performance envelope and determines the feasibility of implementing advanced features within the given power and thermal constraints.

Emerging application domains such as autonomous systems, industrial IoT, and smart city infrastructure are pushing the boundaries of traditional IoT performance requirements, necessitating careful evaluation of integration strategies to meet evolving technical specifications while maintaining economic viability across diverse deployment scenarios.

The evolution of semiconductor packaging technologies has transformed from discrete component assemblies to highly integrated solutions, driven by the relentless demand for miniaturization, enhanced functionality, and improved power efficiency. MCM technology emerged as an intermediate solution, enabling the integration of multiple specialized chips within a single package while maintaining design flexibility and manufacturing cost advantages. Conversely, SoC technology represents the pinnacle of integration, consolidating entire system functionality onto a single silicon die.

Historical development patterns reveal that MCM solutions initially dominated complex system implementations due to yield advantages and design modularity. However, advancing lithography processes and design methodologies have progressively shifted the balance toward SoC implementations, particularly in high-volume consumer applications where cost optimization and form factor constraints are paramount.

The primary technical objective centers on optimizing the performance-power-cost triangle while addressing the unique constraints of IoT applications. These devices typically operate under severe power budgets, require extended operational lifespans, and must maintain reliable connectivity across diverse environmental conditions. Performance optimization encompasses multiple dimensions including computational throughput, real-time response capabilities, energy efficiency, and thermal management.

Contemporary IoT applications demand increasingly sophisticated processing capabilities to handle edge computing tasks, machine learning inference, and complex sensor fusion algorithms. This computational complexity must be balanced against stringent power consumption requirements, as many IoT devices rely on battery power or energy harvesting mechanisms. The architectural choice between MCM and SoC directly influences the achievable performance envelope and determines the feasibility of implementing advanced features within the given power and thermal constraints.

Emerging application domains such as autonomous systems, industrial IoT, and smart city infrastructure are pushing the boundaries of traditional IoT performance requirements, necessitating careful evaluation of integration strategies to meet evolving technical specifications while maintaining economic viability across diverse deployment scenarios.

Market Demand for Optimized IoT Device Architectures

The global IoT ecosystem is experiencing unprecedented growth, driving substantial demand for optimized device architectures that can balance performance, power efficiency, and cost-effectiveness. This expansion spans across diverse sectors including smart cities, industrial automation, healthcare monitoring, and consumer electronics, each presenting unique architectural requirements that influence the choice between Multi Chip Module and System-on-Chip implementations.

Edge computing applications represent a particularly significant demand driver, requiring IoT devices capable of local data processing and real-time decision making. These applications necessitate architectures that can handle complex computational tasks while maintaining the low power consumption essential for battery-operated devices. The growing emphasis on artificial intelligence at the edge further amplifies this demand, as devices must accommodate specialized processing units for machine learning inference.

Industrial IoT deployments are increasingly seeking architectures that offer superior reliability and modularity. Manufacturing environments demand devices that can withstand harsh conditions while providing consistent performance over extended operational periods. The ability to customize and upgrade specific components without redesigning entire systems has become a critical requirement, influencing architectural preferences toward solutions that offer greater flexibility.

Consumer IoT markets are driving demand for cost-optimized architectures that can deliver adequate performance while maintaining competitive pricing. Smart home devices, wearables, and connected appliances require architectures that minimize bill-of-materials costs while ensuring reliable connectivity and sufficient processing capabilities for their intended functions.

The proliferation of 5G networks is creating new architectural demands as IoT devices must support higher data throughput and lower latency requirements. This technological shift necessitates architectures capable of handling advanced communication protocols while managing the increased power consumption associated with high-speed wireless connectivity.

Security concerns across all IoT applications are driving demand for architectures that can implement robust hardware-based security features. The increasing frequency of cyber threats targeting IoT infrastructure has made security a primary consideration in architectural decisions, requiring solutions that can provide hardware-level encryption and secure boot capabilities without significantly impacting performance or power consumption.

Edge computing applications represent a particularly significant demand driver, requiring IoT devices capable of local data processing and real-time decision making. These applications necessitate architectures that can handle complex computational tasks while maintaining the low power consumption essential for battery-operated devices. The growing emphasis on artificial intelligence at the edge further amplifies this demand, as devices must accommodate specialized processing units for machine learning inference.

Industrial IoT deployments are increasingly seeking architectures that offer superior reliability and modularity. Manufacturing environments demand devices that can withstand harsh conditions while providing consistent performance over extended operational periods. The ability to customize and upgrade specific components without redesigning entire systems has become a critical requirement, influencing architectural preferences toward solutions that offer greater flexibility.

Consumer IoT markets are driving demand for cost-optimized architectures that can deliver adequate performance while maintaining competitive pricing. Smart home devices, wearables, and connected appliances require architectures that minimize bill-of-materials costs while ensuring reliable connectivity and sufficient processing capabilities for their intended functions.

The proliferation of 5G networks is creating new architectural demands as IoT devices must support higher data throughput and lower latency requirements. This technological shift necessitates architectures capable of handling advanced communication protocols while managing the increased power consumption associated with high-speed wireless connectivity.

Security concerns across all IoT applications are driving demand for architectures that can implement robust hardware-based security features. The increasing frequency of cyber threats targeting IoT infrastructure has made security a primary consideration in architectural decisions, requiring solutions that can provide hardware-level encryption and secure boot capabilities without significantly impacting performance or power consumption.

Current State of MCM and SoC Technologies in IoT

The current landscape of Multi Chip Module (MCM) and System-on-Chip (SoC) technologies in IoT applications presents a complex ecosystem where both architectures serve distinct market segments with varying performance requirements. MCM technology has evolved significantly from its origins in high-performance computing and telecommunications, now finding renewed relevance in IoT applications that demand modular flexibility and rapid time-to-market solutions.

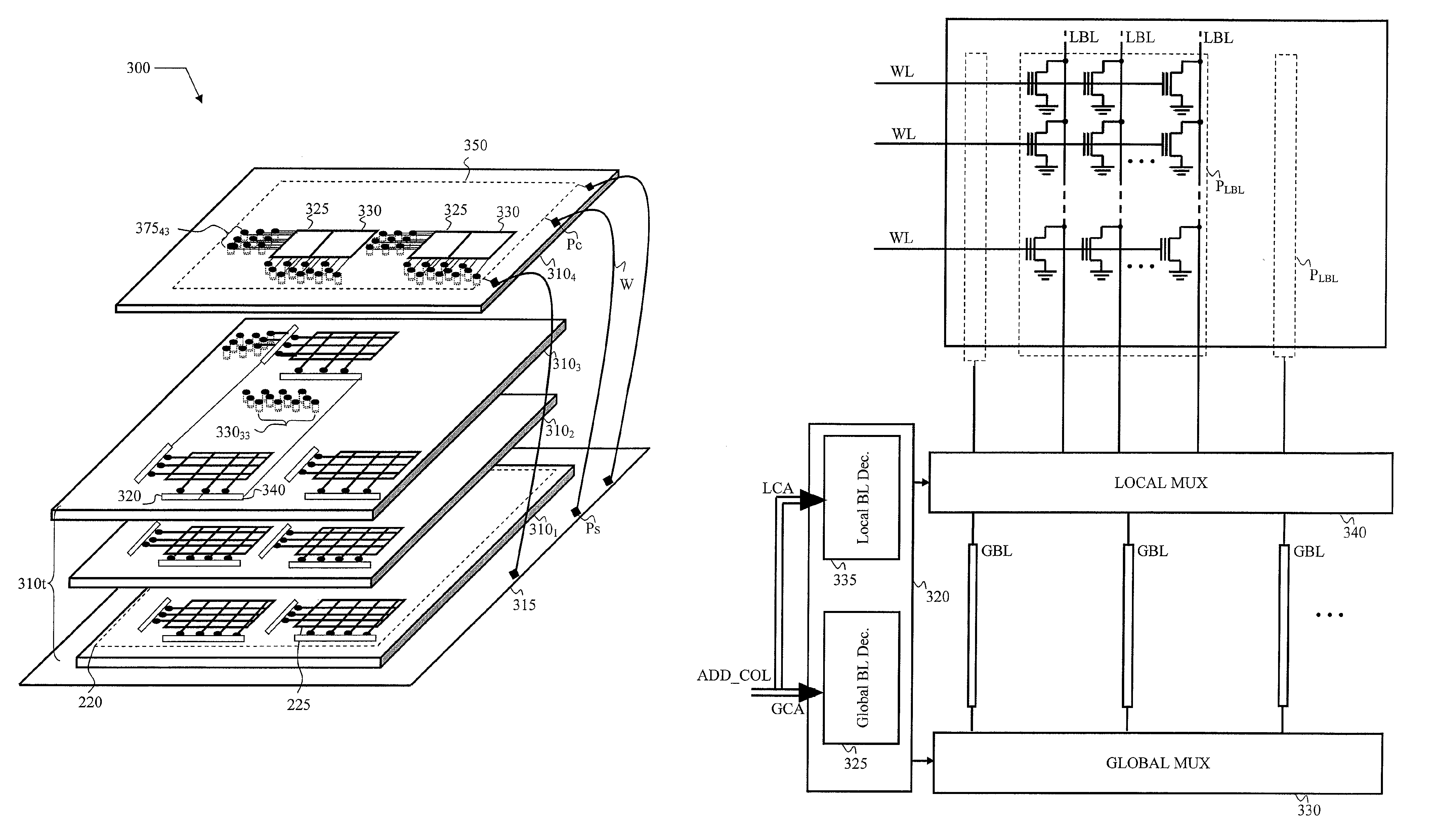

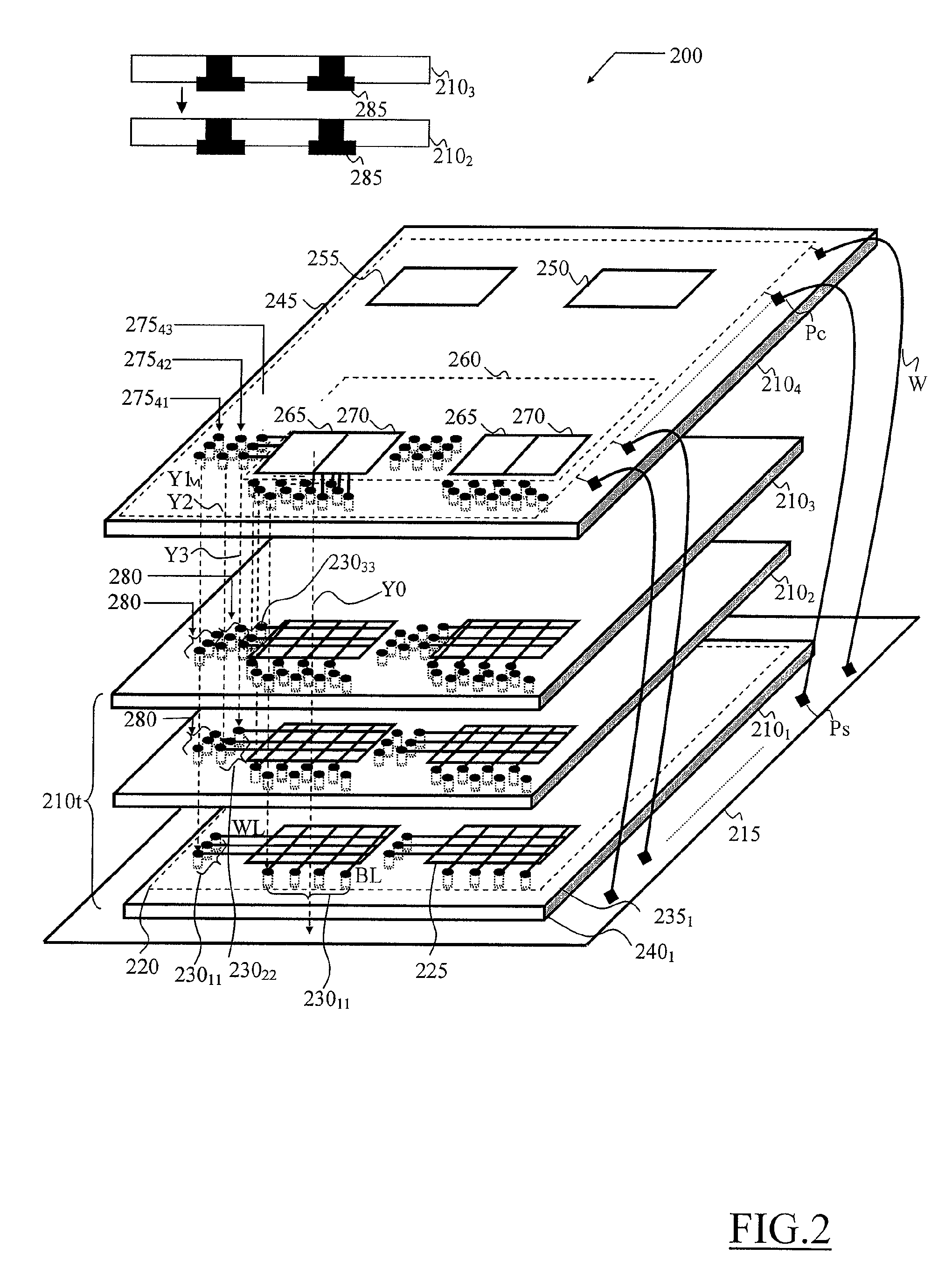

Contemporary MCM implementations in IoT leverage advanced packaging technologies including 2.5D and 3D integration approaches. Leading semiconductor manufacturers have developed sophisticated MCM solutions that combine heterogeneous chiplets on advanced substrates, enabling optimal performance per function while maintaining cost efficiency. These solutions typically integrate specialized processors, memory modules, and connectivity chips within compact form factors suitable for edge computing applications.

SoC technology dominates the mainstream IoT market, with major players delivering highly integrated solutions that combine processing units, memory controllers, wireless connectivity, and peripheral interfaces on single silicon dies. Current SoC architectures for IoT emphasize ultra-low power consumption, with many implementations achieving sub-milliwatt operation in sleep modes while maintaining rapid wake-up capabilities for sensor data processing.

The manufacturing landscape reveals distinct geographical concentrations, with Taiwan and South Korea leading in advanced SoC fabrication capabilities, while MCM assembly and testing operations are distributed across Asia-Pacific regions. European and North American companies focus primarily on design and system integration aspects, leveraging foundry partnerships for production.

Power efficiency remains the primary differentiator between current implementations. Modern IoT SoCs achieve remarkable energy efficiency through process node advantages, typically manufactured on 28nm to 7nm processes, while MCM solutions compensate through selective activation of functional blocks and optimized power management across multiple chips.

Performance scalability represents another critical distinction in current deployments. MCM architectures demonstrate superior adaptability for applications requiring computational scaling, as additional processing elements can be integrated without redesigning the entire system. Conversely, SoC solutions excel in applications with well-defined, stable performance requirements where integration benefits outweigh scalability needs.

Current market adoption patterns show SoC dominance in consumer IoT devices, wearables, and simple sensor nodes, while MCM solutions gain traction in industrial IoT, automotive applications, and edge computing scenarios where performance flexibility and upgrade capabilities provide competitive advantages over fully integrated alternatives.

Contemporary MCM implementations in IoT leverage advanced packaging technologies including 2.5D and 3D integration approaches. Leading semiconductor manufacturers have developed sophisticated MCM solutions that combine heterogeneous chiplets on advanced substrates, enabling optimal performance per function while maintaining cost efficiency. These solutions typically integrate specialized processors, memory modules, and connectivity chips within compact form factors suitable for edge computing applications.

SoC technology dominates the mainstream IoT market, with major players delivering highly integrated solutions that combine processing units, memory controllers, wireless connectivity, and peripheral interfaces on single silicon dies. Current SoC architectures for IoT emphasize ultra-low power consumption, with many implementations achieving sub-milliwatt operation in sleep modes while maintaining rapid wake-up capabilities for sensor data processing.

The manufacturing landscape reveals distinct geographical concentrations, with Taiwan and South Korea leading in advanced SoC fabrication capabilities, while MCM assembly and testing operations are distributed across Asia-Pacific regions. European and North American companies focus primarily on design and system integration aspects, leveraging foundry partnerships for production.

Power efficiency remains the primary differentiator between current implementations. Modern IoT SoCs achieve remarkable energy efficiency through process node advantages, typically manufactured on 28nm to 7nm processes, while MCM solutions compensate through selective activation of functional blocks and optimized power management across multiple chips.

Performance scalability represents another critical distinction in current deployments. MCM architectures demonstrate superior adaptability for applications requiring computational scaling, as additional processing elements can be integrated without redesigning the entire system. Conversely, SoC solutions excel in applications with well-defined, stable performance requirements where integration benefits outweigh scalability needs.

Current market adoption patterns show SoC dominance in consumer IoT devices, wearables, and simple sensor nodes, while MCM solutions gain traction in industrial IoT, automotive applications, and edge computing scenarios where performance flexibility and upgrade capabilities provide competitive advantages over fully integrated alternatives.

Existing MCM and SoC Implementation Strategies

01 Multi-chip module packaging and interconnection technologies

Multi-chip modules utilize advanced packaging techniques to integrate multiple semiconductor chips within a single package. These technologies focus on interconnection methods, substrate designs, and thermal management solutions that enable multiple dies to work together efficiently. The packaging approaches include wire bonding, flip-chip connections, and through-silicon vias to achieve high-density integration while maintaining signal integrity and thermal performance.- Multi-chip module packaging and interconnection technologies: Multi-chip modules utilize advanced packaging techniques to integrate multiple semiconductor chips within a single package. These technologies focus on interconnection methods, substrate designs, and thermal management solutions that enable multiple dies to work together efficiently. The packaging approaches include wire bonding, flip-chip connections, and through-silicon vias to achieve high-density integration while maintaining signal integrity and thermal performance.

- System-on-Chip integration and architecture optimization: System-on-Chip designs integrate multiple functional blocks onto a single semiconductor die, including processors, memory, and peripheral interfaces. These architectures emphasize on-chip communication protocols, power management strategies, and resource sharing mechanisms. The integration approach focuses on optimizing die area utilization, reducing latency through shared buses or network-on-chip architectures, and implementing efficient power domains for different functional units.

- Performance comparison and benchmarking methodologies: Evaluation frameworks for comparing multi-chip modules and system-on-chip solutions involve various performance metrics including processing speed, power consumption, thermal characteristics, and bandwidth capabilities. These methodologies assess factors such as inter-chip communication overhead, memory access latency, and overall system throughput. Testing approaches include standardized benchmarks, real-world application scenarios, and stress testing under different operational conditions.

- Thermal management and power distribution strategies: Thermal and power management solutions address the challenges of heat dissipation and power delivery in both multi-chip modules and system-on-chip designs. These strategies include heat spreader designs, thermal interface materials, power delivery networks, and voltage regulation techniques. The approaches focus on minimizing thermal hotspots, ensuring uniform power distribution, and implementing dynamic power scaling to optimize performance per watt across different operating conditions.

- Signal integrity and high-speed interconnect design: High-speed signal transmission techniques are critical for both multi-chip modules and system-on-chip implementations to maintain data integrity and minimize latency. These designs address impedance matching, crosstalk reduction, electromagnetic interference mitigation, and clock distribution networks. The solutions include differential signaling, equalization techniques, and advanced routing strategies to support high-bandwidth communication while maintaining signal quality across varying distances and frequencies.

02 System-on-Chip integration and architecture optimization

System-on-Chip designs integrate multiple functional blocks onto a single semiconductor substrate, optimizing performance through on-chip communication and reduced latency. These architectures employ various techniques for power management, clock distribution, and resource sharing to maximize computational efficiency. The integration approach focuses on minimizing interconnect delays and power consumption while maximizing processing capabilities within a unified silicon platform.Expand Specific Solutions03 Performance comparison and benchmarking methodologies

Evaluation frameworks and testing methodologies are employed to compare the performance characteristics between different integration approaches. These methods assess parameters such as processing speed, power efficiency, thermal characteristics, and signal propagation delays. Benchmarking techniques include standardized test protocols, simulation models, and real-world application scenarios to provide comprehensive performance metrics.Expand Specific Solutions04 Thermal management and power distribution solutions

Advanced thermal management techniques address heat dissipation challenges in high-density integrated circuits. These solutions include heat spreaders, thermal interface materials, and power delivery networks optimized for different integration architectures. The approaches consider thermal coupling effects, hotspot management, and dynamic power allocation to maintain optimal operating temperatures and ensure reliable performance across various workload conditions.Expand Specific Solutions05 Heterogeneous integration and chiplet architectures

Emerging integration strategies combine multiple specialized processing elements using chiplet-based designs and heterogeneous integration techniques. These approaches enable mixing different process technologies, functional blocks, and semiconductor materials within a single system. The architectures support modular design methodologies, allowing for flexible configuration and scalability while balancing performance, cost, and time-to-market considerations.Expand Specific Solutions

Key Players in MCM and SoC IoT Market

The Multi Chip Module versus SoC debate in IoT devices represents a rapidly evolving competitive landscape in the mature semiconductor industry. The market, valued at billions globally, is experiencing significant growth driven by IoT proliferation. Technology maturity varies considerably across players, with established leaders like Apple, Qualcomm, and Intel demonstrating advanced SoC capabilities for integrated solutions, while Texas Instruments and Analog Devices excel in specialized MCM applications. Samsung Electronics and TSMC provide critical manufacturing infrastructure, enabling both approaches. Emerging players like SMIC-Beijing and Datang Semiconductor are advancing rapidly in foundry services. The competitive dynamics show SoC solutions gaining traction for power-constrained IoT applications, while MCM approaches remain viable for specialized, high-performance requirements where modularity and customization are prioritized over integration.

Texas Instruments Incorporated

Technical Solution: Texas Instruments focuses primarily on SoC solutions for IoT applications, developing highly integrated microcontrollers and wireless connectivity solutions that combine processing, memory, and radio functions on single chips. Their SimpleLink platform offers SoC designs with integrated Wi-Fi, Bluetooth, and sub-GHz connectivity, optimized for ultra-low power consumption with sleep currents below 1µA. TI's approach emphasizes ease of development and deployment, providing comprehensive software stacks and development tools that reduce time-to-market for IoT device manufacturers while maintaining cost-effective single-chip solutions.

Strengths: Ultra-low power consumption and comprehensive development ecosystem. Weaknesses: Limited processing power for complex AI and edge computing applications.

QUALCOMM, Inc.

Technical Solution: Qualcomm develops advanced SoC solutions specifically optimized for IoT applications, featuring integrated connectivity modules including Wi-Fi, Bluetooth, and cellular capabilities within single chip designs. Their Snapdragon IoT platforms utilize heterogeneous computing architectures combining ARM Cortex processors with dedicated DSPs and AI accelerators, achieving power efficiency improvements of up to 40% compared to discrete multi-chip implementations. The company's SoC approach enables smaller form factors and reduced bill of materials costs while maintaining robust performance for edge computing tasks in IoT devices.

Strengths: Integrated connectivity reduces power consumption and board space requirements. Weaknesses: Limited flexibility for customization compared to modular MCM approaches.

Core Innovations in IoT Chip Architecture Design

Multi chip electronic system

PatentActiveUS8228684B2

Innovation

- Separating sub-systems and integrating service circuit structures on dedicated chips shared by multiple ICs, while using more advanced lithographic apparatuses for functional circuit cores, and less expensive ones for service circuit structures.

SoC Dual Processor Architecture for Internet of Things

PatentInactiveKR1020180025114A

Innovation

- A dual-processor system-on-chip architecture with an 8-bit microcontroller for general sensing and driving functions, a 32-bit microprocessor for complex calculations, and multiple buses with synchronization units, supporting high-speed data transmission and encryption for image processing and sensor data, including a lightweight encryption algorithm and image compression up to 5 megapixels at 5 frames per second.

Power Efficiency Standards for IoT Devices

Power efficiency standards for IoT devices have become increasingly critical as the industry grapples with the fundamental architectural choice between Multi Chip Module (MCM) and System-on-Chip (SoC) implementations. The IEEE 802.11ah standard specifically addresses ultra-low power WiFi for IoT applications, establishing baseline power consumption metrics that directly influence MCM versus SoC design decisions. These standards mandate sleep mode power consumption below 10 microamperes and active mode efficiency targets that favor integrated solutions.

The Energy Star IoT Device Specification, introduced in 2019, sets comprehensive power efficiency benchmarks that significantly impact architectural choices. SoC implementations typically demonstrate superior compliance with these standards due to reduced inter-chip communication overhead and optimized power management integration. The specification requires devices to achieve specific performance-per-watt ratios, where SoCs generally outperform MCM configurations by 15-25% in standardized testing scenarios.

International standards bodies including IEC 62430 and ISO/IEC 30071 have established power measurement methodologies that reveal distinct advantages for each architecture. MCM designs excel in meeting standards for modular power scaling, allowing selective component activation that can achieve ultra-low standby power states. Conversely, SoC architectures demonstrate superior performance against continuous operation efficiency standards due to integrated voltage regulation and clock domain optimization.

The Thread Group's power efficiency specifications for mesh networking applications present unique challenges for both architectures. MCM implementations can leverage specialized low-power radio chips that exceed standard requirements, while SoC solutions benefit from integrated protocol stack optimization. Recent amendments to these standards emphasize dynamic power scaling capabilities, where SoCs demonstrate measurable advantages in transition speed and efficiency.

Emerging standards from the LoRa Alliance and Sigfox consortium are reshaping power efficiency requirements for wide-area IoT applications. These specifications favor architectures capable of achieving sub-microamp sleep currents while maintaining rapid wake-up capabilities. SoC implementations increasingly dominate compliance testing due to integrated power management units and optimized silicon processes, though specialized MCM configurations continue to meet niche ultra-low power requirements in specific deployment scenarios.

The Energy Star IoT Device Specification, introduced in 2019, sets comprehensive power efficiency benchmarks that significantly impact architectural choices. SoC implementations typically demonstrate superior compliance with these standards due to reduced inter-chip communication overhead and optimized power management integration. The specification requires devices to achieve specific performance-per-watt ratios, where SoCs generally outperform MCM configurations by 15-25% in standardized testing scenarios.

International standards bodies including IEC 62430 and ISO/IEC 30071 have established power measurement methodologies that reveal distinct advantages for each architecture. MCM designs excel in meeting standards for modular power scaling, allowing selective component activation that can achieve ultra-low standby power states. Conversely, SoC architectures demonstrate superior performance against continuous operation efficiency standards due to integrated voltage regulation and clock domain optimization.

The Thread Group's power efficiency specifications for mesh networking applications present unique challenges for both architectures. MCM implementations can leverage specialized low-power radio chips that exceed standard requirements, while SoC solutions benefit from integrated protocol stack optimization. Recent amendments to these standards emphasize dynamic power scaling capabilities, where SoCs demonstrate measurable advantages in transition speed and efficiency.

Emerging standards from the LoRa Alliance and Sigfox consortium are reshaping power efficiency requirements for wide-area IoT applications. These specifications favor architectures capable of achieving sub-microamp sleep currents while maintaining rapid wake-up capabilities. SoC implementations increasingly dominate compliance testing due to integrated power management units and optimized silicon processes, though specialized MCM configurations continue to meet niche ultra-low power requirements in specific deployment scenarios.

Cost-Performance Trade-offs in IoT Chip Selection

The selection between Multi Chip Module (MCM) and System-on-Chip (SoC) architectures in IoT devices fundamentally revolves around balancing cost constraints with performance requirements. This decision significantly impacts both initial development investments and long-term operational economics, making it crucial for IoT manufacturers to understand the financial implications of each approach.

SoC solutions typically demonstrate superior cost-performance ratios in high-volume IoT deployments. The integration of multiple functions onto a single silicon die reduces manufacturing costs, minimizes board space requirements, and decreases assembly complexity. For consumer IoT devices targeting millions of units annually, the economies of scale associated with SoC production can drive per-unit costs below $5, while delivering adequate processing power for basic sensing and connectivity functions.

MCM architectures present a different cost-performance proposition, particularly advantageous for specialized or low-volume IoT applications. While initial component costs may be 20-40% higher than equivalent SoC solutions, MCMs offer superior flexibility in component selection and upgrade paths. This modularity allows manufacturers to optimize individual subsystems independently, potentially achieving better performance-per-dollar ratios in specific use cases such as industrial monitoring or medical devices.

Power consumption considerations significantly influence the total cost of ownership in battery-powered IoT devices. SoC designs generally exhibit lower power consumption due to reduced interconnect losses and optimized power management integration. This efficiency translates to extended battery life, reducing maintenance costs and improving user experience. MCM solutions may consume 15-25% more power, impacting operational costs over the device lifecycle.

Development and time-to-market factors also affect the cost-performance equation. SoC development requires substantial upfront investment, often exceeding $10 million for advanced process nodes, making it viable only for high-volume applications. MCM approaches leverage existing components, reducing development costs and accelerating market entry, particularly valuable for niche IoT markets where speed and customization outweigh volume economics.

The manufacturing yield and reliability aspects further influence cost considerations. SoC production faces yield challenges as chip complexity increases, potentially driving costs higher for advanced features. MCM solutions distribute risk across multiple components, often achieving better overall yield rates and more predictable cost structures, especially important for mission-critical IoT applications where reliability justifies premium pricing.

SoC solutions typically demonstrate superior cost-performance ratios in high-volume IoT deployments. The integration of multiple functions onto a single silicon die reduces manufacturing costs, minimizes board space requirements, and decreases assembly complexity. For consumer IoT devices targeting millions of units annually, the economies of scale associated with SoC production can drive per-unit costs below $5, while delivering adequate processing power for basic sensing and connectivity functions.

MCM architectures present a different cost-performance proposition, particularly advantageous for specialized or low-volume IoT applications. While initial component costs may be 20-40% higher than equivalent SoC solutions, MCMs offer superior flexibility in component selection and upgrade paths. This modularity allows manufacturers to optimize individual subsystems independently, potentially achieving better performance-per-dollar ratios in specific use cases such as industrial monitoring or medical devices.

Power consumption considerations significantly influence the total cost of ownership in battery-powered IoT devices. SoC designs generally exhibit lower power consumption due to reduced interconnect losses and optimized power management integration. This efficiency translates to extended battery life, reducing maintenance costs and improving user experience. MCM solutions may consume 15-25% more power, impacting operational costs over the device lifecycle.

Development and time-to-market factors also affect the cost-performance equation. SoC development requires substantial upfront investment, often exceeding $10 million for advanced process nodes, making it viable only for high-volume applications. MCM approaches leverage existing components, reducing development costs and accelerating market entry, particularly valuable for niche IoT markets where speed and customization outweigh volume economics.

The manufacturing yield and reliability aspects further influence cost considerations. SoC production faces yield challenges as chip complexity increases, potentially driving costs higher for advanced features. MCM solutions distribute risk across multiple components, often achieving better overall yield rates and more predictable cost structures, especially important for mission-critical IoT applications where reliability justifies premium pricing.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!