Optimize Wafer Bonding for High-Conductivity Materials

APR 13, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Wafer Bonding Technology Background and Objectives

Wafer bonding technology has emerged as a fundamental process in semiconductor manufacturing, enabling the integration of different materials and functionalities within a single device structure. The technique involves joining two or more wafer surfaces at the atomic level to create permanent bonds, facilitating the development of advanced electronic devices, sensors, and microelectromechanical systems. This process has become increasingly critical as the semiconductor industry pushes toward more complex three-dimensional architectures and heterogeneous integration approaches.

The evolution of wafer bonding can be traced back to the 1980s when silicon-on-insulator structures first demonstrated the potential for improved device performance through substrate engineering. Early implementations focused primarily on silicon-to-silicon bonding using thermal oxidation and high-temperature annealing processes. However, as device requirements became more sophisticated, the need for bonding dissimilar materials, particularly high-conductivity materials such as copper, silver, and various metal alloys, became apparent.

High-conductivity materials present unique challenges in wafer bonding applications due to their distinct thermal expansion coefficients, surface oxidation tendencies, and chemical reactivity. Traditional bonding methods often result in interface defects, thermal stress accumulation, and compromised electrical performance when applied to these materials. The mismatch in material properties can lead to delamination, void formation, and reduced bond strength, significantly impacting device reliability and yield.

Current technological objectives focus on developing optimized bonding processes that can accommodate the specific requirements of high-conductivity materials while maintaining excellent electrical and mechanical properties. Key goals include achieving low-temperature bonding to minimize thermal stress, ensuring uniform bond interfaces with minimal void density, and maintaining the inherent electrical characteristics of the high-conductivity materials throughout the bonding process.

The primary technical targets encompass reducing bonding temperatures below 400°C to prevent excessive thermal expansion mismatch, achieving bond strengths exceeding 10 MPa for mechanical reliability, and maintaining electrical resistivity within 10% of bulk material values. Additionally, the development of surface preparation techniques that promote strong adhesion while preserving material integrity represents a critical objective for advancing this technology in next-generation semiconductor applications.

The evolution of wafer bonding can be traced back to the 1980s when silicon-on-insulator structures first demonstrated the potential for improved device performance through substrate engineering. Early implementations focused primarily on silicon-to-silicon bonding using thermal oxidation and high-temperature annealing processes. However, as device requirements became more sophisticated, the need for bonding dissimilar materials, particularly high-conductivity materials such as copper, silver, and various metal alloys, became apparent.

High-conductivity materials present unique challenges in wafer bonding applications due to their distinct thermal expansion coefficients, surface oxidation tendencies, and chemical reactivity. Traditional bonding methods often result in interface defects, thermal stress accumulation, and compromised electrical performance when applied to these materials. The mismatch in material properties can lead to delamination, void formation, and reduced bond strength, significantly impacting device reliability and yield.

Current technological objectives focus on developing optimized bonding processes that can accommodate the specific requirements of high-conductivity materials while maintaining excellent electrical and mechanical properties. Key goals include achieving low-temperature bonding to minimize thermal stress, ensuring uniform bond interfaces with minimal void density, and maintaining the inherent electrical characteristics of the high-conductivity materials throughout the bonding process.

The primary technical targets encompass reducing bonding temperatures below 400°C to prevent excessive thermal expansion mismatch, achieving bond strengths exceeding 10 MPa for mechanical reliability, and maintaining electrical resistivity within 10% of bulk material values. Additionally, the development of surface preparation techniques that promote strong adhesion while preserving material integrity represents a critical objective for advancing this technology in next-generation semiconductor applications.

Market Demand for High-Conductivity Wafer Applications

The semiconductor industry is experiencing unprecedented demand for high-conductivity wafer applications, driven by the rapid expansion of power electronics, electric vehicles, and renewable energy systems. Silicon carbide and gallium nitride wafers have emerged as critical components in power conversion devices, where superior thermal conductivity and electrical performance are essential for efficient energy management.

Electric vehicle manufacturers are increasingly adopting wide-bandgap semiconductors to improve inverter efficiency and reduce system weight. The automotive sector's transition toward electrification has created substantial demand for high-conductivity wafer bonding solutions that can withstand extreme operating conditions while maintaining reliable electrical connections. Power modules in electric drivetrains require robust wafer bonding techniques to ensure long-term performance under high current densities and thermal cycling.

Data center infrastructure represents another significant growth driver, as cloud computing and artificial intelligence applications demand more efficient power management solutions. High-conductivity bonded wafers enable the development of advanced power supplies and voltage regulators that can handle increasing computational loads while minimizing energy losses. The proliferation of edge computing and 5G networks further amplifies this demand.

Renewable energy systems, particularly solar inverters and wind power converters, rely heavily on optimized wafer bonding for high-conductivity materials. These applications require exceptional reliability over decades of operation, making advanced bonding techniques crucial for maintaining electrical integrity and thermal performance. The global push toward carbon neutrality has accelerated investment in renewable infrastructure, directly impacting wafer bonding technology requirements.

Industrial automation and motor drive applications continue to expand the market for high-conductivity wafer solutions. Manufacturing facilities increasingly deploy variable frequency drives and servo systems that benefit from improved power semiconductor performance. The Industrial Internet of Things revolution has created additional demand for efficient power conversion in distributed sensing and control systems.

Consumer electronics markets are also driving innovation in wafer bonding technologies, particularly for fast-charging systems and wireless power transfer applications. Smartphone manufacturers and electric appliance producers seek compact, efficient power management solutions that leverage advanced semiconductor materials and bonding techniques to achieve superior performance in smaller form factors.

Electric vehicle manufacturers are increasingly adopting wide-bandgap semiconductors to improve inverter efficiency and reduce system weight. The automotive sector's transition toward electrification has created substantial demand for high-conductivity wafer bonding solutions that can withstand extreme operating conditions while maintaining reliable electrical connections. Power modules in electric drivetrains require robust wafer bonding techniques to ensure long-term performance under high current densities and thermal cycling.

Data center infrastructure represents another significant growth driver, as cloud computing and artificial intelligence applications demand more efficient power management solutions. High-conductivity bonded wafers enable the development of advanced power supplies and voltage regulators that can handle increasing computational loads while minimizing energy losses. The proliferation of edge computing and 5G networks further amplifies this demand.

Renewable energy systems, particularly solar inverters and wind power converters, rely heavily on optimized wafer bonding for high-conductivity materials. These applications require exceptional reliability over decades of operation, making advanced bonding techniques crucial for maintaining electrical integrity and thermal performance. The global push toward carbon neutrality has accelerated investment in renewable infrastructure, directly impacting wafer bonding technology requirements.

Industrial automation and motor drive applications continue to expand the market for high-conductivity wafer solutions. Manufacturing facilities increasingly deploy variable frequency drives and servo systems that benefit from improved power semiconductor performance. The Industrial Internet of Things revolution has created additional demand for efficient power conversion in distributed sensing and control systems.

Consumer electronics markets are also driving innovation in wafer bonding technologies, particularly for fast-charging systems and wireless power transfer applications. Smartphone manufacturers and electric appliance producers seek compact, efficient power management solutions that leverage advanced semiconductor materials and bonding techniques to achieve superior performance in smaller form factors.

Current Challenges in High-Conductivity Wafer Bonding

High-conductivity wafer bonding faces significant thermal management challenges due to the inherent properties of conductive materials. During the bonding process, these materials exhibit rapid heat dissipation and non-uniform temperature distribution, making it difficult to achieve the precise thermal profiles required for successful bonding. The high thermal conductivity can lead to premature cooling in critical bonding zones, resulting in incomplete interface formation and compromised bond strength.

Surface preparation represents another critical challenge, as high-conductivity materials often develop native oxide layers or surface contamination that impede proper bonding. Copper and silver-based materials, commonly used for their excellent electrical properties, are particularly susceptible to oxidation and require specialized cleaning protocols. Traditional surface activation methods may prove insufficient, necessitating advanced plasma treatments or chemical mechanical polishing techniques that can damage the underlying conductive layers.

Interface compatibility issues arise when bonding dissimilar high-conductivity materials with varying thermal expansion coefficients. The mismatch in thermal properties can generate significant stress concentrations during temperature cycling, leading to delamination or crack propagation at the bonding interface. This challenge is particularly pronounced in heterogeneous integration applications where different conductive materials must be reliably joined.

Process parameter optimization presents substantial difficulties due to the narrow processing windows typical of high-conductivity materials. The bonding temperature, pressure, and time parameters must be precisely controlled to prevent material degradation while ensuring adequate bond formation. Excessive temperatures can cause grain growth or phase transformations in the conductive layers, while insufficient thermal input results in weak bonding interfaces.

Contamination control becomes increasingly critical when working with high-conductivity materials, as even trace amounts of impurities can significantly impact both electrical and mechanical properties. Outgassing from organic residues or moisture absorption can create voids or weak spots in the bonded interface, compromising the overall reliability of the assembly.

Quality assessment and characterization of bonded high-conductivity wafers present unique challenges, as traditional non-destructive testing methods may not adequately detect defects in these materials. The high electrical conductivity can interfere with conventional inspection techniques, requiring specialized metrology approaches to ensure bond quality and reliability.

Surface preparation represents another critical challenge, as high-conductivity materials often develop native oxide layers or surface contamination that impede proper bonding. Copper and silver-based materials, commonly used for their excellent electrical properties, are particularly susceptible to oxidation and require specialized cleaning protocols. Traditional surface activation methods may prove insufficient, necessitating advanced plasma treatments or chemical mechanical polishing techniques that can damage the underlying conductive layers.

Interface compatibility issues arise when bonding dissimilar high-conductivity materials with varying thermal expansion coefficients. The mismatch in thermal properties can generate significant stress concentrations during temperature cycling, leading to delamination or crack propagation at the bonding interface. This challenge is particularly pronounced in heterogeneous integration applications where different conductive materials must be reliably joined.

Process parameter optimization presents substantial difficulties due to the narrow processing windows typical of high-conductivity materials. The bonding temperature, pressure, and time parameters must be precisely controlled to prevent material degradation while ensuring adequate bond formation. Excessive temperatures can cause grain growth or phase transformations in the conductive layers, while insufficient thermal input results in weak bonding interfaces.

Contamination control becomes increasingly critical when working with high-conductivity materials, as even trace amounts of impurities can significantly impact both electrical and mechanical properties. Outgassing from organic residues or moisture absorption can create voids or weak spots in the bonded interface, compromising the overall reliability of the assembly.

Quality assessment and characterization of bonded high-conductivity wafers present unique challenges, as traditional non-destructive testing methods may not adequately detect defects in these materials. The high electrical conductivity can interfere with conventional inspection techniques, requiring specialized metrology approaches to ensure bond quality and reliability.

Existing High-Conductivity Wafer Bonding Solutions

01 Conductive bonding layers and adhesive materials

Wafer bonding conductivity can be enhanced through the use of specialized conductive bonding layers and adhesive materials. These materials facilitate electrical connection between bonded wafers while maintaining mechanical stability. Conductive adhesives, metal layers, or doped polymer materials can be applied at the bonding interface to create low-resistance electrical pathways. The selection of appropriate bonding materials with suitable conductivity properties is critical for achieving reliable electrical interconnection in bonded wafer structures.- Conductive bonding layers and adhesive materials: Wafer bonding conductivity can be enhanced through the use of specialized conductive bonding layers and adhesive materials. These materials facilitate electrical connection between bonded wafers while maintaining mechanical stability. Conductive adhesives, metal layers, or doped polymer materials can be applied at the bonding interface to create low-resistance electrical pathways. The selection of appropriate bonding materials with suitable conductivity properties is critical for achieving reliable electrical interconnection in bonded wafer structures.

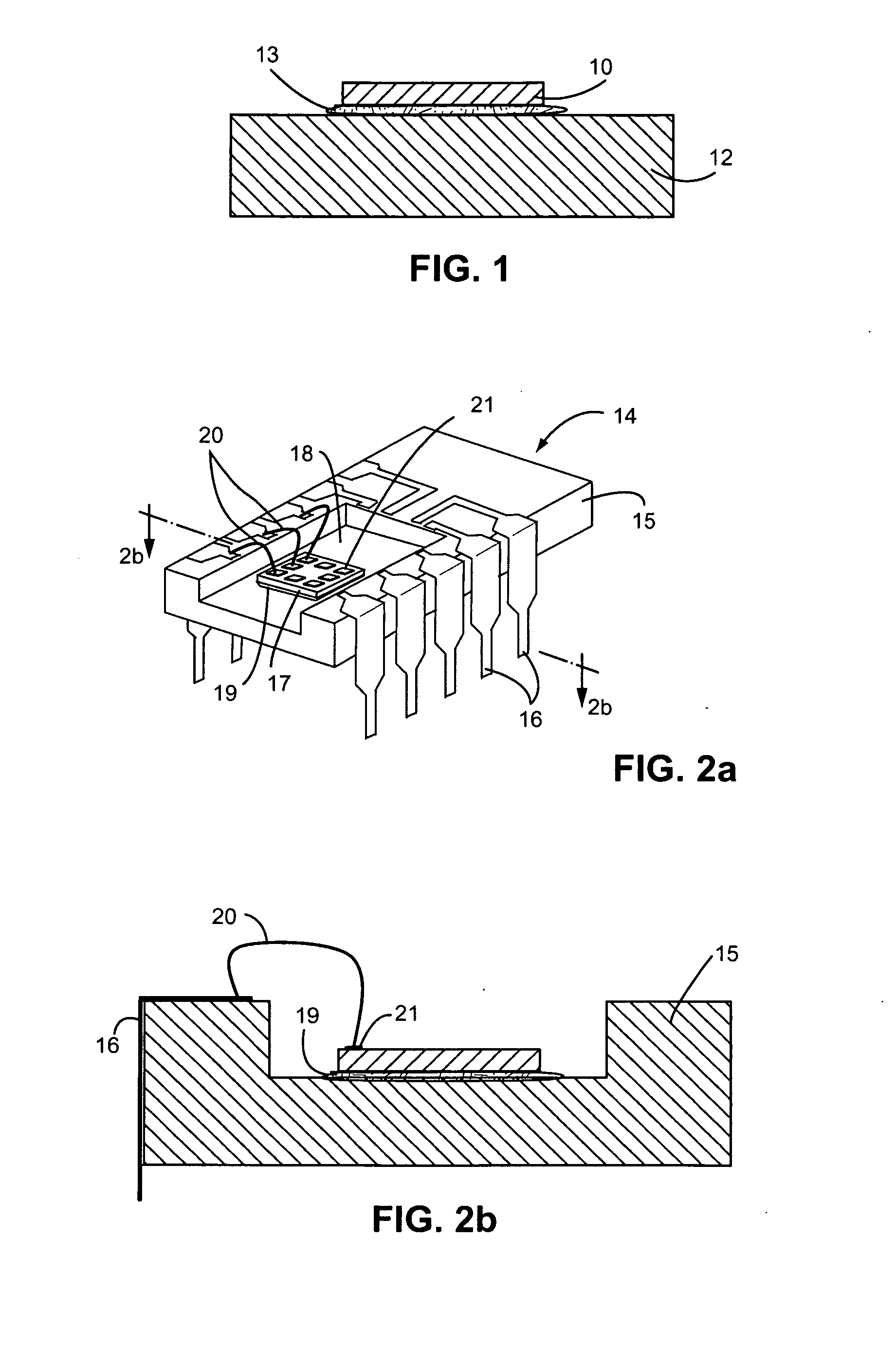

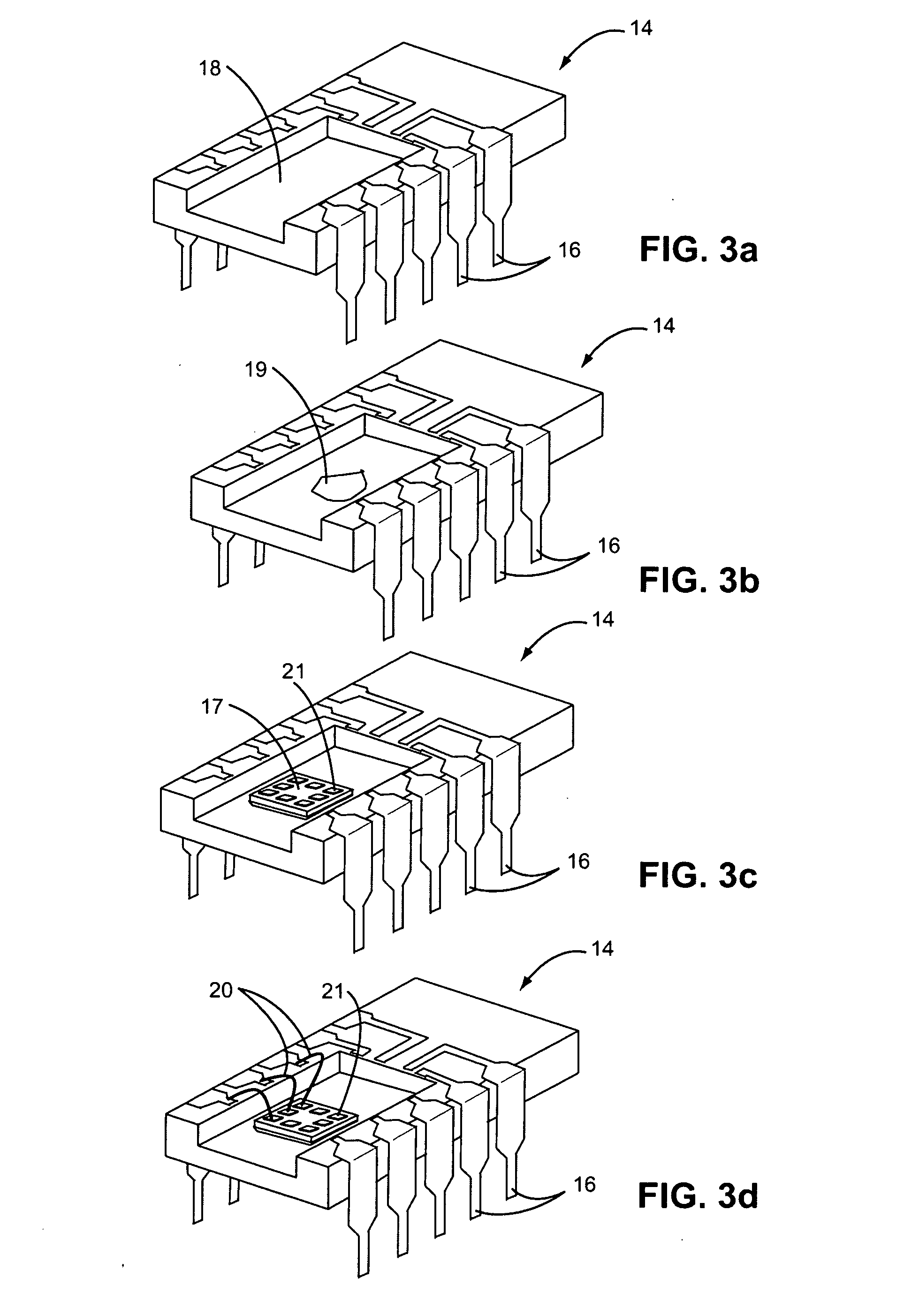

- Metal-to-metal bonding techniques: Direct metal-to-metal bonding provides excellent electrical conductivity across bonded wafer interfaces. This approach involves depositing metal layers on wafer surfaces and bonding them through thermocompression, diffusion bonding, or eutectic bonding processes. The metal layers serve dual purposes of providing mechanical bonding strength and establishing electrical conductivity. Various metal combinations and bonding parameters can be optimized to achieve desired conductivity levels while ensuring bond integrity and reliability.

- Through-silicon vias (TSV) integration: Through-silicon vias enable vertical electrical interconnection in bonded wafer stacks, significantly improving conductivity and signal transmission. These conductive pathways penetrate through the silicon substrate, connecting different layers in three-dimensional integrated structures. The TSV formation process involves etching, insulation deposition, and conductive material filling. Proper TSV design and fabrication are essential for achieving low-resistance electrical paths and maintaining signal integrity in multi-wafer bonded assemblies.

- Surface treatment and activation methods: Surface preparation and activation techniques play a crucial role in enhancing wafer bonding conductivity. These methods include plasma treatment, chemical cleaning, and surface roughening to improve contact quality and reduce interface resistance. Proper surface activation removes contaminants and oxides that can impede electrical conduction. Additionally, controlled surface modification can promote better adhesion and create more conductive bonding interfaces, leading to improved overall electrical performance of bonded wafer structures.

- Annealing and post-bonding processes: Post-bonding thermal treatments and annealing processes are employed to enhance conductivity at wafer bonding interfaces. These processes promote interdiffusion of materials, reduce interface defects, and improve electrical contact quality. Controlled annealing at specific temperatures and atmospheres can optimize the microstructure of bonding layers, resulting in lower contact resistance and better electrical performance. The annealing parameters must be carefully selected to achieve desired conductivity improvements without compromising the mechanical integrity of the bonded structure.

02 Metal-to-metal bonding techniques

Direct metal-to-metal bonding provides excellent electrical conductivity across bonded wafer interfaces. This approach involves depositing metal layers on wafer surfaces and bonding them through thermocompression, diffusion bonding, or eutectic bonding processes. The metal layers serve dual purposes of providing mechanical bonding strength and establishing electrical conductivity. Various metal combinations and bonding parameters can be optimized to achieve desired conductivity levels while ensuring bond integrity and reliability.Expand Specific Solutions03 Through-silicon vias (TSV) integration with wafer bonding

Through-silicon vias combined with wafer bonding enable vertical electrical interconnection in three-dimensional integrated circuits. This technology involves creating conductive pathways through the silicon substrate that connect to bonding interfaces, allowing electrical signals to pass between stacked wafers. The TSV structures are filled with conductive materials and integrated with wafer bonding processes to establish reliable electrical connections. Proper design and fabrication of TSVs are essential for maintaining low resistance and high conductivity in bonded wafer assemblies.Expand Specific Solutions04 Surface treatment and activation for conductive bonding

Surface preparation and activation techniques significantly impact the electrical conductivity of bonded wafer interfaces. Various surface treatment methods including plasma activation, chemical cleaning, and surface roughening can be employed to enhance bonding quality and electrical contact. These treatments remove contaminants, modify surface properties, and create favorable conditions for establishing low-resistance electrical connections. Proper surface preparation ensures intimate contact between bonding surfaces and minimizes interface resistance.Expand Specific Solutions05 Hybrid bonding with electrical interconnection

Hybrid bonding techniques combine dielectric bonding with embedded metal interconnects to achieve simultaneous mechanical and electrical connection. This approach involves patterning metal features within dielectric layers on wafer surfaces, followed by bonding processes that create both dielectric-to-dielectric and metal-to-metal bonds. The resulting structure provides high-density electrical interconnections with excellent conductivity while maintaining strong mechanical bonding. Hybrid bonding is particularly suitable for advanced packaging applications requiring fine-pitch interconnections and high electrical performance.Expand Specific Solutions

Key Players in Semiconductor Wafer Bonding Industry

The wafer bonding optimization for high-conductivity materials represents a rapidly evolving sector within the advanced semiconductor packaging industry, currently in its growth phase with significant technological momentum. The market demonstrates substantial scale potential, driven by increasing demand for 3D integration and advanced packaging solutions across memory, logic, and sensor applications. Technology maturity varies considerably among key players, with established foundries like Taiwan Semiconductor Manufacturing Co. and Samsung Electronics leading in production-scale implementation, while Chinese manufacturers including Yangtze Memory Technologies, SMIC, and Hua Hong Semiconductor are aggressively advancing their capabilities. Specialized equipment providers such as Tokyo Electron and Suss MicroTec Lithography offer critical enabling technologies, while materials companies like Sumitomo Bakelite and Brewer Science provide essential bonding materials. Research institutions including University of California and Industrial Technology Research Institute contribute fundamental innovations, creating a competitive landscape characterized by both technological differentiation and rapid capability development across the value chain.

Suss MicroTec Lithography GmbH

Technical Solution: Suss MicroTec provides specialized equipment and processes for wafer bonding applications involving high-conductivity materials. Their bonding systems feature advanced temperature and pressure control with precision alignment capabilities for achieving optimal electrical connections. The company's technology includes plasma activation systems that enhance surface reactivity for improved bonding of conductive materials like copper and gold. Their process chambers incorporate controlled atmosphere capabilities to prevent oxidation during bonding of reactive metals. Suss MicroTec's solutions include both temporary and permanent bonding options with specialized release mechanisms for temporary applications. Their equipment supports various bonding techniques including thermocompression, fusion, and adhesive bonding optimized for different conductivity requirements. The company provides comprehensive process development services to optimize bonding parameters for specific material combinations and application requirements.

Strengths: Specialized equipment expertise and comprehensive process support, flexible solutions for various bonding applications. Weaknesses: Equipment-focused rather than materials innovation, smaller scale compared to major semiconductor manufacturers.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced wafer bonding technologies for high-conductivity materials as part of their 3D IC integration and advanced packaging solutions. Their CoWoS (Chip on Wafer on Substrate) and InFO (Integrated Fan-Out) technologies incorporate sophisticated wafer bonding processes optimized for copper and other high-conductivity materials. TSMC's approach utilizes plasma-activated bonding combined with precise surface preparation techniques to achieve low-resistance interconnects. Their process includes advanced surface cleaning, activation, and controlled atmosphere bonding to minimize oxidation and contamination. The company has implemented temperature-controlled bonding chambers with real-time monitoring systems to ensure consistent bond quality across large wafer areas. Their technology supports both temporary and permanent bonding applications with excellent thermal and electrical performance.

Strengths: Massive manufacturing scale and advanced process control, extensive R&D resources and industry partnerships. Weaknesses: High cost structure, complex qualification processes for new technologies.

Core Innovations in Conductive Material Bonding Patents

Low-temperature wafer bonding of semiconductor substrates to metal substrates

PatentActiveUS20090286382A1

Innovation

- A method for direct bonding of semiconductor and metal substrates without intermediate layers, using techniques such as plasma exposure, low-temperature annealing, and the application of thin metal films like Palladium to achieve low electrical and thermal resistance interfaces, allowing for low-temperature bonding and enhanced reliability.

Semiconductor structure, semiconductor device, electronic device, and wafer bonding method

PatentWO2024109459A1

Innovation

- A method is adopted that includes forming a metal bonding layer and an insulating bonding layer on two wafers, and introducing an insulating compound to the auxiliary bonding layer. The auxiliary bonding layer is reduced to a conductive layer through heat treatment to achieve high-strength bonding. .

Semiconductor Manufacturing Equipment Standards

The semiconductor manufacturing industry operates under a comprehensive framework of equipment standards that directly impact wafer bonding processes for high-conductivity materials. These standards encompass multiple dimensions including equipment design specifications, operational parameters, safety protocols, and quality assurance requirements that manufacturers must adhere to when developing and deploying bonding systems.

International standards organizations such as SEMI (Semiconductor Equipment and Materials International) have established critical guidelines for wafer bonding equipment, particularly focusing on thermal management, pressure control, and environmental conditions. The SEMI E10 standard for safety guidelines and SEMI E84 for mechanical interfaces are fundamental requirements that bonding equipment must meet. Additionally, ISO 14644 cleanroom standards define the environmental conditions necessary for contamination-free bonding processes.

Equipment certification processes require rigorous testing and validation procedures to ensure consistent performance across different operational scenarios. For high-conductivity material bonding, specific standards address temperature uniformity requirements, typically mandating variations within ±2°C across the wafer surface, and pressure distribution tolerances that must remain within ±5% of target values. These specifications are critical for achieving reliable electrical connections in advanced semiconductor devices.

Metrology and inspection standards play a crucial role in validating bonding quality and equipment performance. Standards such as ASTM F1530 for measuring wafer bow and warp, and SEMI MF1811 for particle contamination assessment, provide frameworks for evaluating bonding outcomes. These measurement protocols ensure that equipment consistently produces bonds meeting electrical conductivity and mechanical strength requirements.

Emerging standards are being developed to address next-generation bonding technologies, including hybrid bonding and direct copper-to-copper bonding techniques. These evolving standards focus on sub-micron alignment accuracy, surface preparation requirements, and post-bonding annealing protocols. Equipment manufacturers must anticipate these developing standards to ensure their systems remain compliant with future industry requirements while maintaining compatibility with existing production environments.

International standards organizations such as SEMI (Semiconductor Equipment and Materials International) have established critical guidelines for wafer bonding equipment, particularly focusing on thermal management, pressure control, and environmental conditions. The SEMI E10 standard for safety guidelines and SEMI E84 for mechanical interfaces are fundamental requirements that bonding equipment must meet. Additionally, ISO 14644 cleanroom standards define the environmental conditions necessary for contamination-free bonding processes.

Equipment certification processes require rigorous testing and validation procedures to ensure consistent performance across different operational scenarios. For high-conductivity material bonding, specific standards address temperature uniformity requirements, typically mandating variations within ±2°C across the wafer surface, and pressure distribution tolerances that must remain within ±5% of target values. These specifications are critical for achieving reliable electrical connections in advanced semiconductor devices.

Metrology and inspection standards play a crucial role in validating bonding quality and equipment performance. Standards such as ASTM F1530 for measuring wafer bow and warp, and SEMI MF1811 for particle contamination assessment, provide frameworks for evaluating bonding outcomes. These measurement protocols ensure that equipment consistently produces bonds meeting electrical conductivity and mechanical strength requirements.

Emerging standards are being developed to address next-generation bonding technologies, including hybrid bonding and direct copper-to-copper bonding techniques. These evolving standards focus on sub-micron alignment accuracy, surface preparation requirements, and post-bonding annealing protocols. Equipment manufacturers must anticipate these developing standards to ensure their systems remain compliant with future industry requirements while maintaining compatibility with existing production environments.

Thermal Management in High-Conductivity Wafer Processing

Thermal management represents one of the most critical challenges in high-conductivity wafer bonding processes, as the exceptional thermal properties of materials like copper, silver, and graphene create unique processing requirements that differ significantly from conventional semiconductor materials. The high thermal conductivity of these materials, while advantageous for final device performance, introduces complex heat distribution patterns during bonding operations that can lead to non-uniform temperature profiles across the wafer surface.

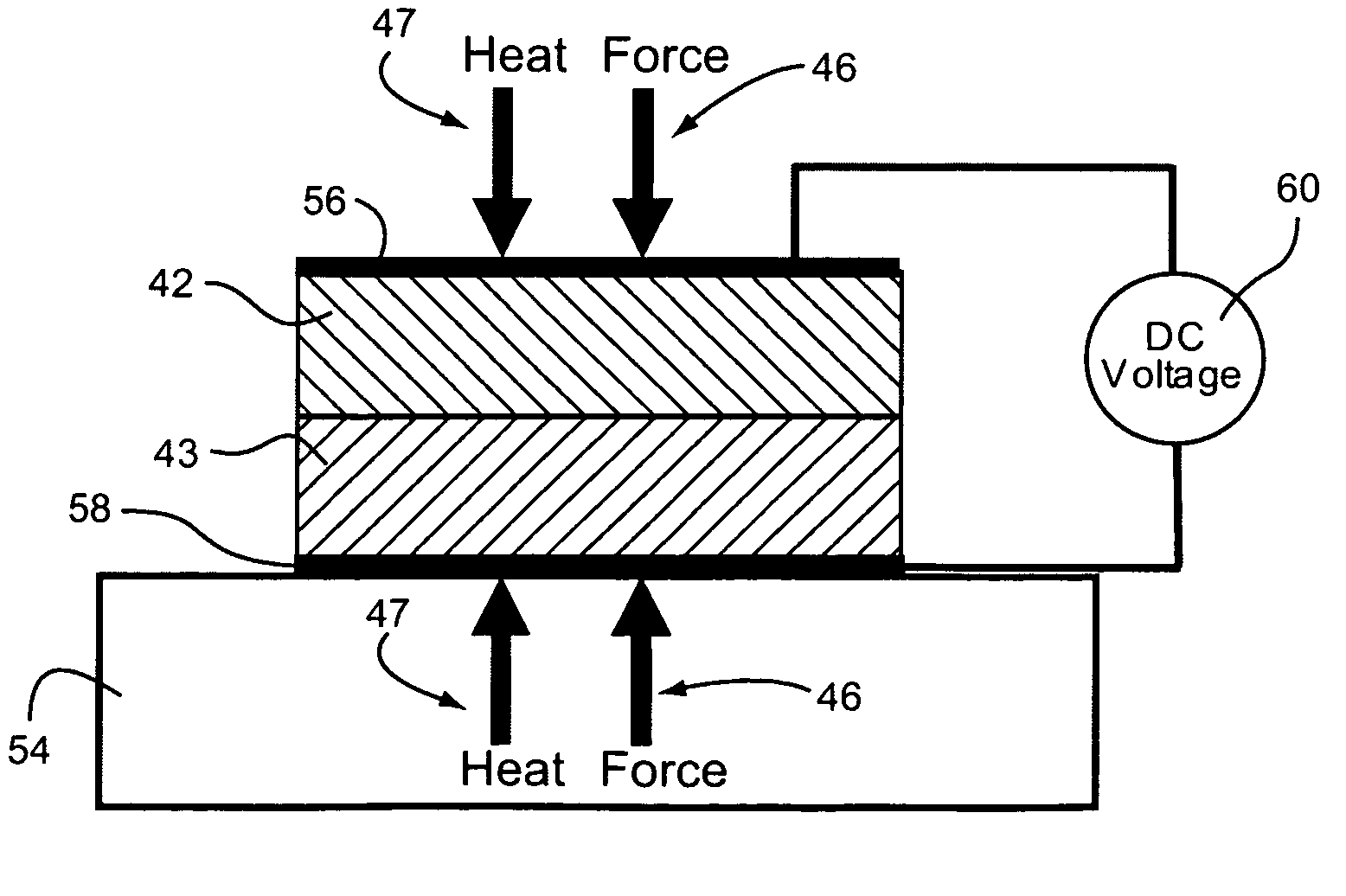

During wafer bonding processes involving high-conductivity materials, rapid heat dissipation occurs through the material substrate, creating temperature gradients that can compromise bond quality and uniformity. This phenomenon is particularly pronounced in direct bonding techniques where precise temperature control is essential for achieving optimal interfacial adhesion. The challenge is further amplified when bonding dissimilar materials with varying thermal expansion coefficients, as differential thermal stresses can induce warpage and delamination.

Advanced thermal management strategies have emerged to address these challenges, including the implementation of multi-zone heating systems that provide localized temperature control across different wafer regions. These systems utilize sophisticated feedback mechanisms with embedded temperature sensors to maintain uniform thermal profiles despite the rapid heat conduction characteristics of high-conductivity substrates. Additionally, thermal barrier coatings and intermediate buffer layers are increasingly employed to modulate heat transfer rates and create more controlled thermal environments during bonding.

The integration of real-time thermal monitoring systems has become essential for optimizing bonding parameters in high-conductivity wafer processing. These systems employ infrared thermography and thermocouple arrays to provide continuous temperature mapping, enabling dynamic adjustment of heating profiles to compensate for material-specific thermal behaviors. Such monitoring capabilities are crucial for maintaining process repeatability and achieving consistent bond quality across production batches.

Emerging approaches focus on leveraging the inherent thermal properties of high-conductivity materials as processing advantages rather than obstacles. This includes the development of rapid thermal bonding techniques that utilize controlled thermal cycling to enhance interfacial diffusion while minimizing thermal stress accumulation. These methods represent a paradigm shift toward thermal management strategies specifically designed for high-conductivity material systems.

During wafer bonding processes involving high-conductivity materials, rapid heat dissipation occurs through the material substrate, creating temperature gradients that can compromise bond quality and uniformity. This phenomenon is particularly pronounced in direct bonding techniques where precise temperature control is essential for achieving optimal interfacial adhesion. The challenge is further amplified when bonding dissimilar materials with varying thermal expansion coefficients, as differential thermal stresses can induce warpage and delamination.

Advanced thermal management strategies have emerged to address these challenges, including the implementation of multi-zone heating systems that provide localized temperature control across different wafer regions. These systems utilize sophisticated feedback mechanisms with embedded temperature sensors to maintain uniform thermal profiles despite the rapid heat conduction characteristics of high-conductivity substrates. Additionally, thermal barrier coatings and intermediate buffer layers are increasingly employed to modulate heat transfer rates and create more controlled thermal environments during bonding.

The integration of real-time thermal monitoring systems has become essential for optimizing bonding parameters in high-conductivity wafer processing. These systems employ infrared thermography and thermocouple arrays to provide continuous temperature mapping, enabling dynamic adjustment of heating profiles to compensate for material-specific thermal behaviors. Such monitoring capabilities are crucial for maintaining process repeatability and achieving consistent bond quality across production batches.

Emerging approaches focus on leveraging the inherent thermal properties of high-conductivity materials as processing advantages rather than obstacles. This includes the development of rapid thermal bonding techniques that utilize controlled thermal cycling to enhance interfacial diffusion while minimizing thermal stress accumulation. These methods represent a paradigm shift toward thermal management strategies specifically designed for high-conductivity material systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!