Analyzing Chip Package Plating Against Electrochemical Migration

APR 7, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chip Package Plating ECM Background and Objectives

Electrochemical migration (ECM) represents one of the most critical reliability challenges in modern semiconductor packaging, where metallic ions migrate under the influence of electric fields in the presence of moisture, potentially leading to catastrophic device failures. This phenomenon has gained increasing prominence as electronic devices continue to miniaturize while operating under higher power densities and more demanding environmental conditions.

The semiconductor industry's relentless pursuit of smaller form factors and enhanced performance has resulted in increasingly dense packaging architectures with reduced spacing between conductive elements. These design trends have inadvertently created conditions that are more susceptible to ECM, particularly in chip package plating systems where multiple metallic layers interact in complex electrochemical environments.

Traditional approaches to ECM mitigation have primarily focused on material selection and environmental control, yet these methods often prove insufficient for next-generation packaging requirements. The challenge is compounded by the diverse range of plating materials used in modern packages, including copper, nickel, gold, and various alloy systems, each exhibiting distinct electrochemical behaviors under operational stress conditions.

Current industry objectives center on developing comprehensive analytical frameworks that can predict ECM susceptibility during the design phase, thereby enabling proactive mitigation strategies rather than reactive solutions. This involves establishing standardized testing protocols that accurately simulate real-world operating conditions while providing quantitative metrics for ECM resistance evaluation.

The primary technical goal involves creating robust methodologies for analyzing the electrochemical stability of plating systems under various environmental and electrical stress conditions. This encompasses understanding the fundamental mechanisms governing ion migration, identifying critical design parameters that influence ECM susceptibility, and developing predictive models that can guide material selection and package design optimization.

Furthermore, the industry seeks to establish correlation between accelerated laboratory testing results and long-term field reliability performance, ensuring that ECM analysis techniques provide meaningful insights for product development cycles. The ultimate objective is to enable the design of inherently ECM-resistant package architectures that maintain reliability throughout their operational lifetime while supporting continued miniaturization trends.

The semiconductor industry's relentless pursuit of smaller form factors and enhanced performance has resulted in increasingly dense packaging architectures with reduced spacing between conductive elements. These design trends have inadvertently created conditions that are more susceptible to ECM, particularly in chip package plating systems where multiple metallic layers interact in complex electrochemical environments.

Traditional approaches to ECM mitigation have primarily focused on material selection and environmental control, yet these methods often prove insufficient for next-generation packaging requirements. The challenge is compounded by the diverse range of plating materials used in modern packages, including copper, nickel, gold, and various alloy systems, each exhibiting distinct electrochemical behaviors under operational stress conditions.

Current industry objectives center on developing comprehensive analytical frameworks that can predict ECM susceptibility during the design phase, thereby enabling proactive mitigation strategies rather than reactive solutions. This involves establishing standardized testing protocols that accurately simulate real-world operating conditions while providing quantitative metrics for ECM resistance evaluation.

The primary technical goal involves creating robust methodologies for analyzing the electrochemical stability of plating systems under various environmental and electrical stress conditions. This encompasses understanding the fundamental mechanisms governing ion migration, identifying critical design parameters that influence ECM susceptibility, and developing predictive models that can guide material selection and package design optimization.

Furthermore, the industry seeks to establish correlation between accelerated laboratory testing results and long-term field reliability performance, ensuring that ECM analysis techniques provide meaningful insights for product development cycles. The ultimate objective is to enable the design of inherently ECM-resistant package architectures that maintain reliability throughout their operational lifetime while supporting continued miniaturization trends.

Market Demand for ECM-Resistant Packaging Solutions

The semiconductor packaging industry faces mounting pressure to address electrochemical migration (ECM) challenges as electronic devices become increasingly miniaturized and operate under more demanding environmental conditions. Market demand for ECM-resistant packaging solutions has intensified significantly across multiple sectors, driven by the critical need to ensure long-term reliability and prevent catastrophic device failures.

Consumer electronics manufacturers represent the largest demand segment for ECM-resistant packaging technologies. Smartphones, tablets, and wearable devices require robust protection against moisture-induced failures, particularly as these products incorporate higher pin densities and reduced spacing between conductors. The automotive electronics sector has emerged as another major driver, where ECM-related failures can have severe safety implications in critical systems such as engine control units, advanced driver assistance systems, and electric vehicle power management modules.

Industrial automation and IoT applications constitute rapidly growing market segments demanding enhanced ECM protection. These applications often operate in harsh environments with elevated humidity, temperature fluctuations, and extended operational lifespans that amplify ECM risks. Data center infrastructure and telecommunications equipment also drive substantial demand, where system reliability directly impacts business continuity and service availability.

The aerospace and defense industries maintain stringent requirements for ECM-resistant solutions, given the mission-critical nature of their applications and the extreme environmental conditions encountered. Medical device manufacturers similarly prioritize ECM protection to ensure patient safety and regulatory compliance, particularly for implantable devices and life-support equipment.

Market dynamics reveal increasing customer willingness to invest in premium ECM-resistant packaging solutions as the total cost of ownership considerations favor prevention over post-failure remediation. Supply chain disruptions and quality issues associated with ECM failures have heightened awareness of the economic benefits of proactive protection measures.

Regional demand patterns show particularly strong growth in Asia-Pacific markets, where high-volume electronics manufacturing concentrates. North American and European markets emphasize advanced ECM protection for automotive and industrial applications, reflecting stricter regulatory requirements and quality standards in these sectors.

The convergence of 5G technology deployment, electric vehicle adoption, and Industry 4.0 initiatives continues to expand addressable market opportunities for ECM-resistant packaging solutions across diverse application domains.

Consumer electronics manufacturers represent the largest demand segment for ECM-resistant packaging technologies. Smartphones, tablets, and wearable devices require robust protection against moisture-induced failures, particularly as these products incorporate higher pin densities and reduced spacing between conductors. The automotive electronics sector has emerged as another major driver, where ECM-related failures can have severe safety implications in critical systems such as engine control units, advanced driver assistance systems, and electric vehicle power management modules.

Industrial automation and IoT applications constitute rapidly growing market segments demanding enhanced ECM protection. These applications often operate in harsh environments with elevated humidity, temperature fluctuations, and extended operational lifespans that amplify ECM risks. Data center infrastructure and telecommunications equipment also drive substantial demand, where system reliability directly impacts business continuity and service availability.

The aerospace and defense industries maintain stringent requirements for ECM-resistant solutions, given the mission-critical nature of their applications and the extreme environmental conditions encountered. Medical device manufacturers similarly prioritize ECM protection to ensure patient safety and regulatory compliance, particularly for implantable devices and life-support equipment.

Market dynamics reveal increasing customer willingness to invest in premium ECM-resistant packaging solutions as the total cost of ownership considerations favor prevention over post-failure remediation. Supply chain disruptions and quality issues associated with ECM failures have heightened awareness of the economic benefits of proactive protection measures.

Regional demand patterns show particularly strong growth in Asia-Pacific markets, where high-volume electronics manufacturing concentrates. North American and European markets emphasize advanced ECM protection for automotive and industrial applications, reflecting stricter regulatory requirements and quality standards in these sectors.

The convergence of 5G technology deployment, electric vehicle adoption, and Industry 4.0 initiatives continues to expand addressable market opportunities for ECM-resistant packaging solutions across diverse application domains.

Current ECM Challenges in Chip Package Plating

Electrochemical migration in chip package plating represents one of the most critical reliability challenges facing modern semiconductor packaging technologies. The phenomenon occurs when metal ions migrate under the influence of electric fields in the presence of moisture, leading to dendritic growth that can cause catastrophic device failures. This challenge has become increasingly prominent as packaging densities continue to increase and operating voltages remain significant enough to drive ionic transport.

The primary challenge stems from the inherent vulnerability of commonly used plating materials, particularly copper and silver, to electrochemical migration under humid conditions. Copper, while offering excellent electrical conductivity and cost-effectiveness, exhibits high susceptibility to migration when exposed to bias voltages exceeding 5V in humid environments. Silver-based finishes, despite their superior solderability, demonstrate even greater migration tendencies due to silver's high ionic mobility in aqueous solutions.

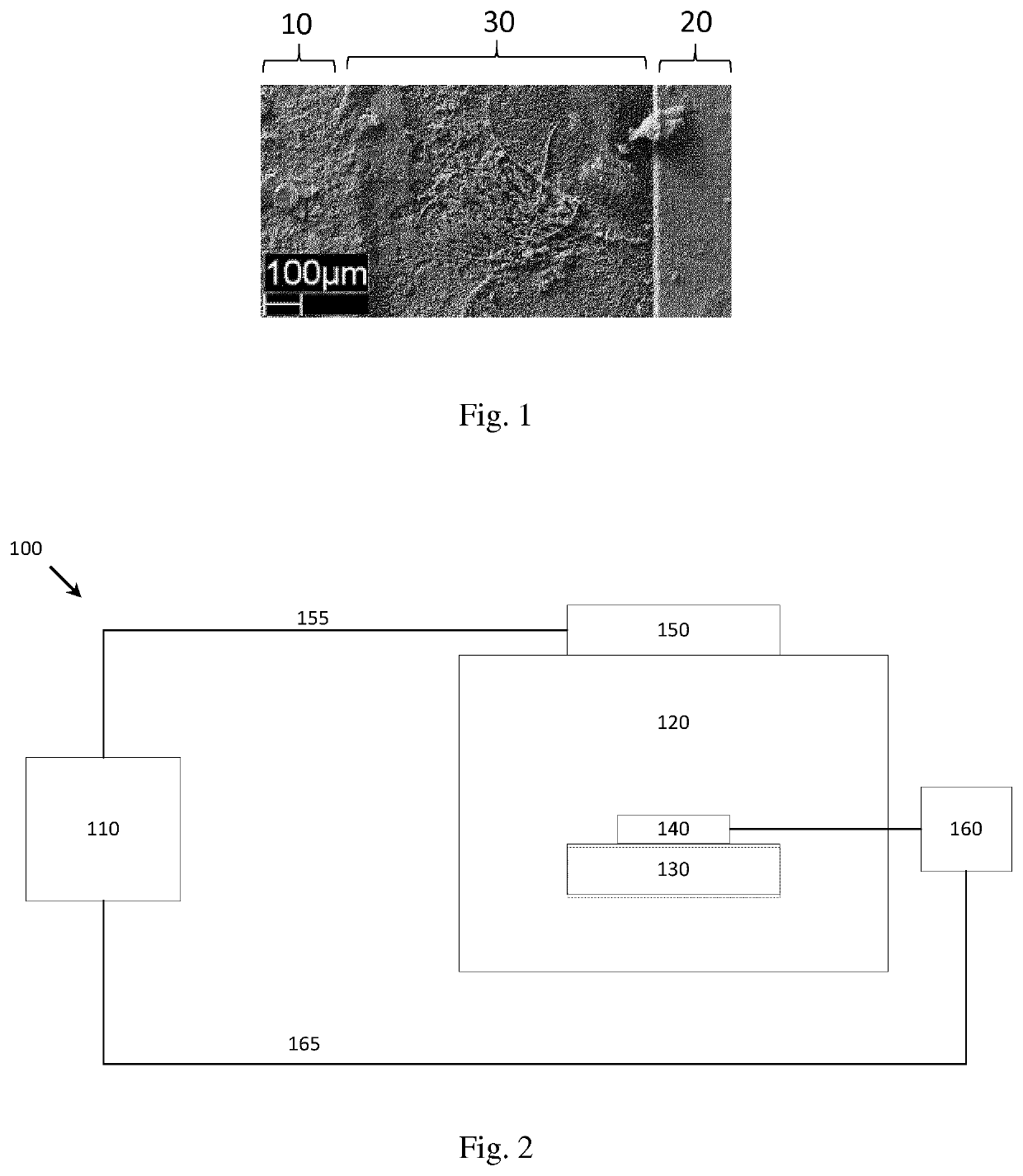

Package miniaturization has exacerbated ECM challenges by reducing spacing between conductors to sub-100 micrometer dimensions. These tight geometries create high electric field concentrations that accelerate ion migration rates, while simultaneously reducing the physical distance required for dendrite bridging. The combination of reduced spacing and increased field strength creates a perfect storm for ECM-induced failures.

Environmental factors present another significant challenge category. Temperature cycling induces thermal stress that can create microcracks in protective coatings, providing pathways for moisture ingress. Humidity levels above 60% relative humidity dramatically increase ECM susceptibility, yet many applications require operation in such conditions. The interaction between temperature and humidity creates complex failure mechanisms that are difficult to predict and mitigate.

Manufacturing process variations contribute substantially to ECM vulnerability. Inconsistent plating thickness, surface roughness variations, and contamination from flux residues or handling create localized weak points where migration preferentially initiates. These process-induced defects often remain undetected during standard quality control procedures but become critical failure sites under operational stress.

The challenge is further complicated by the need to balance ECM resistance with other performance requirements. Protective coatings that effectively prevent moisture ingress may compromise thermal dissipation or mechanical flexibility. Alternative plating materials with improved ECM resistance often sacrifice electrical performance or increase manufacturing costs significantly.

Current testing methodologies present additional challenges in accurately predicting long-term ECM behavior. Accelerated testing protocols may not adequately represent real-world operating conditions, leading to either over-conservative designs or unexpected field failures. The complex interplay between multiple environmental and electrical stressors makes it difficult to establish reliable failure prediction models.

The primary challenge stems from the inherent vulnerability of commonly used plating materials, particularly copper and silver, to electrochemical migration under humid conditions. Copper, while offering excellent electrical conductivity and cost-effectiveness, exhibits high susceptibility to migration when exposed to bias voltages exceeding 5V in humid environments. Silver-based finishes, despite their superior solderability, demonstrate even greater migration tendencies due to silver's high ionic mobility in aqueous solutions.

Package miniaturization has exacerbated ECM challenges by reducing spacing between conductors to sub-100 micrometer dimensions. These tight geometries create high electric field concentrations that accelerate ion migration rates, while simultaneously reducing the physical distance required for dendrite bridging. The combination of reduced spacing and increased field strength creates a perfect storm for ECM-induced failures.

Environmental factors present another significant challenge category. Temperature cycling induces thermal stress that can create microcracks in protective coatings, providing pathways for moisture ingress. Humidity levels above 60% relative humidity dramatically increase ECM susceptibility, yet many applications require operation in such conditions. The interaction between temperature and humidity creates complex failure mechanisms that are difficult to predict and mitigate.

Manufacturing process variations contribute substantially to ECM vulnerability. Inconsistent plating thickness, surface roughness variations, and contamination from flux residues or handling create localized weak points where migration preferentially initiates. These process-induced defects often remain undetected during standard quality control procedures but become critical failure sites under operational stress.

The challenge is further complicated by the need to balance ECM resistance with other performance requirements. Protective coatings that effectively prevent moisture ingress may compromise thermal dissipation or mechanical flexibility. Alternative plating materials with improved ECM resistance often sacrifice electrical performance or increase manufacturing costs significantly.

Current testing methodologies present additional challenges in accurately predicting long-term ECM behavior. Accelerated testing protocols may not adequately represent real-world operating conditions, leading to either over-conservative designs or unexpected field failures. The complex interplay between multiple environmental and electrical stressors makes it difficult to establish reliable failure prediction models.

Existing ECM Prevention Solutions in Plating

01 Barrier layer structures to prevent electrochemical migration

Implementation of barrier layers or protective coatings between conductive elements in chip packages can effectively prevent electrochemical migration. These barrier structures act as physical and chemical barriers that inhibit ion transport and dendrite formation between adjacent conductors. The barrier materials are selected for their resistance to moisture penetration and their ability to block ionic pathways that would otherwise facilitate migration under electrical bias.- Barrier layer structures to prevent electrochemical migration: Implementation of barrier layers or protective coatings between conductive elements in chip packages can effectively prevent electrochemical migration. These barrier structures are designed to block ion transport and moisture penetration, which are primary causes of migration. The barrier materials are typically composed of insulating compounds or metal oxides that provide high resistance to ionic movement while maintaining compatibility with standard packaging processes.

- Plating composition optimization for migration resistance: Modification of electroplating bath compositions and plating parameters can significantly reduce the susceptibility to electrochemical migration. This includes adjusting the chemical composition of plating solutions, controlling grain structure, and incorporating additives that enhance the stability of deposited metal layers. The optimized plating processes result in denser, more uniform metal deposits with fewer defects that could serve as migration initiation sites.

- Surface treatment and passivation methods: Application of surface treatment techniques and passivation processes to plated surfaces can create protective layers that inhibit electrochemical migration. These treatments modify the surface chemistry and morphology to reduce reactivity with environmental moisture and contaminants. The passivation layers act as diffusion barriers while maintaining electrical connectivity where required.

- Package design modifications for migration prevention: Structural design changes in chip package architecture can minimize electrochemical migration risks by optimizing conductor spacing, implementing moisture-resistant encapsulation, and controlling electric field distribution. These design approaches focus on reducing the driving forces for migration and limiting exposure to environmental factors that promote the phenomenon. Advanced packaging configurations incorporate features specifically engineered to interrupt potential migration paths.

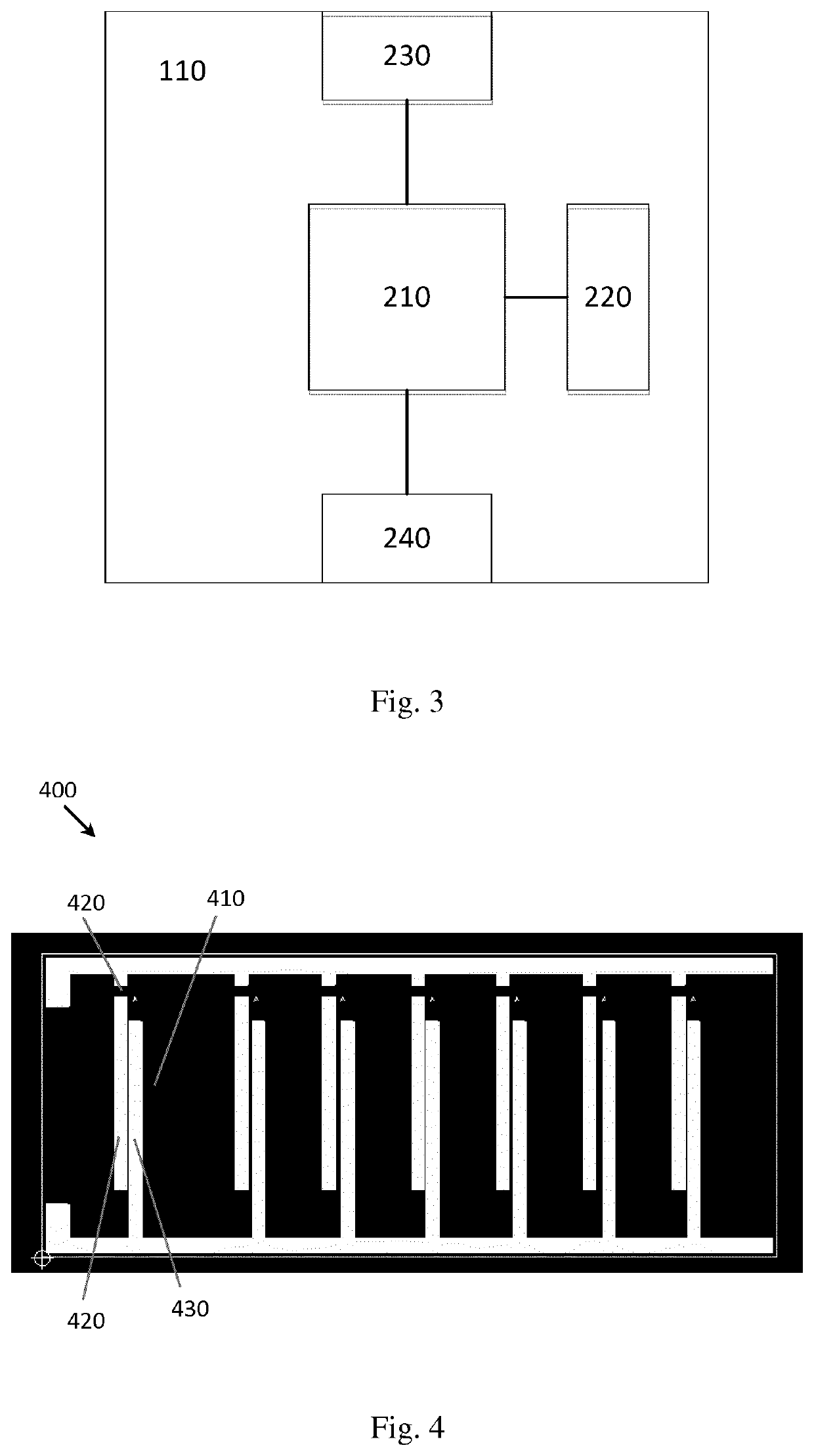

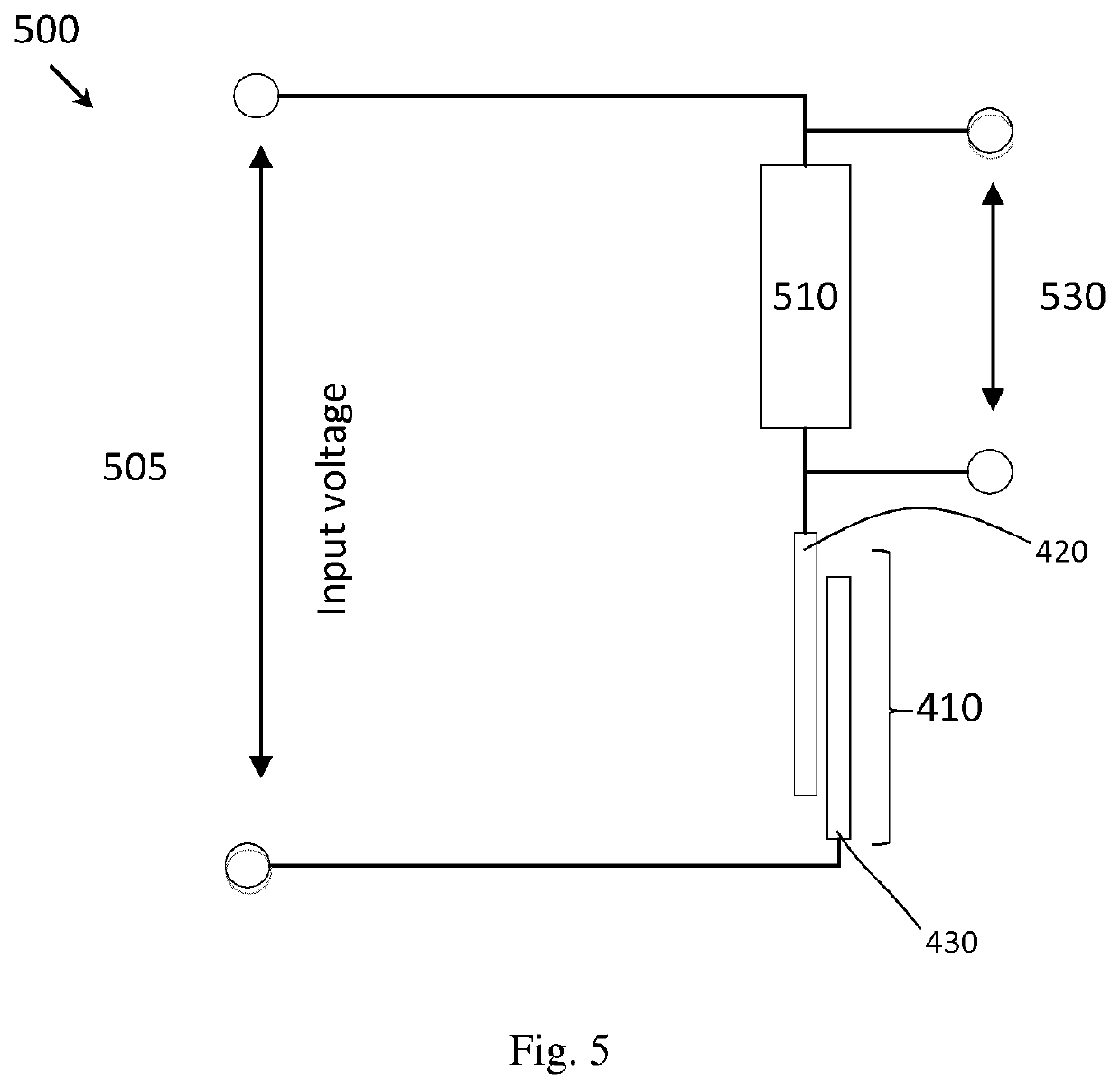

- Testing and evaluation methods for migration susceptibility: Development of accelerated testing protocols and evaluation methodologies to assess electrochemical migration resistance in plated chip packages. These methods involve controlled environmental exposure, electrical bias application, and analytical techniques to detect early signs of migration. The testing approaches enable prediction of long-term reliability and validation of migration prevention strategies under various operating conditions.

02 Plating composition and material selection for migration resistance

The selection and formulation of plating materials with inherent resistance to electrochemical migration is critical. This includes the use of specific metal alloys, plating bath compositions, and additives that reduce the susceptibility of deposited layers to ion migration. The plating composition can be optimized to create dense, uniform coatings with minimal defects that could serve as initiation sites for migration. Material properties such as grain structure, surface morphology, and chemical stability are carefully controlled during the electroplating process.Expand Specific Solutions03 Surface treatment and passivation techniques

Post-plating surface treatments and passivation methods are employed to enhance migration resistance. These treatments modify the surface chemistry and create protective layers that reduce the electrochemical activity of plated surfaces. Surface modification techniques can include chemical treatments, plasma processing, or the application of conversion coatings that seal the surface and prevent moisture ingress and ion mobility under operating conditions.Expand Specific Solutions04 Package design and spacing optimization

Optimization of package design parameters, particularly the spacing and geometry between conductive traces and pads, plays a crucial role in mitigating electrochemical migration risks. Design considerations include increasing the distance between conductors at different potentials, implementing guard rings or grounded structures, and optimizing the layout to minimize electric field concentrations. The package substrate material selection and its moisture absorption characteristics are also important factors in the overall design strategy.Expand Specific Solutions05 Testing and evaluation methods for migration susceptibility

Specialized testing methodologies and evaluation techniques are used to assess the electrochemical migration susceptibility of chip package plating systems. These methods typically involve accelerated testing under controlled temperature, humidity, and voltage bias conditions to simulate long-term reliability. Testing protocols may include water drop tests, humidity bias tests, and electrochemical impedance measurements to characterize migration behavior and validate the effectiveness of mitigation strategies before production implementation.Expand Specific Solutions

Key Players in Semiconductor Packaging Industry

The chip package plating against electrochemical migration field represents a mature yet evolving market segment within the broader semiconductor packaging industry. The market demonstrates significant scale, driven by increasing demand for reliable electronic devices across automotive, mobile, and IoT applications. Technology maturity varies considerably among key players, with industry leaders like Taiwan Semiconductor Manufacturing Co., Samsung Electronics, and Intel Corp. advancing sophisticated anti-migration plating solutions. Equipment manufacturers including Applied Materials, Lam Research Corp., and ACM Research provide critical process technologies. Asian packaging specialists such as Advanced Semiconductor Engineering, Xintec, and Changdian Technology focus on implementation expertise. The competitive landscape shows established foundries and packaging companies leading innovation, while emerging players like Anhui Jixin Microelectronics and specialized research institutions contribute to next-generation solutions addressing increasingly stringent reliability requirements in advanced packaging applications.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced electrochemical migration (ECM) prevention techniques through optimized plating processes and material selection. Their approach includes using copper-based interconnects with barrier layers to minimize ion migration, implementing strict moisture control during packaging, and utilizing specialized surface treatments that reduce the formation of conductive paths. The company employs multi-layer metallization schemes with carefully controlled grain structures to enhance resistance against ECM. Additionally, TSMC has integrated real-time monitoring systems during the plating process to detect early signs of potential migration issues, ensuring high reliability in their advanced packaging solutions for mobile and high-performance computing applications.

Strengths: Industry-leading process control and extensive R&D capabilities in advanced packaging. Weaknesses: High cost implementation and complex manufacturing requirements.

Applied Materials, Inc.

Technical Solution: Applied Materials provides comprehensive ECM mitigation solutions through their advanced plating equipment and process technologies. Their systems feature precise control of electrochemical deposition parameters, including current density, temperature, and electrolyte composition, which are critical for preventing migration-prone microstructures. The company's Electrochemical Deposition (ECD) systems incorporate in-situ monitoring capabilities that track plating uniformity and detect potential defects that could lead to ECM. Their approach also includes post-plating treatments such as annealing processes that optimize grain structure and reduce residual stresses. Applied Materials has developed proprietary additives and plating chemistries that enhance the ECM resistance of deposited films while maintaining excellent electrical and mechanical properties for semiconductor packaging applications.

Strengths: Comprehensive equipment solutions and strong process expertise across multiple plating technologies. Weaknesses: Equipment-focused approach may require integration with other vendors' solutions.

Core Innovations in ECM-Resistant Plating Materials

Bump Pad Metallurgy Employing An Electrolytic Cu / Electorlytic Ni / Electrolytic Cu Stack

PatentInactiveUS20090174045A1

Innovation

- A bump pad metallurgy structure comprising a stack of electrolytic Cu/electrolytic Ni/electrolytic Cu is employed, where the electrolytic Ni portions provide enhanced resistance to electromigration and the second electrolytic Cu portions serve as an adhesion layer and oxidation protection, reducing the likelihood of mechanical failures.

Apparatus and method relating to electrochemical migration

PatentActiveUS11470727B2

Innovation

- A method involving thermal association of electrical circuitry with a thermal reservoir in a test chamber, where temperature and humidity are controlled to simulate resistance to ECM, allowing condensation to form and monitor electrical properties for dendrite growth, and an electrical circuit assembly method using tin plating and solder with specific compositions to enhance resistance to ECM.

Environmental Regulations for Plating Processes

The semiconductor industry faces increasingly stringent environmental regulations governing electroplating processes used in chip package manufacturing. These regulations primarily target the reduction of hazardous substances and the implementation of sustainable manufacturing practices to minimize environmental impact while maintaining product reliability against electrochemical migration.

The Restriction of Hazardous Substances (RoHS) directive and its amendments significantly influence plating material selection for semiconductor packages. Lead-based solders and finishes, once standard in the industry, have been largely phased out in favor of lead-free alternatives. This transition has necessitated the development of new plating chemistries and processes that maintain equivalent or superior performance in preventing electrochemical migration while complying with environmental mandates.

REACH (Registration, Evaluation, Authorization and restriction of Chemicals) regulations in Europe impose strict controls on chemical substances used in plating baths. Manufacturers must demonstrate that their plating processes do not utilize substances of very high concern (SVHC) or obtain proper authorization for their use. This has driven innovation in plating chemistry formulations, particularly in the development of environmentally benign additives and brighteners that maintain surface quality and migration resistance.

Water discharge regulations significantly impact plating facility operations, requiring comprehensive wastewater treatment systems to remove heavy metals and organic compounds before discharge. The implementation of closed-loop systems and advanced filtration technologies has become essential for compliance, while also reducing operational costs through chemical recovery and reuse.

Air emission standards regulate volatile organic compounds (VOCs) and particulate matter released during plating operations. Facilities must install appropriate ventilation and scrubbing systems to capture and treat emissions, particularly from acid etching and cleaning processes that precede plating operations.

The emerging concept of extended producer responsibility (EPR) is influencing plating process design, requiring manufacturers to consider the entire lifecycle impact of their products. This includes developing plating solutions that facilitate end-of-life recycling and minimize environmental burden during disposal, while maintaining the electrical and mechanical properties necessary to prevent electrochemical migration in service conditions.

The Restriction of Hazardous Substances (RoHS) directive and its amendments significantly influence plating material selection for semiconductor packages. Lead-based solders and finishes, once standard in the industry, have been largely phased out in favor of lead-free alternatives. This transition has necessitated the development of new plating chemistries and processes that maintain equivalent or superior performance in preventing electrochemical migration while complying with environmental mandates.

REACH (Registration, Evaluation, Authorization and restriction of Chemicals) regulations in Europe impose strict controls on chemical substances used in plating baths. Manufacturers must demonstrate that their plating processes do not utilize substances of very high concern (SVHC) or obtain proper authorization for their use. This has driven innovation in plating chemistry formulations, particularly in the development of environmentally benign additives and brighteners that maintain surface quality and migration resistance.

Water discharge regulations significantly impact plating facility operations, requiring comprehensive wastewater treatment systems to remove heavy metals and organic compounds before discharge. The implementation of closed-loop systems and advanced filtration technologies has become essential for compliance, while also reducing operational costs through chemical recovery and reuse.

Air emission standards regulate volatile organic compounds (VOCs) and particulate matter released during plating operations. Facilities must install appropriate ventilation and scrubbing systems to capture and treat emissions, particularly from acid etching and cleaning processes that precede plating operations.

The emerging concept of extended producer responsibility (EPR) is influencing plating process design, requiring manufacturers to consider the entire lifecycle impact of their products. This includes developing plating solutions that facilitate end-of-life recycling and minimize environmental burden during disposal, while maintaining the electrical and mechanical properties necessary to prevent electrochemical migration in service conditions.

Reliability Standards for ECM Testing Methods

The establishment of comprehensive reliability standards for electrochemical migration (ECM) testing methods represents a critical foundation for evaluating chip package plating performance. Current industry standards primarily rely on JEDEC JESD22-B112 and IPC-TM-650 methodologies, which provide standardized test conditions including temperature, humidity, bias voltage, and test duration parameters. These standards typically specify testing at 85°C/85% relative humidity with applied voltages ranging from 3.3V to 50V, depending on the specific application requirements.

International standardization efforts have converged around several key testing protocols that ensure reproducibility and comparability across different laboratories and manufacturers. The JEDEC standard emphasizes accelerated testing conditions with specific sample preparation requirements, including surface cleanliness protocols and electrode spacing configurations. Meanwhile, IPC standards focus on practical implementation aspects, providing detailed guidance on test fixture design and measurement procedures for detecting ion migration phenomena.

Testing methodology standardization encompasses multiple critical parameters that directly influence ECM susceptibility assessment. Standard test vehicles typically feature comb-pattern electrodes with spacing ranging from 50 to 500 micrometers, fabricated on standardized substrates to eliminate material variability. The standards mandate specific environmental conditioning procedures, including pre-test baking cycles and controlled atmosphere exposure, to ensure consistent baseline conditions across all test specimens.

Measurement criteria within these standards define clear failure thresholds based on leakage current increases and visual inspection requirements. Most standards establish failure criteria when leakage current exceeds predetermined levels, typically 10^-5 amperes, or when visible dendrite formation occurs between electrodes. These quantitative metrics enable objective assessment of ECM resistance across different plating materials and process conditions.

Recent standardization developments have incorporated advanced characterization techniques, including scanning electron microscopy requirements and ion chromatography analysis protocols. These enhanced standards provide more comprehensive evaluation capabilities, enabling detailed understanding of migration mechanisms and failure modes. The integration of statistical analysis requirements ensures robust data interpretation and supports reliable lifetime prediction models for various chip package plating systems under diverse operational environments.

International standardization efforts have converged around several key testing protocols that ensure reproducibility and comparability across different laboratories and manufacturers. The JEDEC standard emphasizes accelerated testing conditions with specific sample preparation requirements, including surface cleanliness protocols and electrode spacing configurations. Meanwhile, IPC standards focus on practical implementation aspects, providing detailed guidance on test fixture design and measurement procedures for detecting ion migration phenomena.

Testing methodology standardization encompasses multiple critical parameters that directly influence ECM susceptibility assessment. Standard test vehicles typically feature comb-pattern electrodes with spacing ranging from 50 to 500 micrometers, fabricated on standardized substrates to eliminate material variability. The standards mandate specific environmental conditioning procedures, including pre-test baking cycles and controlled atmosphere exposure, to ensure consistent baseline conditions across all test specimens.

Measurement criteria within these standards define clear failure thresholds based on leakage current increases and visual inspection requirements. Most standards establish failure criteria when leakage current exceeds predetermined levels, typically 10^-5 amperes, or when visible dendrite formation occurs between electrodes. These quantitative metrics enable objective assessment of ECM resistance across different plating materials and process conditions.

Recent standardization developments have incorporated advanced characterization techniques, including scanning electron microscopy requirements and ion chromatography analysis protocols. These enhanced standards provide more comprehensive evaluation capabilities, enabling detailed understanding of migration mechanisms and failure modes. The integration of statistical analysis requirements ensures robust data interpretation and supports reliable lifetime prediction models for various chip package plating systems under diverse operational environments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!