Optimizing Bond Pad Design for Stress Reduction in Chip Packaging

APR 7, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Bond Pad Stress Challenges and Design Goals

Bond pad design in semiconductor packaging faces significant mechanical stress challenges that directly impact device reliability and manufacturing yield. The primary stress sources include thermal expansion mismatches between different materials, mechanical forces during wire bonding processes, and package-induced stresses from molding compounds and substrate interactions. These stresses can lead to metal layer cracking, delamination at interfaces, and ultimately device failure.

Thermal cycling represents one of the most critical stress factors, as repeated expansion and contraction cycles create fatigue conditions in bond pad structures. The coefficient of thermal expansion differences between silicon, aluminum metallization, and packaging materials generate substantial mechanical loads. Additionally, the wire bonding process itself introduces localized stresses through ultrasonic energy, thermosonic heating, and mechanical pressure applied during bond formation.

Current bond pad designs often exhibit stress concentration at sharp corners, narrow metal traces, and interface boundaries between different material layers. These geometric discontinuities create failure initiation points where cracks can propagate under cyclic loading conditions. The traditional rectangular bond pad geometry, while space-efficient, tends to concentrate stresses at corner regions where the highest failure rates typically occur.

The evolution toward advanced packaging technologies, including flip-chip, wafer-level packaging, and 3D integration, has intensified stress management requirements. Smaller feature sizes, higher interconnect densities, and increased power densities create more challenging thermal and mechanical environments. These trends demand innovative bond pad designs that can withstand higher stress levels while maintaining electrical performance and manufacturing compatibility.

Design optimization goals focus on achieving uniform stress distribution across bond pad structures while minimizing peak stress concentrations. Key objectives include extending fatigue life under thermal cycling conditions, improving resistance to wire bonding-induced damage, and maintaining electrical connectivity throughout the device operational lifetime. Additionally, designs must accommodate manufacturing process variations and provide adequate safety margins for reliable high-volume production.

Advanced design approaches target stress reduction through geometric optimization, material selection, and structural modifications. These include implementing rounded corners to eliminate stress concentration points, utilizing stress-relief structures such as serpentine traces, and incorporating buffer layers with intermediate thermal expansion properties. The integration of finite element analysis and reliability modeling enables predictive design optimization before physical prototyping.

Thermal cycling represents one of the most critical stress factors, as repeated expansion and contraction cycles create fatigue conditions in bond pad structures. The coefficient of thermal expansion differences between silicon, aluminum metallization, and packaging materials generate substantial mechanical loads. Additionally, the wire bonding process itself introduces localized stresses through ultrasonic energy, thermosonic heating, and mechanical pressure applied during bond formation.

Current bond pad designs often exhibit stress concentration at sharp corners, narrow metal traces, and interface boundaries between different material layers. These geometric discontinuities create failure initiation points where cracks can propagate under cyclic loading conditions. The traditional rectangular bond pad geometry, while space-efficient, tends to concentrate stresses at corner regions where the highest failure rates typically occur.

The evolution toward advanced packaging technologies, including flip-chip, wafer-level packaging, and 3D integration, has intensified stress management requirements. Smaller feature sizes, higher interconnect densities, and increased power densities create more challenging thermal and mechanical environments. These trends demand innovative bond pad designs that can withstand higher stress levels while maintaining electrical performance and manufacturing compatibility.

Design optimization goals focus on achieving uniform stress distribution across bond pad structures while minimizing peak stress concentrations. Key objectives include extending fatigue life under thermal cycling conditions, improving resistance to wire bonding-induced damage, and maintaining electrical connectivity throughout the device operational lifetime. Additionally, designs must accommodate manufacturing process variations and provide adequate safety margins for reliable high-volume production.

Advanced design approaches target stress reduction through geometric optimization, material selection, and structural modifications. These include implementing rounded corners to eliminate stress concentration points, utilizing stress-relief structures such as serpentine traces, and incorporating buffer layers with intermediate thermal expansion properties. The integration of finite element analysis and reliability modeling enables predictive design optimization before physical prototyping.

Market Demand for Reliable Chip Packaging Solutions

The semiconductor industry faces mounting pressure to deliver increasingly reliable chip packaging solutions as electronic devices become more sophisticated and mission-critical applications expand. Modern consumer electronics, automotive systems, aerospace components, and industrial equipment demand unprecedented levels of reliability and longevity from their semiconductor components. This growing emphasis on reliability has created substantial market demand for advanced packaging technologies that can withstand mechanical stress, thermal cycling, and environmental challenges.

Automotive electronics represents one of the most demanding sectors driving this market expansion. Advanced driver assistance systems, electric vehicle power management, and autonomous driving technologies require semiconductor packages that can operate reliably for decades under harsh conditions. The automotive industry's shift toward electrification and automation has intensified requirements for packaging solutions that maintain electrical integrity while managing thermal and mechanical stresses effectively.

Consumer electronics manufacturers are simultaneously pushing for thinner, lighter devices with enhanced performance capabilities. This miniaturization trend creates significant challenges for traditional packaging approaches, as reduced form factors concentrate mechanical stresses and thermal loads. The market increasingly values packaging solutions that can maintain reliability while enabling continued device miniaturization and performance improvements.

Data center and telecommunications infrastructure applications represent another critical market segment demanding enhanced packaging reliability. These systems require continuous operation with minimal downtime, making packaging-related failures particularly costly. The expansion of cloud computing, artificial intelligence processing, and high-speed communications networks has created substantial demand for packaging technologies that can support high-performance processors while ensuring long-term reliability.

Industrial and aerospace applications impose additional stringent requirements for packaging reliability under extreme environmental conditions. These sectors require semiconductor packages capable of withstanding temperature extremes, vibration, humidity, and radiation exposure while maintaining consistent performance over extended operational lifespans.

The convergence of these market demands has created significant opportunities for innovative packaging solutions that address stress-related reliability challenges. Companies developing advanced bond pad designs and stress reduction technologies are positioned to capture substantial market value by enabling more reliable semiconductor packages across these diverse application sectors.

Automotive electronics represents one of the most demanding sectors driving this market expansion. Advanced driver assistance systems, electric vehicle power management, and autonomous driving technologies require semiconductor packages that can operate reliably for decades under harsh conditions. The automotive industry's shift toward electrification and automation has intensified requirements for packaging solutions that maintain electrical integrity while managing thermal and mechanical stresses effectively.

Consumer electronics manufacturers are simultaneously pushing for thinner, lighter devices with enhanced performance capabilities. This miniaturization trend creates significant challenges for traditional packaging approaches, as reduced form factors concentrate mechanical stresses and thermal loads. The market increasingly values packaging solutions that can maintain reliability while enabling continued device miniaturization and performance improvements.

Data center and telecommunications infrastructure applications represent another critical market segment demanding enhanced packaging reliability. These systems require continuous operation with minimal downtime, making packaging-related failures particularly costly. The expansion of cloud computing, artificial intelligence processing, and high-speed communications networks has created substantial demand for packaging technologies that can support high-performance processors while ensuring long-term reliability.

Industrial and aerospace applications impose additional stringent requirements for packaging reliability under extreme environmental conditions. These sectors require semiconductor packages capable of withstanding temperature extremes, vibration, humidity, and radiation exposure while maintaining consistent performance over extended operational lifespans.

The convergence of these market demands has created significant opportunities for innovative packaging solutions that address stress-related reliability challenges. Companies developing advanced bond pad designs and stress reduction technologies are positioned to capture substantial market value by enabling more reliable semiconductor packages across these diverse application sectors.

Current Bond Pad Stress Issues and Design Limitations

Bond pad stress represents one of the most critical reliability challenges in modern semiconductor packaging, particularly as device miniaturization and performance demands continue to escalate. The fundamental issue stems from the mechanical mismatch between different materials in the packaging stack, where bond pads serve as the primary interface between the silicon die and external interconnects. During wire bonding processes, significant mechanical forces are applied to create reliable electrical connections, often resulting in stress concentrations that can propagate into the underlying silicon substrate and cause structural damage.

Thermal cycling during device operation exacerbates these stress-related problems, as coefficient of thermal expansion mismatches between aluminum bond pads, silicon substrates, and packaging materials create cyclical stress patterns. These thermal stresses can lead to bond pad peeling, metal layer delamination, and crack propagation in the passivation layers. The situation becomes particularly problematic in high-power applications where temperature excursions are frequent and severe, potentially causing premature device failure through stress-induced degradation mechanisms.

Current bond pad design methodologies face significant limitations in addressing these multifaceted stress challenges. Traditional rectangular pad geometries, while simple to manufacture, create stress concentration points at corners and edges where mechanical forces are not uniformly distributed. The standard aluminum metallization systems, though cost-effective, exhibit poor mechanical properties under high-stress conditions and limited resistance to plastic deformation during bonding operations.

Dimensional constraints imposed by shrinking die sizes further complicate stress management efforts. As bond pad pitch continues to decrease to accommodate higher pin counts, the available area for stress distribution becomes increasingly limited. This geometric constraint forces designers to balance electrical performance requirements against mechanical reliability considerations, often resulting in suboptimal solutions that compromise long-term device reliability.

The lack of comprehensive stress modeling tools specifically tailored for bond pad applications represents another significant limitation. Existing finite element analysis approaches often fail to accurately capture the complex multi-physics interactions occurring during bonding processes, including plastic deformation, interfacial adhesion effects, and dynamic loading conditions. This modeling gap makes it difficult to predict stress-related failure modes during the design phase, leading to costly reliability issues discovered only during qualification testing or field deployment.

Thermal cycling during device operation exacerbates these stress-related problems, as coefficient of thermal expansion mismatches between aluminum bond pads, silicon substrates, and packaging materials create cyclical stress patterns. These thermal stresses can lead to bond pad peeling, metal layer delamination, and crack propagation in the passivation layers. The situation becomes particularly problematic in high-power applications where temperature excursions are frequent and severe, potentially causing premature device failure through stress-induced degradation mechanisms.

Current bond pad design methodologies face significant limitations in addressing these multifaceted stress challenges. Traditional rectangular pad geometries, while simple to manufacture, create stress concentration points at corners and edges where mechanical forces are not uniformly distributed. The standard aluminum metallization systems, though cost-effective, exhibit poor mechanical properties under high-stress conditions and limited resistance to plastic deformation during bonding operations.

Dimensional constraints imposed by shrinking die sizes further complicate stress management efforts. As bond pad pitch continues to decrease to accommodate higher pin counts, the available area for stress distribution becomes increasingly limited. This geometric constraint forces designers to balance electrical performance requirements against mechanical reliability considerations, often resulting in suboptimal solutions that compromise long-term device reliability.

The lack of comprehensive stress modeling tools specifically tailored for bond pad applications represents another significant limitation. Existing finite element analysis approaches often fail to accurately capture the complex multi-physics interactions occurring during bonding processes, including plastic deformation, interfacial adhesion effects, and dynamic loading conditions. This modeling gap makes it difficult to predict stress-related failure modes during the design phase, leading to costly reliability issues discovered only during qualification testing or field deployment.

Existing Bond Pad Stress Reduction Solutions

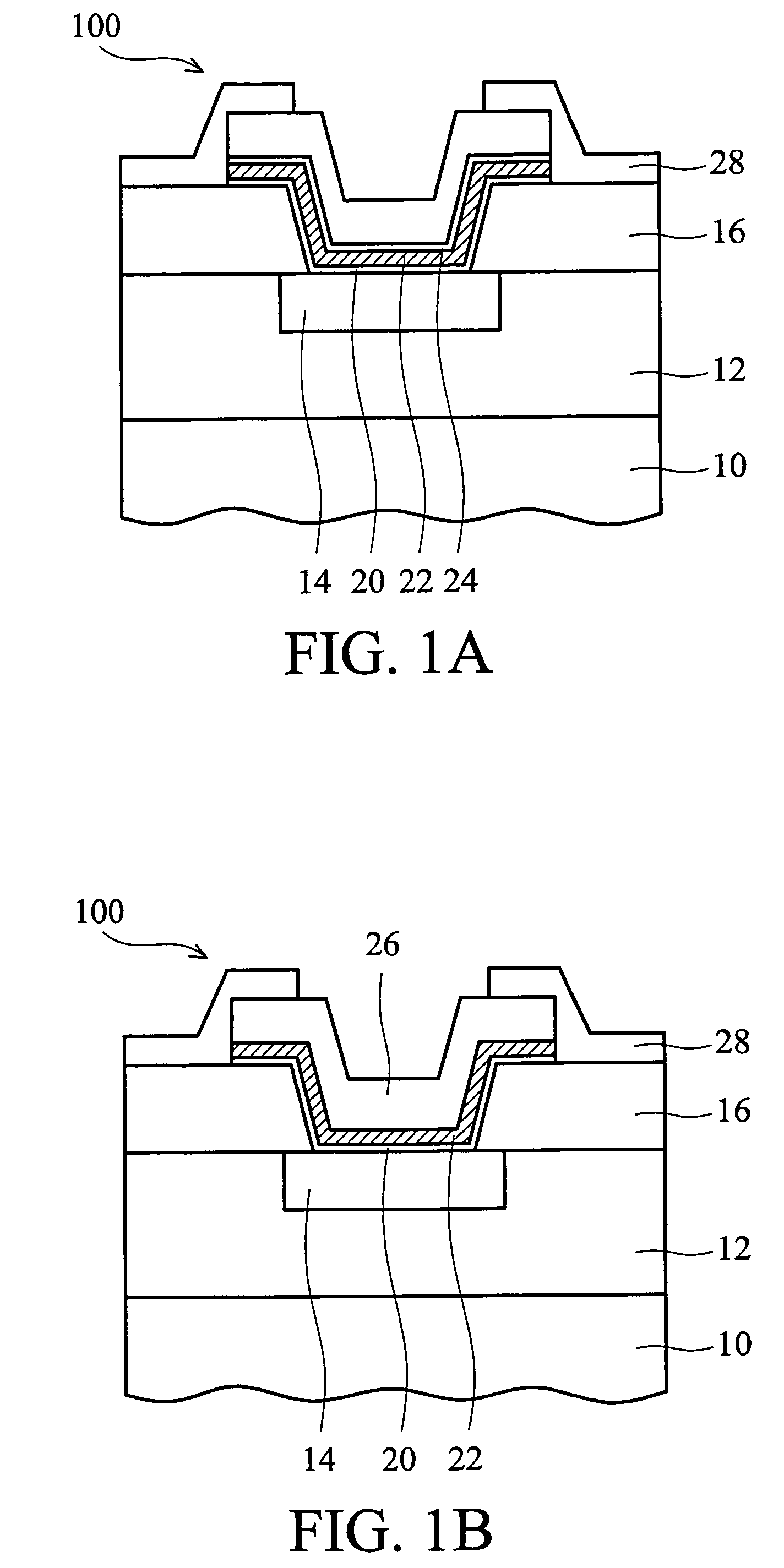

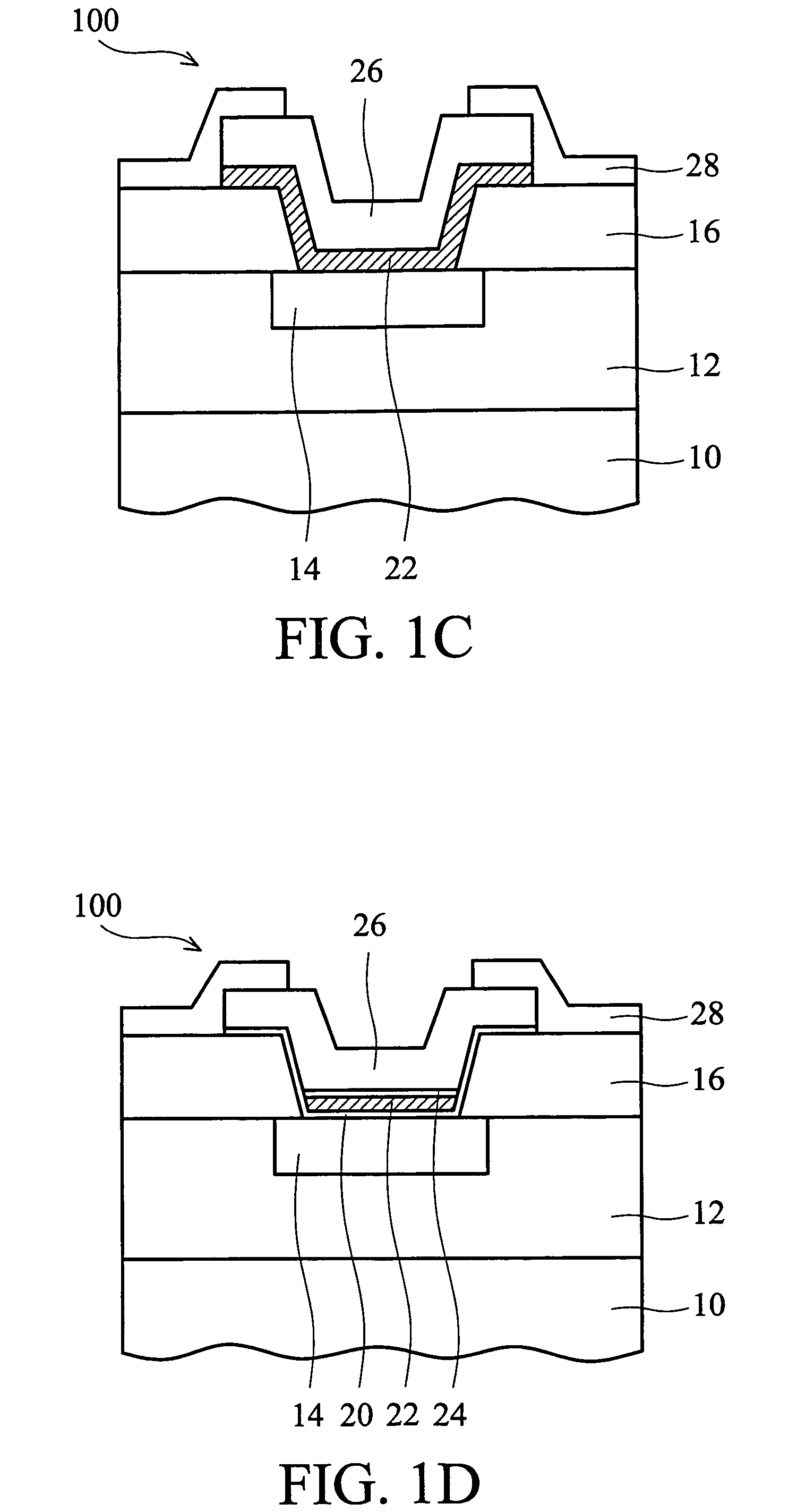

01 Bond pad structure with stress buffer layers

Implementation of stress buffer layers or compliant layers between the bond pad and underlying structures to absorb and distribute mechanical stress during wire bonding or flip-chip bonding processes. These buffer layers can include polymeric materials, low-k dielectrics, or specially designed metal layers that provide mechanical compliance while maintaining electrical connectivity. The stress buffer approach helps prevent crack propagation and delamination in the interconnect stack.- Bond pad structure with stress buffer layers: Implementing stress buffer layers or compliant layers between the bond pad and underlying structures can effectively reduce mechanical stress during wire bonding or flip-chip bonding processes. These buffer layers absorb and distribute stress, preventing crack propagation and delamination. Materials such as polymers, low-k dielectrics, or specially designed metal layers can serve as stress buffers to improve reliability.

- Multi-layer bond pad metallization design: Utilizing multi-layer metallization structures with optimized material combinations can enhance stress distribution and mechanical strength. The design typically involves stacking different metal layers with varying properties to balance electrical conductivity and mechanical robustness. This approach helps prevent pad cratering and improves adhesion between layers during bonding operations.

- Bond pad geometry and layout optimization: Optimizing the geometric design of bond pads, including size, shape, and spacing, can significantly reduce stress concentration points. Design considerations include rounded corners, optimized pad dimensions, and strategic placement relative to underlying circuit elements. Proper layout planning helps distribute mechanical forces more evenly across the pad structure.

- Passivation layer design for stress relief: Engineering passivation layers with specific openings, thicknesses, and material properties can provide stress relief around bond pad areas. The passivation design includes controlled opening sizes and shapes that minimize stress concentration while maintaining protection for underlying circuits. Advanced designs may incorporate multiple passivation layers with different mechanical properties.

- Under-pad structure reinforcement: Strengthening the structures beneath bond pads through reinforced dielectric layers, metal redistribution patterns, or specialized support structures can improve stress resistance. These reinforcement techniques prevent substrate damage and crack formation during bonding processes. The under-pad design may include dummy metal fills, via arrangements, or strengthened inter-layer dielectric structures.

02 Multi-layer bond pad metallization design

Design of bond pads using multiple metal layers with optimized thickness ratios and material combinations to manage stress distribution. This approach involves strategic placement of different metal materials such as aluminum, copper, and barrier metals in a stacked configuration. The multi-layer structure provides improved adhesion, reduced stress concentration at interfaces, and enhanced reliability during thermal cycling and mechanical loading.Expand Specific Solutions03 Bond pad geometry and layout optimization

Optimization of bond pad shape, size, and peripheral layout features to minimize stress concentration points. This includes the use of rounded corners, tapered edges, stress relief slots, and optimized pad-to-pad spacing. The geometric design considerations also encompass the arrangement of underlying via structures and metal routing to distribute mechanical forces more uniformly across the pad area and prevent localized stress buildup.Expand Specific Solutions04 Passivation layer design for stress management

Engineering of passivation and protective layers over and around bond pads to control stress transfer and provide mechanical reinforcement. This involves careful selection of passivation materials, control of layer thickness, and design of openings that expose the bond pad while managing stress at the passivation edge. Advanced designs may include graded composition layers or multiple passivation materials to create stress transition zones.Expand Specific Solutions05 Under-pad structure reinforcement

Strengthening of the dielectric and metal structures beneath the bond pad to provide mechanical support and prevent substrate damage. This includes the use of reinforced via arrays, solid metal planes, or dense interconnect structures under the pad area. The reinforcement approach helps distribute bonding forces into the substrate and prevents cracking of low-k dielectric materials or inter-layer dielectric structures during the bonding process.Expand Specific Solutions

Key Players in Semiconductor Packaging Industry

The bond pad design optimization for stress reduction in chip packaging represents a mature yet evolving segment within the broader semiconductor industry, which has reached a consolidated growth phase with established market leaders driving innovation. The global semiconductor packaging market, valued at approximately $30 billion, continues expanding driven by miniaturization demands and advanced packaging requirements. Technology maturity varies significantly across market participants, with industry giants like Taiwan Semiconductor Manufacturing Co., Samsung Electronics, and SK Hynix leading advanced packaging innovations through substantial R&D investments. Foundries such as GLOBALFOUNDRIES and specialized assembly providers like Advanced Semiconductor Engineering demonstrate high technical capabilities in stress-optimized designs. Memory manufacturers including Micron Technology and ChangXin Memory Technologies focus on package-specific stress solutions, while integrated device manufacturers like Texas Instruments, Analog Devices, and Infineon Technologies leverage their vertical integration for comprehensive optimization approaches, creating a competitive landscape where technological differentiation increasingly determines market positioning.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC employs advanced bond pad design optimization techniques including copper pillar bumping technology and through-silicon via (TSV) integration to minimize mechanical stress during packaging. Their approach utilizes finite element analysis (FEA) modeling to predict stress distribution patterns and optimize pad placement geometry. The company implements multi-layer redistribution layers (RDL) with optimized trace routing to reduce current density hotspots and thermal-induced stress. TSMC's CoWoS (Chip-on-Wafer-on-Substrate) technology incorporates stress-relief structures around bond pads, including polymer underfill materials and flexible interconnect designs that accommodate thermal expansion mismatches between different materials in the package stack.

Strengths: Industry-leading process technology and extensive R&D capabilities in advanced packaging. Weaknesses: High development costs and complex manufacturing processes requiring specialized equipment.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung develops bond pad stress reduction solutions through their advanced packaging portfolio including Fan-Out Wafer Level Packaging (FOWLP) and 2.5D/3D integration technologies. Their methodology focuses on optimizing pad metallization stack composition using low-stress materials such as aluminum-copper alloys with barrier layers to prevent electromigration. Samsung implements adaptive pad sizing algorithms that adjust bond pad dimensions based on current carrying requirements and thermal cycling conditions. The company utilizes machine learning-driven design optimization tools to predict stress concentration points and automatically generate pad layouts that minimize peak stress values while maintaining electrical performance specifications.

Strengths: Strong integration capabilities across memory and logic technologies with comprehensive packaging solutions. Weaknesses: Limited third-party foundry services compared to pure-play foundries, potentially restricting market reach.

Core Innovations in Bond Pad Stress Optimization

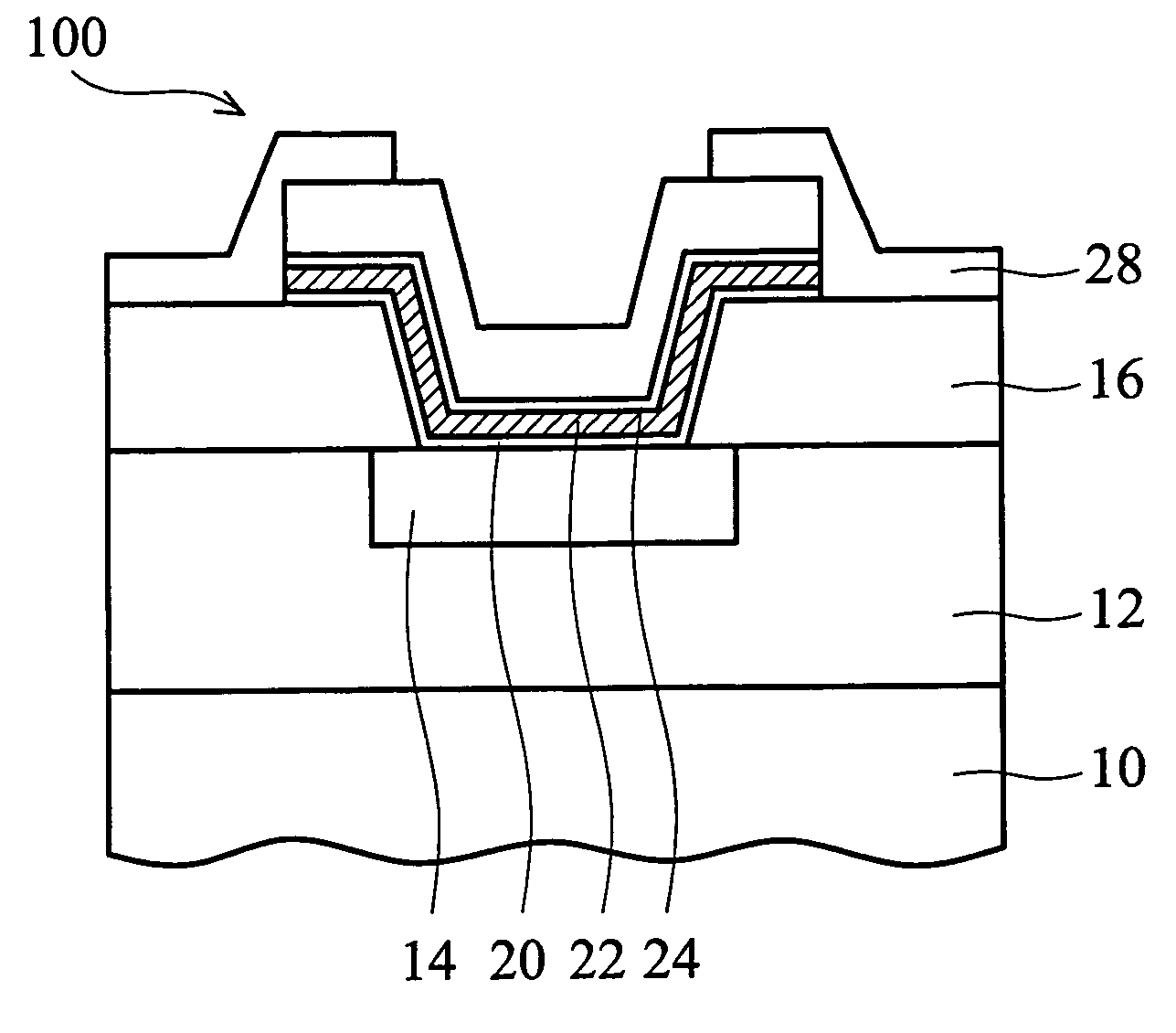

Bond pad structure with stress-buffering layer capping interconnection metal layer

PatentInactiveUS7741714B2

Innovation

- A bond pad structure with a stress-buffering layer having greater Young's modulus, hardness, strength, or toughness than the underlying metal layers, typically using tungsten, is introduced between the top interconnection metal layer and the bond pad layer to absorb mechanical stresses.

Bond pad design for improved routing and reduced package stress

PatentActiveUS20120326336A1

Innovation

- The proposed bond pad design features elongated shapes with a wide portion and a narrow portion, allowing for increased spacing between pads for more routing lines and improved stress distribution by orienting the elongated portions along stress directions radiating from the center to the chip's periphery, thereby reducing delamination risk.

Semiconductor Manufacturing Standards and Compliance

The semiconductor industry operates under stringent manufacturing standards that directly impact bond pad design optimization for stress reduction. International standards such as JEDEC (Joint Electron Device Engineering Council) specifications provide comprehensive guidelines for package-level stress testing and reliability assessment. JEDEC standards JESD22-B110 and JESD22-B111 specifically address subassembly mechanical shock and vibration testing, which are crucial for validating bond pad designs under mechanical stress conditions.

ISO 9001 quality management systems and AS9100 aerospace standards mandate rigorous documentation and traceability requirements for bond pad design modifications. These standards require comprehensive design validation protocols, including finite element analysis documentation, stress simulation reports, and reliability test data. Compliance with these standards ensures that optimized bond pad designs meet industry-accepted reliability criteria and can withstand specified mechanical and thermal stress levels.

IPC standards, particularly IPC-2221 and IPC-6012, establish design rules for conductor spacing, pad dimensions, and material specifications that directly influence stress distribution in packaging applications. These standards define minimum annular ring requirements, via-in-pad specifications, and copper thickness tolerances that affect bond pad mechanical integrity. Adherence to IPC guidelines ensures compatibility with standard assembly processes while maintaining stress reduction objectives.

Military and automotive standards such as MIL-STD-883 and AEC-Q100 impose additional constraints on bond pad design optimization. These standards require extended temperature cycling, mechanical shock testing, and long-term reliability validation that must be incorporated into the design optimization process. Compliance testing protocols under these standards often reveal stress concentration points that require iterative design refinement.

Regulatory compliance frameworks in different geographical regions, including CE marking in Europe, FCC certification in North America, and CCC certification in China, establish electromagnetic compatibility and safety requirements that can influence bond pad layout and grounding strategies. These regulations may impose constraints on pad placement and routing that must be balanced against stress reduction objectives during the optimization process.

ISO 9001 quality management systems and AS9100 aerospace standards mandate rigorous documentation and traceability requirements for bond pad design modifications. These standards require comprehensive design validation protocols, including finite element analysis documentation, stress simulation reports, and reliability test data. Compliance with these standards ensures that optimized bond pad designs meet industry-accepted reliability criteria and can withstand specified mechanical and thermal stress levels.

IPC standards, particularly IPC-2221 and IPC-6012, establish design rules for conductor spacing, pad dimensions, and material specifications that directly influence stress distribution in packaging applications. These standards define minimum annular ring requirements, via-in-pad specifications, and copper thickness tolerances that affect bond pad mechanical integrity. Adherence to IPC guidelines ensures compatibility with standard assembly processes while maintaining stress reduction objectives.

Military and automotive standards such as MIL-STD-883 and AEC-Q100 impose additional constraints on bond pad design optimization. These standards require extended temperature cycling, mechanical shock testing, and long-term reliability validation that must be incorporated into the design optimization process. Compliance testing protocols under these standards often reveal stress concentration points that require iterative design refinement.

Regulatory compliance frameworks in different geographical regions, including CE marking in Europe, FCC certification in North America, and CCC certification in China, establish electromagnetic compatibility and safety requirements that can influence bond pad layout and grounding strategies. These regulations may impose constraints on pad placement and routing that must be balanced against stress reduction objectives during the optimization process.

Reliability Testing Methods for Bond Pad Performance

Reliability testing methods for bond pad performance encompass a comprehensive suite of evaluation techniques designed to assess the long-term durability and functionality of bond pad structures under various stress conditions. These testing methodologies are critical for validating design optimizations and ensuring that stress reduction measures effectively translate into improved package reliability.

Thermal cycling tests represent one of the most fundamental reliability assessment methods, subjecting bond pads to repeated temperature fluctuations that simulate real-world operating conditions. These tests typically involve cycling between extreme temperatures ranging from -65°C to 150°C, with dwell times and ramp rates carefully controlled to induce thermal stress. The evaluation focuses on monitoring bond pad adhesion, metallization integrity, and the formation of intermetallic compounds that could compromise electrical connectivity.

Wire bond pull and shear tests provide quantitative measurements of mechanical bond strength, directly correlating with the effectiveness of stress reduction design features. Pull tests apply vertical force to bonded wires until failure occurs, while shear tests apply horizontal force to assess bond pad adhesion to the underlying substrate. These tests are performed both before and after thermal cycling to evaluate degradation patterns and establish reliability margins.

High-temperature storage testing exposes bond pads to elevated temperatures for extended periods, typically 150°C to 200°C for 500 to 1000 hours. This accelerated aging process reveals potential failure mechanisms related to metallization migration, oxidation, and thermal stress accumulation. The testing protocol includes periodic electrical measurements to monitor resistance changes and visual inspection for physical degradation signs.

Humidity and temperature bias testing combines elevated temperature and humidity conditions with applied electrical bias to simulate harsh environmental exposure. This method is particularly effective for identifying corrosion-related failure modes and evaluating the effectiveness of passivation layers in protecting bond pad structures from moisture ingress.

Advanced characterization techniques such as scanning electron microscopy and focused ion beam analysis provide detailed failure mode analysis, enabling correlation between observed degradation patterns and specific design parameters. These methods support the validation of stress reduction strategies by providing microscopic evidence of their effectiveness in preventing common failure mechanisms.

Thermal cycling tests represent one of the most fundamental reliability assessment methods, subjecting bond pads to repeated temperature fluctuations that simulate real-world operating conditions. These tests typically involve cycling between extreme temperatures ranging from -65°C to 150°C, with dwell times and ramp rates carefully controlled to induce thermal stress. The evaluation focuses on monitoring bond pad adhesion, metallization integrity, and the formation of intermetallic compounds that could compromise electrical connectivity.

Wire bond pull and shear tests provide quantitative measurements of mechanical bond strength, directly correlating with the effectiveness of stress reduction design features. Pull tests apply vertical force to bonded wires until failure occurs, while shear tests apply horizontal force to assess bond pad adhesion to the underlying substrate. These tests are performed both before and after thermal cycling to evaluate degradation patterns and establish reliability margins.

High-temperature storage testing exposes bond pads to elevated temperatures for extended periods, typically 150°C to 200°C for 500 to 1000 hours. This accelerated aging process reveals potential failure mechanisms related to metallization migration, oxidation, and thermal stress accumulation. The testing protocol includes periodic electrical measurements to monitor resistance changes and visual inspection for physical degradation signs.

Humidity and temperature bias testing combines elevated temperature and humidity conditions with applied electrical bias to simulate harsh environmental exposure. This method is particularly effective for identifying corrosion-related failure modes and evaluating the effectiveness of passivation layers in protecting bond pad structures from moisture ingress.

Advanced characterization techniques such as scanning electron microscopy and focused ion beam analysis provide detailed failure mode analysis, enabling correlation between observed degradation patterns and specific design parameters. These methods support the validation of stress reduction strategies by providing microscopic evidence of their effectiveness in preventing common failure mechanisms.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!