Comparing Oscillator Power Needs: CMOS vs BiCMOS

MAR 13, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

CMOS vs BiCMOS Oscillator Power Background and Objectives

The semiconductor industry has witnessed continuous evolution in integrated circuit technologies, with CMOS and BiCMOS representing two fundamental approaches to circuit design. CMOS technology, utilizing complementary metal-oxide-semiconductor structures, emerged as the dominant force in digital applications due to its inherently low static power consumption and high integration density. BiCMOS technology combines the advantages of both bipolar and CMOS transistors on a single substrate, offering enhanced performance characteristics for specific applications requiring high-speed operation and superior analog performance.

Oscillator circuits serve as critical timing references in virtually all electronic systems, from simple microcontrollers to complex communication infrastructure. The power consumption characteristics of these timing circuits directly impact overall system efficiency, battery life in portable devices, and thermal management requirements in high-performance applications. As electronic systems become increasingly power-conscious and performance-demanding, understanding the fundamental differences in power requirements between CMOS and BiCMOS oscillator implementations becomes essential for optimal design decisions.

The historical development of oscillator technologies has been closely tied to the evolution of semiconductor processes. Early oscillator designs relied heavily on bipolar transistors, which provided excellent frequency stability and low phase noise but consumed significant static power. The introduction of CMOS technology revolutionized low-power oscillator design, enabling battery-operated devices and reducing overall system power budgets. BiCMOS technology emerged as a hybrid solution, attempting to capture the performance benefits of bipolar devices while maintaining some of the power advantages of CMOS implementations.

Contemporary electronic systems face increasingly stringent power efficiency requirements driven by environmental concerns, regulatory standards, and market demands for extended battery life. Simultaneously, performance requirements continue to escalate, with applications demanding higher frequencies, lower jitter, and improved spectral purity from oscillator circuits. This creates a fundamental tension between power consumption and performance that must be carefully balanced through appropriate technology selection.

The primary objective of this comparative analysis is to establish a comprehensive understanding of power consumption characteristics inherent to CMOS and BiCMOS oscillator implementations across various operating conditions and performance requirements. This investigation aims to quantify the trade-offs between power efficiency and performance metrics, providing actionable insights for technology selection in different application contexts and establishing guidelines for optimizing oscillator power consumption while meeting specific performance criteria.

Oscillator circuits serve as critical timing references in virtually all electronic systems, from simple microcontrollers to complex communication infrastructure. The power consumption characteristics of these timing circuits directly impact overall system efficiency, battery life in portable devices, and thermal management requirements in high-performance applications. As electronic systems become increasingly power-conscious and performance-demanding, understanding the fundamental differences in power requirements between CMOS and BiCMOS oscillator implementations becomes essential for optimal design decisions.

The historical development of oscillator technologies has been closely tied to the evolution of semiconductor processes. Early oscillator designs relied heavily on bipolar transistors, which provided excellent frequency stability and low phase noise but consumed significant static power. The introduction of CMOS technology revolutionized low-power oscillator design, enabling battery-operated devices and reducing overall system power budgets. BiCMOS technology emerged as a hybrid solution, attempting to capture the performance benefits of bipolar devices while maintaining some of the power advantages of CMOS implementations.

Contemporary electronic systems face increasingly stringent power efficiency requirements driven by environmental concerns, regulatory standards, and market demands for extended battery life. Simultaneously, performance requirements continue to escalate, with applications demanding higher frequencies, lower jitter, and improved spectral purity from oscillator circuits. This creates a fundamental tension between power consumption and performance that must be carefully balanced through appropriate technology selection.

The primary objective of this comparative analysis is to establish a comprehensive understanding of power consumption characteristics inherent to CMOS and BiCMOS oscillator implementations across various operating conditions and performance requirements. This investigation aims to quantify the trade-offs between power efficiency and performance metrics, providing actionable insights for technology selection in different application contexts and establishing guidelines for optimizing oscillator power consumption while meeting specific performance criteria.

Market Demand for Low-Power Oscillator Solutions

The global electronics industry is experiencing unprecedented demand for low-power oscillator solutions, driven by the proliferation of battery-powered devices and stringent energy efficiency requirements. Mobile devices, wearable technology, and Internet of Things applications represent the largest market segments demanding ultra-low power consumption. These applications require oscillators that can maintain precise timing while consuming minimal current, particularly during standby modes where devices spend the majority of their operational time.

Automotive electronics constitute another rapidly expanding market segment for low-power oscillators. Advanced driver assistance systems, infotainment units, and electric vehicle control systems require reliable timing solutions that minimize power drain on vehicle batteries. The automotive sector's shift toward electrification has intensified focus on power efficiency across all electronic components, creating substantial opportunities for optimized oscillator technologies.

Industrial automation and smart manufacturing applications increasingly demand low-power timing solutions for distributed sensor networks and wireless monitoring systems. These applications often operate in remote locations where power availability is limited, making energy-efficient oscillators critical for extended operational periods. The growing adoption of Industry 4.0 technologies continues to expand this market segment significantly.

Healthcare and medical device markets present unique requirements for low-power oscillators, particularly in implantable devices and portable diagnostic equipment. Regulatory standards in medical applications demand exceptional reliability while maintaining minimal power consumption to extend battery life and reduce patient intervention requirements. This sector values precision timing solutions that can operate continuously for years without maintenance.

Consumer electronics manufacturers face increasing pressure to extend battery life while maintaining device performance. Smartphones, tablets, and smart home devices require oscillators that can dynamically adjust power consumption based on operational modes. The competitive landscape in consumer electronics drives continuous innovation in power-efficient timing solutions.

The telecommunications infrastructure sector requires low-power oscillators for base stations, small cells, and network equipment where operational costs directly correlate with power consumption. Energy efficiency regulations and sustainability initiatives in telecommunications create strong market pull for advanced low-power timing technologies.

Market growth is further accelerated by emerging applications in edge computing, where distributed processing nodes require precise timing with minimal power overhead. The convergence of artificial intelligence and edge computing creates new opportunities for specialized low-power oscillator solutions that can support high-performance computing while maintaining energy efficiency constraints.

Automotive electronics constitute another rapidly expanding market segment for low-power oscillators. Advanced driver assistance systems, infotainment units, and electric vehicle control systems require reliable timing solutions that minimize power drain on vehicle batteries. The automotive sector's shift toward electrification has intensified focus on power efficiency across all electronic components, creating substantial opportunities for optimized oscillator technologies.

Industrial automation and smart manufacturing applications increasingly demand low-power timing solutions for distributed sensor networks and wireless monitoring systems. These applications often operate in remote locations where power availability is limited, making energy-efficient oscillators critical for extended operational periods. The growing adoption of Industry 4.0 technologies continues to expand this market segment significantly.

Healthcare and medical device markets present unique requirements for low-power oscillators, particularly in implantable devices and portable diagnostic equipment. Regulatory standards in medical applications demand exceptional reliability while maintaining minimal power consumption to extend battery life and reduce patient intervention requirements. This sector values precision timing solutions that can operate continuously for years without maintenance.

Consumer electronics manufacturers face increasing pressure to extend battery life while maintaining device performance. Smartphones, tablets, and smart home devices require oscillators that can dynamically adjust power consumption based on operational modes. The competitive landscape in consumer electronics drives continuous innovation in power-efficient timing solutions.

The telecommunications infrastructure sector requires low-power oscillators for base stations, small cells, and network equipment where operational costs directly correlate with power consumption. Energy efficiency regulations and sustainability initiatives in telecommunications create strong market pull for advanced low-power timing technologies.

Market growth is further accelerated by emerging applications in edge computing, where distributed processing nodes require precise timing with minimal power overhead. The convergence of artificial intelligence and edge computing creates new opportunities for specialized low-power oscillator solutions that can support high-performance computing while maintaining energy efficiency constraints.

Current Power Consumption Challenges in CMOS and BiCMOS

Power consumption challenges in CMOS and BiCMOS oscillator circuits represent one of the most critical design constraints in modern integrated circuit development. As operating frequencies continue to increase and supply voltages scale down with advanced process nodes, maintaining stable oscillation while minimizing power dissipation has become increasingly complex. The fundamental trade-off between power consumption, phase noise performance, and frequency stability creates a multifaceted optimization problem that affects both circuit topology selection and process technology choices.

CMOS oscillators face significant challenges related to their inherently higher transconductance requirements for maintaining oscillation at high frequencies. The need for larger transistor sizes to achieve adequate gain-bandwidth product directly translates to increased parasitic capacitances and higher dynamic power consumption. Additionally, CMOS circuits typically require higher bias currents to overcome process variations and maintain consistent oscillation amplitude across temperature and supply voltage variations, leading to elevated static power dissipation.

BiCMOS technology introduces different power consumption dynamics through the integration of bipolar junction transistors with CMOS devices. While bipolar transistors offer superior transconductance efficiency and lower flicker noise, they inherently consume more static power due to base current requirements and higher collector-emitter saturation voltages. The challenge lies in optimizing the bias point to achieve the desired oscillation characteristics while managing the increased quiescent current consumption typical of bipolar devices.

Process scaling effects compound these challenges differently for each technology. In advanced CMOS nodes, reduced supply voltages limit the available voltage headroom for oscillator circuits, forcing designers to operate closer to threshold voltages where process variations have more pronounced effects on power consumption. Leakage currents also become more significant contributors to total power dissipation, particularly in applications requiring extended battery life or standby operation modes.

Temperature dependency presents another critical challenge affecting power consumption in both technologies. CMOS oscillators exhibit strong temperature coefficients that often require compensation circuits, adding to overall power overhead. BiCMOS circuits, while offering better temperature stability in some aspects, face challenges related to thermal coupling between bipolar and CMOS sections, potentially leading to thermal runaway conditions if not properly managed.

The emergence of ultra-low-power applications has intensified focus on subthreshold operation and duty-cycling techniques, creating new challenges in maintaining oscillation quality while operating at extremely low power levels. These constraints particularly affect frequency accuracy and startup reliability, requiring innovative circuit techniques and careful technology selection to achieve acceptable performance within stringent power budgets.

CMOS oscillators face significant challenges related to their inherently higher transconductance requirements for maintaining oscillation at high frequencies. The need for larger transistor sizes to achieve adequate gain-bandwidth product directly translates to increased parasitic capacitances and higher dynamic power consumption. Additionally, CMOS circuits typically require higher bias currents to overcome process variations and maintain consistent oscillation amplitude across temperature and supply voltage variations, leading to elevated static power dissipation.

BiCMOS technology introduces different power consumption dynamics through the integration of bipolar junction transistors with CMOS devices. While bipolar transistors offer superior transconductance efficiency and lower flicker noise, they inherently consume more static power due to base current requirements and higher collector-emitter saturation voltages. The challenge lies in optimizing the bias point to achieve the desired oscillation characteristics while managing the increased quiescent current consumption typical of bipolar devices.

Process scaling effects compound these challenges differently for each technology. In advanced CMOS nodes, reduced supply voltages limit the available voltage headroom for oscillator circuits, forcing designers to operate closer to threshold voltages where process variations have more pronounced effects on power consumption. Leakage currents also become more significant contributors to total power dissipation, particularly in applications requiring extended battery life or standby operation modes.

Temperature dependency presents another critical challenge affecting power consumption in both technologies. CMOS oscillators exhibit strong temperature coefficients that often require compensation circuits, adding to overall power overhead. BiCMOS circuits, while offering better temperature stability in some aspects, face challenges related to thermal coupling between bipolar and CMOS sections, potentially leading to thermal runaway conditions if not properly managed.

The emergence of ultra-low-power applications has intensified focus on subthreshold operation and duty-cycling techniques, creating new challenges in maintaining oscillation quality while operating at extremely low power levels. These constraints particularly affect frequency accuracy and startup reliability, requiring innovative circuit techniques and careful technology selection to achieve acceptable performance within stringent power budgets.

Existing Power Reduction Solutions for Oscillators

01 Low-power oscillator circuit design techniques

Various circuit design techniques can be employed to reduce power consumption in oscillators. These include optimizing transistor sizing, using current-starved topologies, implementing duty-cycle control, and employing adaptive biasing schemes. Such techniques help minimize static and dynamic power dissipation while maintaining oscillation stability and frequency accuracy. Advanced design methodologies focus on reducing supply current and improving power efficiency across different operating conditions.- Low-power oscillator circuit design techniques: Various circuit design techniques can be employed to reduce power consumption in oscillators. These include optimizing transistor sizing, using current-starved topologies, implementing duty-cycle control, and employing adaptive biasing schemes. Such techniques help minimize static and dynamic power dissipation while maintaining oscillation stability and frequency accuracy. Advanced design methodologies focus on reducing supply voltage requirements and minimizing parasitic capacitances to achieve ultra-low power operation suitable for battery-powered and energy-harvesting applications.

- Power management and control circuits for oscillators: Power management circuits can be integrated with oscillators to dynamically control power consumption based on operational requirements. These circuits include power gating mechanisms, clock gating techniques, and intelligent duty-cycling schemes that enable the oscillator to operate in different power modes. Adaptive control systems can monitor operating conditions and adjust bias currents, supply voltages, or enable/disable oscillator sections to optimize power efficiency during different phases of operation.

- Temperature-compensated low-power oscillator designs: Temperature compensation techniques can be implemented in oscillator designs to maintain frequency stability while minimizing power consumption across varying temperature conditions. These approaches include using temperature-dependent bias circuits, compensation networks, and calibration schemes that adjust oscillator parameters based on temperature variations. By maintaining stable operation without requiring excessive power margins, these designs achieve both accuracy and energy efficiency in temperature-varying environments.

- Crystal and resonator-based low-power oscillator architectures: Oscillator architectures utilizing crystal resonators or MEMS resonators can achieve low power consumption through optimized drive level control and efficient coupling circuits. These designs minimize the power required to sustain oscillation by carefully controlling the energy delivered to the resonator and implementing high-efficiency amplification stages. Techniques include automatic gain control, negative resistance optimization, and impedance matching to reduce power dissipation while ensuring reliable startup and stable operation.

- Digital and hybrid oscillator implementations for power reduction: Digital and hybrid oscillator implementations can provide significant power savings compared to traditional analog designs. These approaches include digitally-controlled oscillators, ring oscillators with digital control, and hybrid architectures combining analog and digital techniques. Power reduction is achieved through digital calibration, fine-grained frequency control, and the ability to scale supply voltage dynamically. Such implementations are particularly suitable for integration in modern CMOS processes and system-on-chip applications where power efficiency is critical.

02 Power management and control mechanisms for oscillators

Power management strategies involve implementing control circuits that can dynamically adjust oscillator operation based on system requirements. These mechanisms include power gating, clock gating, frequency scaling, and selective activation of oscillator components. By intelligently controlling when and how the oscillator operates, significant power savings can be achieved without compromising system performance. These approaches are particularly useful in battery-operated and energy-constrained applications.Expand Specific Solutions03 Ultra-low-power oscillator architectures

Specialized oscillator architectures are designed specifically for ultra-low-power applications. These architectures may utilize relaxation oscillators, ring oscillators with optimized stages, or crystal oscillators with minimal drive circuits. The designs focus on minimizing leakage current, reducing switching activity, and optimizing the trade-off between power consumption and performance metrics such as phase noise and frequency stability. Such architectures are essential for IoT devices and wearable electronics.Expand Specific Solutions04 Voltage-controlled and digitally-controlled oscillators with power optimization

Voltage-controlled oscillators and digitally-controlled oscillators can be designed with power optimization features that allow for efficient operation across varying frequency ranges. These designs incorporate techniques such as varactor optimization, reduced swing operation, and intelligent tuning mechanisms that minimize power consumption while maintaining frequency tuning capability. The power efficiency is achieved through careful design of control interfaces and tuning elements.Expand Specific Solutions05 Temperature-compensated and process-variation-tolerant low-power oscillators

Oscillator designs that incorporate temperature compensation and process variation tolerance can maintain low power consumption across different operating conditions and manufacturing variations. These designs use compensation circuits, trimming techniques, and adaptive calibration methods to ensure consistent power performance. By addressing environmental and process variations, these oscillators provide reliable low-power operation without requiring excessive design margins that would increase power consumption.Expand Specific Solutions

Key Players in CMOS and BiCMOS Oscillator Industry

The oscillator power comparison between CMOS and BiCMOS technologies represents a mature market segment within the broader semiconductor industry, which has reached a stable growth phase with established design methodologies and manufacturing processes. The global oscillator market, valued at several billion dollars, continues to expand driven by increasing demand for timing solutions in telecommunications, automotive, and IoT applications. Technology maturity varies significantly among key players, with industry leaders like Texas Instruments, Intel, Samsung Electronics, and Qualcomm demonstrating advanced capabilities in both CMOS and BiCMOS oscillator designs, while companies such as Infineon Technologies, NXP Semiconductors, and Nuvoton Technology focus on specialized power-efficient solutions. Asian manufacturers including Advanced Semiconductor Manufacturing Corp and Shanghai Huahong Grace represent emerging capabilities in foundry services, supporting the competitive landscape where power optimization remains a critical differentiator for next-generation applications.

Texas Instruments Incorporated

Technical Solution: Texas Instruments has developed comprehensive oscillator solutions utilizing both CMOS and BiCMOS technologies for power-sensitive applications. Their CMOS oscillators typically consume 50-200μA of current while providing frequency stability within ±25ppm over temperature ranges. For high-performance applications, TI's BiCMOS oscillators deliver superior phase noise performance at -140dBc/Hz at 10kHz offset but require 2-5mA operating current. The company has optimized power management through adaptive biasing circuits and sleep modes, reducing standby power to sub-microamp levels in CMOS variants while maintaining quick startup times under 10ms.

Strengths: Industry-leading power efficiency in CMOS designs, extensive product portfolio covering wide frequency ranges. Weaknesses: BiCMOS solutions have higher power consumption, limited integration options for ultra-low power applications.

Infineon Technologies AG

Technical Solution: Infineon has developed specialized oscillator solutions comparing CMOS and BiCMOS technologies for automotive and industrial applications. Their CMOS oscillators achieve 100-500μA current consumption with temperature coefficients below ±20ppm/°C across -40°C to +125°C ranges. For precision timing requirements, Infineon's BiCMOS oscillators provide phase noise performance of -145dBc/Hz at 1kHz offset but require 1-3mA operating current. The company has implemented advanced compensation techniques including temperature-dependent bias adjustment and process variation calibration to optimize power-performance trade-offs in both technologies.

Strengths: Robust performance across automotive temperature ranges, excellent long-term stability, comprehensive power optimization techniques. Weaknesses: Higher cost for BiCMOS solutions, limited frequency range options in ultra-low power CMOS variants.

Core Innovations in Low-Power Oscillator Design

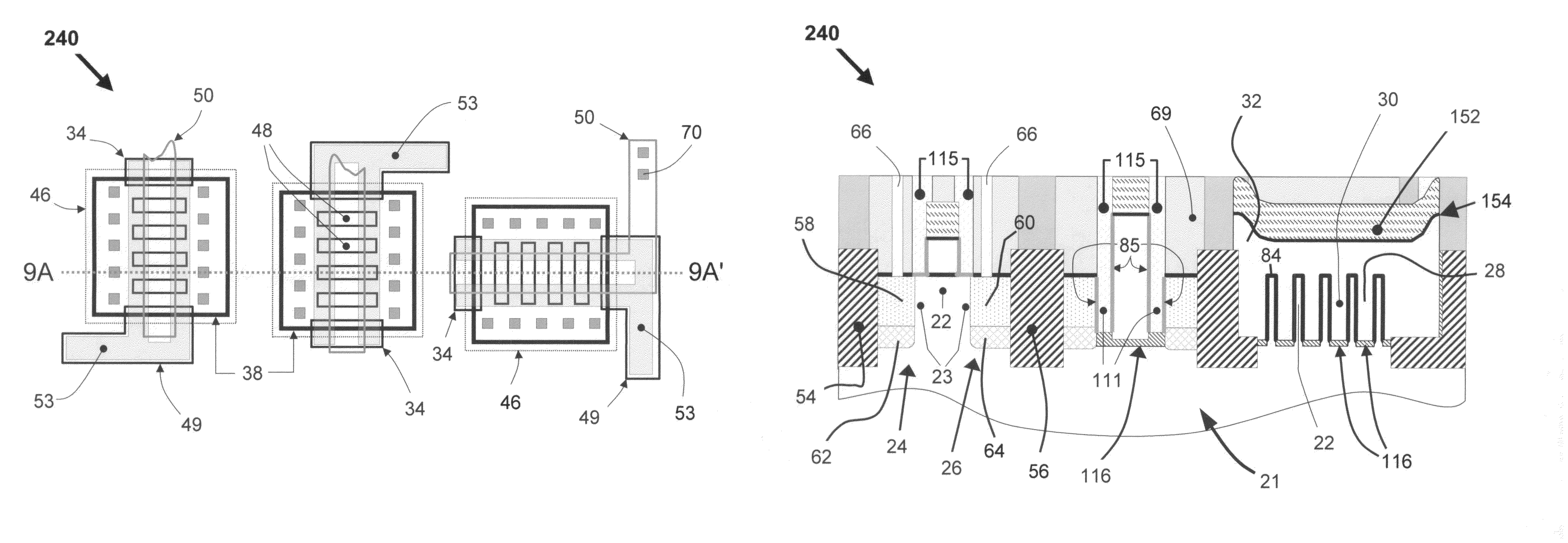

Efficient Fabrication of BiCMOS Devices

PatentActiveUS20150303186A1

Innovation

- A method involving the use of a common spacer layer and a spacer clear masking layer to define regions for forming sub-collectors and bases of bipolar devices, allowing for the selective implantation of dopants and deposition of silicon-germanium layers, thereby reducing the number of masking layers and processing steps.

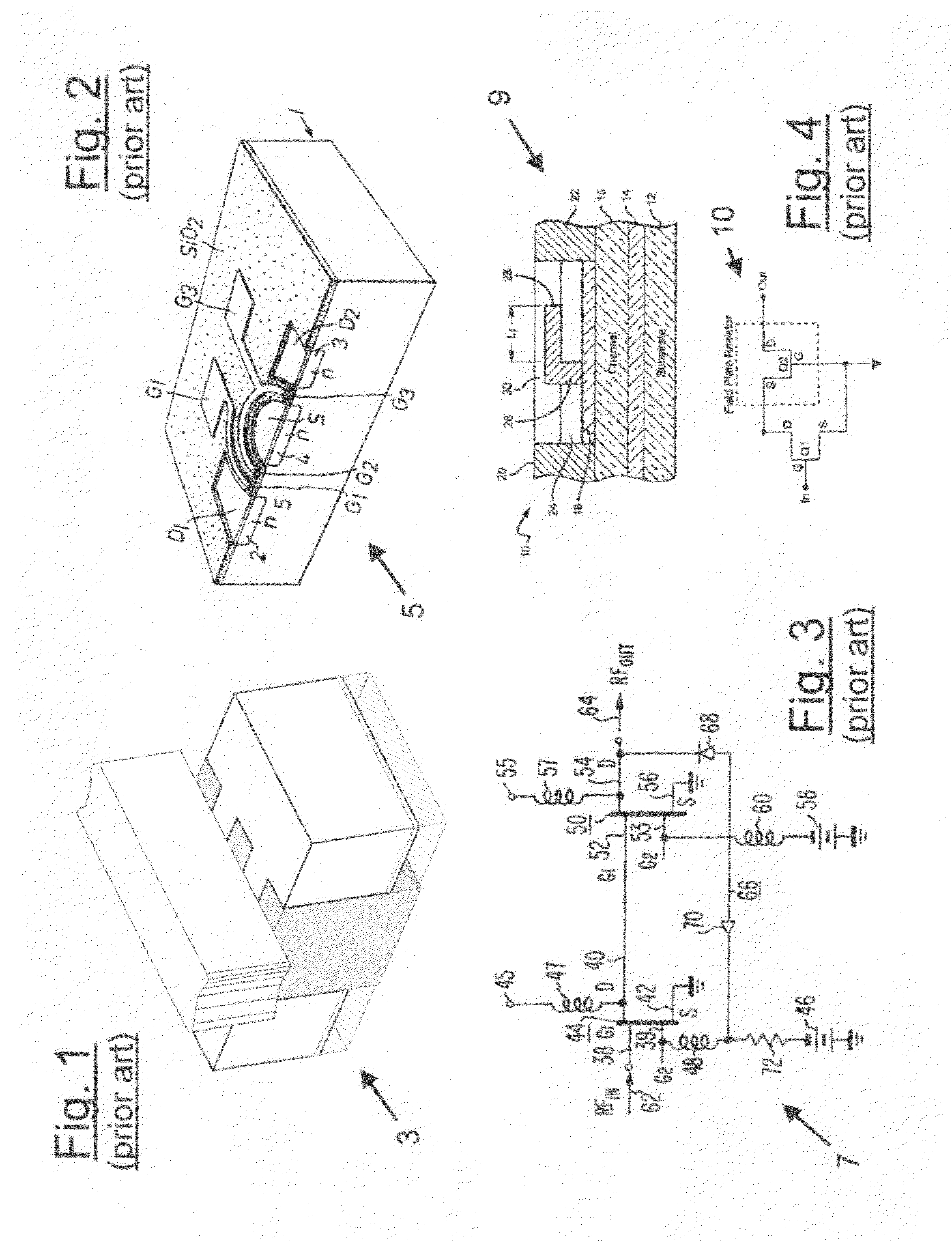

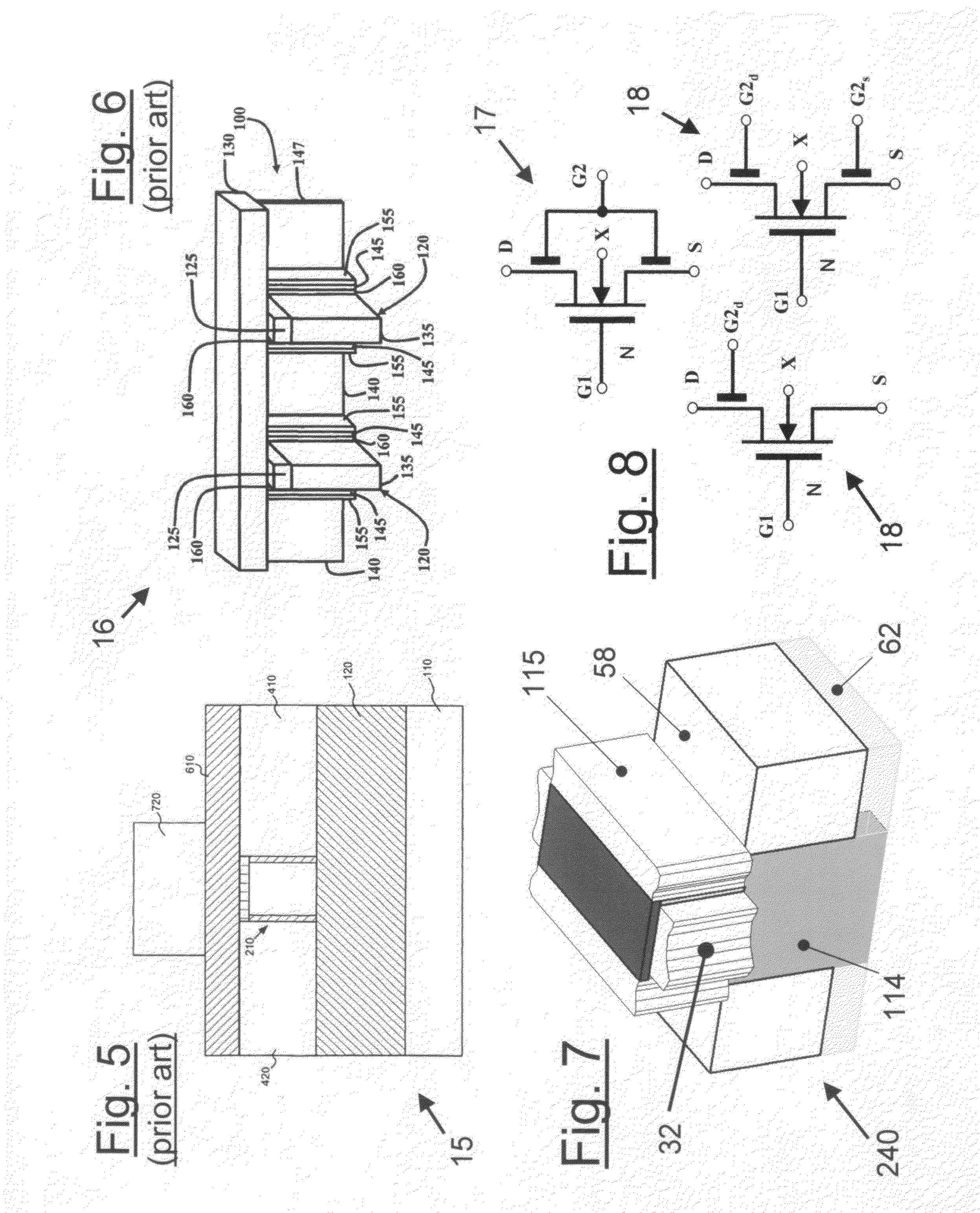

Castellated gate MOSFET tetrode capable of fully-depleted operation

PatentInactiveUS8138544B2

Innovation

- A castellated-gate MOSFET tetrode device is developed, featuring multiple gate structures and trench isolation insulator islands to create an integrated cascode configuration, allowing for fully depleted operation, increased drive current, tunable impedance, and reduced junction capacitance, while being compatible with various substrate types.

Process Technology Scaling Impact on Oscillator Power

Process technology scaling has fundamentally transformed oscillator power consumption patterns across both CMOS and BiCMOS implementations over the past several decades. The continuous miniaturization of semiconductor processes, following Moore's Law trajectory from micron-scale nodes to current sub-10nm technologies, has created distinct power scaling behaviors that affect these two process families differently.

In CMOS oscillators, technology scaling has generally favored power reduction through decreased supply voltages and reduced parasitic capacitances. As process nodes shrink from 180nm to 28nm and beyond, CMOS oscillators benefit from lower switching energy per transition due to reduced gate capacitances and shorter interconnect lengths. The quadratic relationship between supply voltage and dynamic power consumption becomes particularly advantageous as VDD scales from 3.3V in older processes to 1.0V or lower in advanced nodes.

BiCMOS oscillators exhibit more complex scaling behavior due to their hybrid nature combining bipolar and CMOS elements. While the CMOS portions benefit from similar scaling advantages, the bipolar components maintain relatively constant current requirements regardless of process scaling. This creates a scaling asymmetry where BiCMOS power reduction benefits diminish compared to pure CMOS implementations as technology nodes advance.

Advanced process nodes below 65nm introduce new challenges that affect both technologies differently. Increased leakage currents due to thinner gate oxides and shorter channel lengths impact CMOS oscillators more significantly, as static power consumption becomes a larger fraction of total power. BiCMOS circuits, already dominated by bipolar current consumption, show less relative impact from increased leakage.

The introduction of high-k metal gate technologies and FinFET structures in sub-32nm processes has created new optimization opportunities. CMOS oscillators can leverage improved gate control and reduced short-channel effects to maintain performance while further reducing power. BiCMOS implementations gain less benefit from these structural improvements, as bipolar device characteristics remain largely unchanged.

Process scaling also affects oscillator frequency capabilities and power efficiency trade-offs. Advanced CMOS processes enable higher frequency operation with proportionally lower power consumption, while BiCMOS maintains superior phase noise performance but with diminishing power scaling benefits. This divergence becomes more pronounced as process technology continues advancing toward 5nm and 3nm nodes.

In CMOS oscillators, technology scaling has generally favored power reduction through decreased supply voltages and reduced parasitic capacitances. As process nodes shrink from 180nm to 28nm and beyond, CMOS oscillators benefit from lower switching energy per transition due to reduced gate capacitances and shorter interconnect lengths. The quadratic relationship between supply voltage and dynamic power consumption becomes particularly advantageous as VDD scales from 3.3V in older processes to 1.0V or lower in advanced nodes.

BiCMOS oscillators exhibit more complex scaling behavior due to their hybrid nature combining bipolar and CMOS elements. While the CMOS portions benefit from similar scaling advantages, the bipolar components maintain relatively constant current requirements regardless of process scaling. This creates a scaling asymmetry where BiCMOS power reduction benefits diminish compared to pure CMOS implementations as technology nodes advance.

Advanced process nodes below 65nm introduce new challenges that affect both technologies differently. Increased leakage currents due to thinner gate oxides and shorter channel lengths impact CMOS oscillators more significantly, as static power consumption becomes a larger fraction of total power. BiCMOS circuits, already dominated by bipolar current consumption, show less relative impact from increased leakage.

The introduction of high-k metal gate technologies and FinFET structures in sub-32nm processes has created new optimization opportunities. CMOS oscillators can leverage improved gate control and reduced short-channel effects to maintain performance while further reducing power. BiCMOS implementations gain less benefit from these structural improvements, as bipolar device characteristics remain largely unchanged.

Process scaling also affects oscillator frequency capabilities and power efficiency trade-offs. Advanced CMOS processes enable higher frequency operation with proportionally lower power consumption, while BiCMOS maintains superior phase noise performance but with diminishing power scaling benefits. This divergence becomes more pronounced as process technology continues advancing toward 5nm and 3nm nodes.

Thermal Management Considerations for Oscillator Design

Thermal management represents a critical design consideration when comparing CMOS and BiCMOS oscillator architectures, as the power consumption differences between these technologies directly translate to distinct thermal challenges. The inherently lower power consumption of CMOS oscillators generates less heat dissipation, typically requiring minimal thermal management strategies for most applications. In contrast, BiCMOS oscillators, with their higher current consumption and bipolar transistor components, produce significantly more heat that must be effectively managed to maintain performance and reliability.

The thermal characteristics of CMOS oscillators benefit from their predominantly capacitive switching behavior, where power dissipation occurs primarily during state transitions. This results in relatively predictable thermal profiles that can be managed through standard PCB design practices, including appropriate ground plane sizing and via placement for heat spreading. The lower junction temperatures achieved in CMOS designs also contribute to improved long-term reliability and frequency stability.

BiCMOS oscillators present more complex thermal management requirements due to the continuous current flow in bipolar stages and higher overall power density. The bipolar components generate steady-state heat that requires active thermal dissipation strategies, particularly in high-frequency applications where power consumption scales significantly. Effective thermal design for BiCMOS oscillators often necessitates dedicated heat sinking, thermal vias, and careful consideration of component placement to prevent hot spots.

Package selection becomes crucial for both technologies, with thermal resistance from junction to ambient being a key parameter. CMOS oscillators can often utilize smaller, cost-effective packages due to their lower thermal requirements, while BiCMOS designs may require larger packages with enhanced thermal capabilities or exposed thermal pads to achieve adequate heat dissipation.

Temperature coefficient considerations also differ between the technologies, as BiCMOS circuits typically exhibit better temperature stability due to the compensating effects of bipolar and CMOS characteristics. However, this advantage must be weighed against the increased thermal management complexity and associated system costs, making thermal design a decisive factor in technology selection for temperature-sensitive applications.

The thermal characteristics of CMOS oscillators benefit from their predominantly capacitive switching behavior, where power dissipation occurs primarily during state transitions. This results in relatively predictable thermal profiles that can be managed through standard PCB design practices, including appropriate ground plane sizing and via placement for heat spreading. The lower junction temperatures achieved in CMOS designs also contribute to improved long-term reliability and frequency stability.

BiCMOS oscillators present more complex thermal management requirements due to the continuous current flow in bipolar stages and higher overall power density. The bipolar components generate steady-state heat that requires active thermal dissipation strategies, particularly in high-frequency applications where power consumption scales significantly. Effective thermal design for BiCMOS oscillators often necessitates dedicated heat sinking, thermal vias, and careful consideration of component placement to prevent hot spots.

Package selection becomes crucial for both technologies, with thermal resistance from junction to ambient being a key parameter. CMOS oscillators can often utilize smaller, cost-effective packages due to their lower thermal requirements, while BiCMOS designs may require larger packages with enhanced thermal capabilities or exposed thermal pads to achieve adequate heat dissipation.

Temperature coefficient considerations also differ between the technologies, as BiCMOS circuits typically exhibit better temperature stability due to the compensating effects of bipolar and CMOS characteristics. However, this advantage must be weighed against the increased thermal management complexity and associated system costs, making thermal design a decisive factor in technology selection for temperature-sensitive applications.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!