How LPDDR5X Reduces Standby Power While Preserving Wake-Up Latency?

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

LPDDR5X Power Efficiency Evolution and Objectives

Low-Power Double Data Rate (LPDDR) memory technology has undergone significant evolution since its inception, with each generation bringing substantial improvements in power efficiency while maintaining or enhancing performance. The LPDDR5X represents the latest milestone in this evolutionary journey, specifically designed to address the growing demands of mobile computing, artificial intelligence applications, and edge computing devices where power consumption is a critical constraint.

The development of LPDDR memory has consistently focused on reducing power consumption while increasing data transfer rates. LPDDR1 established the foundation for mobile memory solutions, while LPDDR2 and LPDDR3 progressively improved power efficiency through voltage scaling and enhanced signaling techniques. LPDDR4 marked a significant leap with the introduction of dual-channel architecture and lower operating voltages, reducing power consumption by approximately 40% compared to LPDDR3.

LPDDR5, introduced in 2019, further advanced power efficiency through innovations like Data Copy Operations and Link ECC, achieving up to 30% power reduction compared to LPDDR4X. The latest LPDDR5X standard, finalized in 2021, represents the culmination of these evolutionary efforts, with specific focus on optimizing standby power consumption while maintaining rapid wake-up capabilities.

The primary objective of LPDDR5X's power efficiency innovations is to address the "power paradox" faced by modern mobile and edge computing devices. These devices require both extended battery life during idle states and immediate responsiveness when activated. This necessitates memory that consumes minimal power during standby periods while maintaining the ability to transition to full operational capacity with minimal latency.

Specifically, LPDDR5X aims to reduce standby power consumption by at least 25% compared to LPDDR5, while ensuring wake-up latency remains under 100 nanoseconds. This balance is crucial for applications like smartphones, where extended standby time is essential, but users expect instant responsiveness when interacting with their devices.

Another key objective is to support the increasing memory demands of AI-powered applications at the edge, which require both high bandwidth for processing and extreme power efficiency to operate within thermal and battery constraints. LPDDR5X targets a 20% improvement in power efficiency during active AI workloads compared to previous generations.

The evolution of LPDDR5X also reflects the industry's broader commitment to sustainability, with objectives to reduce the overall carbon footprint of memory subsystems in billions of devices worldwide. By enabling more efficient operation across both active and standby states, LPDDR5X contributes to significant cumulative energy savings at global scale.

The development of LPDDR memory has consistently focused on reducing power consumption while increasing data transfer rates. LPDDR1 established the foundation for mobile memory solutions, while LPDDR2 and LPDDR3 progressively improved power efficiency through voltage scaling and enhanced signaling techniques. LPDDR4 marked a significant leap with the introduction of dual-channel architecture and lower operating voltages, reducing power consumption by approximately 40% compared to LPDDR3.

LPDDR5, introduced in 2019, further advanced power efficiency through innovations like Data Copy Operations and Link ECC, achieving up to 30% power reduction compared to LPDDR4X. The latest LPDDR5X standard, finalized in 2021, represents the culmination of these evolutionary efforts, with specific focus on optimizing standby power consumption while maintaining rapid wake-up capabilities.

The primary objective of LPDDR5X's power efficiency innovations is to address the "power paradox" faced by modern mobile and edge computing devices. These devices require both extended battery life during idle states and immediate responsiveness when activated. This necessitates memory that consumes minimal power during standby periods while maintaining the ability to transition to full operational capacity with minimal latency.

Specifically, LPDDR5X aims to reduce standby power consumption by at least 25% compared to LPDDR5, while ensuring wake-up latency remains under 100 nanoseconds. This balance is crucial for applications like smartphones, where extended standby time is essential, but users expect instant responsiveness when interacting with their devices.

Another key objective is to support the increasing memory demands of AI-powered applications at the edge, which require both high bandwidth for processing and extreme power efficiency to operate within thermal and battery constraints. LPDDR5X targets a 20% improvement in power efficiency during active AI workloads compared to previous generations.

The evolution of LPDDR5X also reflects the industry's broader commitment to sustainability, with objectives to reduce the overall carbon footprint of memory subsystems in billions of devices worldwide. By enabling more efficient operation across both active and standby states, LPDDR5X contributes to significant cumulative energy savings at global scale.

Market Demand for Low-Power Memory Solutions

The global demand for low-power memory solutions has experienced significant growth in recent years, driven primarily by the proliferation of mobile devices, IoT applications, and the increasing focus on energy efficiency across all computing platforms. Market research indicates that the low-power memory segment is expanding at a compound annual growth rate of approximately 15% between 2020 and 2025, outpacing the broader semiconductor memory market.

Mobile device manufacturers represent the largest consumer segment for low-power memory solutions, with smartphones and tablets accounting for nearly 60% of the total market share. These devices require memory components that can deliver high performance while minimizing battery drain, making LPDDR technologies particularly valuable in this space.

The emergence of 5G networks has further accelerated demand for advanced low-power memory solutions. The higher data rates and increased processing requirements of 5G-enabled devices necessitate memory systems that can handle greater bandwidth while maintaining power efficiency. Industry analysts project that 5G-compatible devices will represent over 70% of smartphone shipments by 2023, creating substantial market opportunities for next-generation memory technologies like LPDDR5X.

Enterprise data centers have also become significant consumers of low-power memory solutions as organizations prioritize energy efficiency to reduce operational costs and meet sustainability goals. The total cost of ownership calculations increasingly factor in power consumption, with memory subsystems representing 20-30% of server power usage in typical deployments.

Automotive applications represent another rapidly growing market segment, particularly with the advancement of autonomous driving technologies and in-vehicle infotainment systems. These applications demand memory solutions that combine low power consumption with high reliability and performance under varying environmental conditions.

Consumer expectations regarding device battery life continue to shape market requirements, with surveys indicating that battery performance remains among the top three purchasing considerations for mobile device consumers. This consumer pressure has translated into manufacturer specifications that increasingly emphasize standby power efficiency without compromising system responsiveness.

The market has also witnessed growing demand for memory solutions that can dynamically adjust power states based on workload requirements, allowing devices to optimize the balance between performance and energy consumption. This trend aligns perfectly with the capabilities of LPDDR5X, which offers sophisticated power management features while maintaining rapid wake-up times.

Mobile device manufacturers represent the largest consumer segment for low-power memory solutions, with smartphones and tablets accounting for nearly 60% of the total market share. These devices require memory components that can deliver high performance while minimizing battery drain, making LPDDR technologies particularly valuable in this space.

The emergence of 5G networks has further accelerated demand for advanced low-power memory solutions. The higher data rates and increased processing requirements of 5G-enabled devices necessitate memory systems that can handle greater bandwidth while maintaining power efficiency. Industry analysts project that 5G-compatible devices will represent over 70% of smartphone shipments by 2023, creating substantial market opportunities for next-generation memory technologies like LPDDR5X.

Enterprise data centers have also become significant consumers of low-power memory solutions as organizations prioritize energy efficiency to reduce operational costs and meet sustainability goals. The total cost of ownership calculations increasingly factor in power consumption, with memory subsystems representing 20-30% of server power usage in typical deployments.

Automotive applications represent another rapidly growing market segment, particularly with the advancement of autonomous driving technologies and in-vehicle infotainment systems. These applications demand memory solutions that combine low power consumption with high reliability and performance under varying environmental conditions.

Consumer expectations regarding device battery life continue to shape market requirements, with surveys indicating that battery performance remains among the top three purchasing considerations for mobile device consumers. This consumer pressure has translated into manufacturer specifications that increasingly emphasize standby power efficiency without compromising system responsiveness.

The market has also witnessed growing demand for memory solutions that can dynamically adjust power states based on workload requirements, allowing devices to optimize the balance between performance and energy consumption. This trend aligns perfectly with the capabilities of LPDDR5X, which offers sophisticated power management features while maintaining rapid wake-up times.

Current LPDDR5X Standby Power Challenges

Despite the significant advancements in LPDDR5X technology, standby power consumption remains a critical challenge for mobile and embedded system designers. Current LPDDR5X memory implementations face several power efficiency obstacles that must be addressed to meet the increasingly demanding requirements of modern battery-powered devices. The fundamental tension exists between maintaining low standby power consumption while simultaneously ensuring rapid wake-up response times.

One of the primary challenges is the leakage current in DRAM cells during standby mode. As process technologies continue to shrink, transistor leakage becomes more pronounced, contributing significantly to overall standby power consumption. This issue is particularly problematic in LPDDR5X, where the higher density and more complex architecture can lead to increased leakage paths compared to previous generations.

The refresh operations necessary to maintain data integrity represent another major power drain. LPDDR5X memory cells require periodic refresh to prevent data loss, and these operations consume substantial power even when the system is idle. Current implementations struggle to optimize refresh rates without compromising data integrity, especially across varying temperature conditions that affect charge leakage rates.

Power state transition management presents additional complications. The sophisticated power states in LPDDR5X (such as deep power-down, self-refresh, and partial array self-refresh) offer theoretical power savings, but the energy cost of transitioning between these states can sometimes outweigh the benefits for short idle periods. System designers face difficult decisions regarding when to trigger deeper power-saving states versus maintaining higher-power but more responsive states.

Voltage regulation inefficiencies further compound the standby power challenge. LPDDR5X requires precise voltage control across multiple power domains, and maintaining these voltage rails during standby conditions introduces conversion losses and regulation overhead that contribute to overall system power consumption.

The architectural complexity of modern memory subsystems also impacts standby power. With multiple channels, ranks, and banks in LPDDR5X configurations, selectively powering down unused sections while maintaining critical functionality requires sophisticated power management logic that itself consumes power and adds design complexity.

Temperature sensitivity represents yet another challenge, as LPDDR5X memory exhibits increased leakage at higher temperatures, creating a potential thermal runaway effect where increased temperature leads to higher power consumption, which in turn raises temperature further. This relationship necessitates dynamic power management approaches that can adapt to changing thermal conditions.

One of the primary challenges is the leakage current in DRAM cells during standby mode. As process technologies continue to shrink, transistor leakage becomes more pronounced, contributing significantly to overall standby power consumption. This issue is particularly problematic in LPDDR5X, where the higher density and more complex architecture can lead to increased leakage paths compared to previous generations.

The refresh operations necessary to maintain data integrity represent another major power drain. LPDDR5X memory cells require periodic refresh to prevent data loss, and these operations consume substantial power even when the system is idle. Current implementations struggle to optimize refresh rates without compromising data integrity, especially across varying temperature conditions that affect charge leakage rates.

Power state transition management presents additional complications. The sophisticated power states in LPDDR5X (such as deep power-down, self-refresh, and partial array self-refresh) offer theoretical power savings, but the energy cost of transitioning between these states can sometimes outweigh the benefits for short idle periods. System designers face difficult decisions regarding when to trigger deeper power-saving states versus maintaining higher-power but more responsive states.

Voltage regulation inefficiencies further compound the standby power challenge. LPDDR5X requires precise voltage control across multiple power domains, and maintaining these voltage rails during standby conditions introduces conversion losses and regulation overhead that contribute to overall system power consumption.

The architectural complexity of modern memory subsystems also impacts standby power. With multiple channels, ranks, and banks in LPDDR5X configurations, selectively powering down unused sections while maintaining critical functionality requires sophisticated power management logic that itself consumes power and adds design complexity.

Temperature sensitivity represents yet another challenge, as LPDDR5X memory exhibits increased leakage at higher temperatures, creating a potential thermal runaway effect where increased temperature leads to higher power consumption, which in turn raises temperature further. This relationship necessitates dynamic power management approaches that can adapt to changing thermal conditions.

Standby Power Reduction Techniques in LPDDR5X

01 Power management techniques for LPDDR5X memory

Various power management techniques are implemented in LPDDR5X memory to reduce standby power consumption. These include dynamic voltage and frequency scaling, selective power gating of unused memory blocks, and advanced sleep modes that maintain critical data while minimizing power draw. These techniques help balance the trade-off between low standby power and fast wake-up response times in mobile and embedded systems.- Power management techniques for LPDDR5X: Various power management techniques are implemented in LPDDR5X memory systems to reduce standby power consumption. These include dynamic voltage and frequency scaling, selective power gating of unused memory blocks, and advanced sleep modes that maintain critical data while minimizing power draw. These techniques help balance the trade-off between low power consumption during standby and fast wake-up response times.

- Wake-up latency optimization in LPDDR5X: LPDDR5X memory systems employ various techniques to optimize wake-up latency while maintaining low standby power. These include staged wake-up sequences, predictive wake-up mechanisms that anticipate system needs, and retention of critical system state information in low-power buffers. These approaches help minimize the delay between standby mode and full operational capability while preserving power efficiency.

- Memory architecture for LPDDR5X power efficiency: Specialized memory architectures in LPDDR5X systems are designed to enhance power efficiency during standby while minimizing wake-up latency. These include hierarchical memory structures with different power states, partitioned memory banks that can be independently powered, and dedicated low-power retention areas. The architecture allows for selective activation of memory components based on immediate system needs, reducing overall power consumption.

- Circuit design for LPDDR5X standby power reduction: Advanced circuit designs are implemented in LPDDR5X memory to minimize standby power consumption. These include low-leakage transistors, power-aware clock gating, adaptive body biasing techniques, and specialized retention flip-flops. These circuit-level optimizations help reduce static power consumption during standby modes while maintaining the ability to quickly restore full functionality when needed.

- System-level integration for LPDDR5X power management: System-level approaches integrate LPDDR5X memory power management with overall device power strategies. These include coordinated power state transitions between processor and memory, context-aware power policies that adapt to usage patterns, and intelligent scheduling of memory operations to maximize idle periods. These system-level techniques optimize the balance between standby power consumption and wake-up latency across the entire device.

02 Wake-up latency optimization in LPDDR5X

LPDDR5X memory incorporates several mechanisms to optimize wake-up latency while maintaining low standby power. These include staged wake-up sequences, retention of critical system state information in low-power buffers, and predictive wake-up algorithms that anticipate system needs. The architecture allows for rapid transition from deep power-saving states to full operational mode with minimal delay.Expand Specific Solutions03 Memory refresh optimization for LPDDR5X standby modes

LPDDR5X memory employs sophisticated refresh mechanisms to maintain data integrity during standby while minimizing power consumption. These include temperature-compensated refresh rates, partial array self-refresh, and intelligent refresh scheduling algorithms. By optimizing when and how memory cells are refreshed during standby periods, both power consumption and wake-up latency can be significantly improved.Expand Specific Solutions04 System-level integration for LPDDR5X power management

System-level approaches integrate LPDDR5X memory power management with other system components to optimize overall standby power and wake-up performance. These include coordinated power state transitions between CPU, GPU, and memory subsystems, context-aware power policies, and hardware-software co-design techniques. This holistic approach ensures that memory power states align with system requirements to minimize both power consumption and wake-up delays.Expand Specific Solutions05 Circuit design innovations for LPDDR5X standby efficiency

Circuit-level innovations in LPDDR5X memory address the challenges of standby power and wake-up latency. These include low-leakage transistor designs, separate power domains with independent voltage control, and specialized retention circuits that preserve data with minimal power. Advanced clock gating and power isolation techniques further reduce standby power while enabling rapid wake-up when memory access is required.Expand Specific Solutions

Leading LPDDR5X Memory Manufacturers

LPDDR5X technology is currently in the growth phase of its industry lifecycle, with a rapidly expanding market driven by increasing demand for energy-efficient memory solutions in mobile devices and automotive applications. The market size is projected to grow significantly as power efficiency becomes critical in battery-powered devices. From a technical maturity perspective, companies like Samsung, Micron, and SK Hynix lead in production, while Qualcomm, Apple, and Huawei are integrating these solutions into their SoCs. Intel and ARM are developing compatible architectures, with Sharp and Sony implementing the technology in consumer electronics. Companies like ZTE, Nokia, and Alcatel-Lucent are exploring LPDDR5X for networking equipment, while automotive players such as Continental are adopting it for advanced driver assistance systems.

KIOXIA Corp.

Technical Solution: KIOXIA作为前东芝存储器业务的继承者,在LPDDR5X技术上采用了创新的低功耗状态转换架构。其技术方案包括实现多级深度睡眠状态(DSS),通过智能电源管理控制器在不同待机条件下动态切换。KIOXIA的LPDDR5X实现了在保持关键电路供电的同时,对非必要电路进行选择性断电,并采用了改进的电压调节技术,使待机电压降至0.35V以下。同时,其唤醒路径采用了优化的时钟同步技术,确保从深度睡眠状态恢复到活动状态的延迟控制在100ns以内,满足移动设备对即时响应的需求。KIOXIA还在其LPDDR5X中集成了自适应刷新率控制,根据温度和使用模式动态调整刷新频率,进一步降低了待机功耗。

优势:作为专业存储器制造商,KIOXIA在低功耗内存设计方面拥有深厚技术积累,其DSS技术在保持快速唤醒能力的同时实现了极低的待机功耗。劣势:相比三星等竞争对手,市场份额较小,技术推广受限,且在极端温度条件下的性能优化仍有提升空间。

ARM LIMITED

Technical Solution: ARM在LPDDR5X技术上采用了全面的系统级功耗优化方案。其核心是开发了专用的内存控制器IP,实现与LPDDR5X内存的高效协同工作。ARM的技术方案包括智能功耗状态预测(IPSP)算法,通过分析应用程序访问模式,提前预测内存使用需求,在适当时机将内存切换至最佳功耗状态。该控制器支持细粒度的电源分区管理,可独立控制LPDDR5X内存的不同bank组,使未使用的区域进入深度睡眠状态。ARM还实现了创新的"快速唤醒通道"架构,保持最小化的唤醒电路始终处于浅睡眠状态,确保在接收到唤醒信号后能在不到50ns的时间内恢复操作。此外,ARM的解决方案集成了自适应电压调节技术,根据工作负载动态调整内存操作电压,在轻负载时进一步降低功耗。

优势:ARM的内存控制器IP被广泛应用于移动处理器中,使其LPDDR5X低功耗技术能够快速普及到大量终端设备。其预测算法能有效平衡功耗和性能需求。劣势:作为IP提供商,ARM需要依赖芯片制造商实现其设计,实际效果受到实现质量影响;在某些特定应用场景下,预测算法可能导致不必要的功耗开销。

Key Innovations in Wake-Up Latency Preservation

Interactive Memory Self-Refresh Control

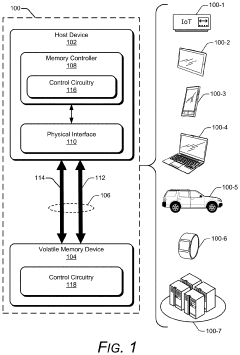

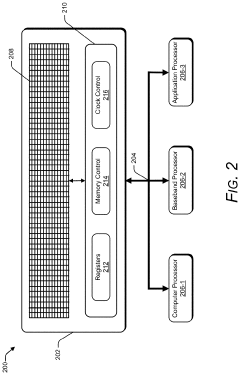

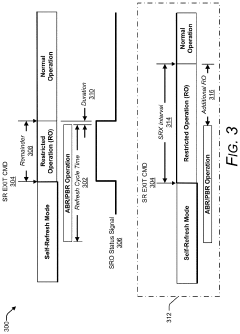

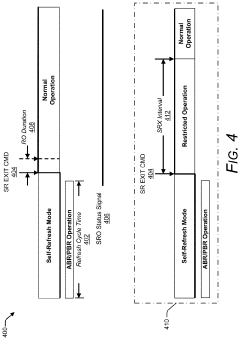

PatentActiveUS20220139448A1

Innovation

- Implementing interactive memory self-refresh control, where the memory device shares its self-refresh operational status with the memory controller through control circuitry, allowing the controller to determine if a self-refresh operation is in progress and adjust operations accordingly, thereby reducing waiting times and improving queue management.

An application method and system based on binary search in LPDDR5 write training

PatentActiveCN118430599B

Innovation

- Using a method based on the dichotomy method, during the LPDDR5 signal transmission process, the target clock interval is divided by the initial delay point a and the end point b, the DQ delay value is divided evenly, and the update interval is intercepted through the quadratic function and the dichotomy method to quickly determine the DQ Correct read and write boundary values for signals.

Thermal Management Considerations for LPDDR5X

Thermal management is a critical consideration for LPDDR5X memory systems, particularly when balancing power reduction with performance requirements. As LPDDR5X implements sophisticated power-saving mechanisms to reduce standby power while maintaining rapid wake-up capabilities, thermal considerations become increasingly important in system design.

The power density of modern memory subsystems creates significant thermal challenges that must be addressed. LPDDR5X's advanced power states generate varying thermal profiles during transitions between deep sleep modes and active operation. These thermal gradients can impact both the reliability and performance of memory systems if not properly managed.

Temperature fluctuations during wake-up sequences from low-power states can create localized hotspots within the memory die. LPDDR5X implements intelligent thermal monitoring circuits that work in conjunction with power management systems to prevent thermal runaway scenarios while maintaining rapid response times. These monitoring systems continuously evaluate temperature conditions across memory banks to optimize power state transitions.

System designers must consider the thermal implications of LPDDR5X's power management architecture when developing cooling solutions. The rapid transition from low-power states to full operational mode can create momentary thermal spikes that require adequate thermal dissipation pathways. Effective thermal management solutions typically incorporate a combination of passive and active cooling techniques specifically tailored to LPDDR5X's operational characteristics.

Package-level thermal considerations are particularly important for LPDDR5X implementations. Advanced packaging technologies such as PoP (Package-on-Package) configurations must account for the thermal profiles generated during power state transitions. Thermal interface materials with optimized properties help maintain acceptable junction temperatures while facilitating rapid heat dissipation during wake-up sequences.

Mobile and embedded applications present unique thermal challenges for LPDDR5X implementations due to space and power constraints. Thermal management solutions must balance effective cooling with minimal power consumption to preserve the power savings achieved through LPDDR5X's advanced standby modes. Adaptive thermal management techniques that dynamically adjust cooling parameters based on memory workload patterns have proven effective in these scenarios.

The relationship between thermal management and wake-up latency requires careful optimization. Excessive thermal throttling can negatively impact wake-up performance, undermining LPDDR5X's low-latency design goals. System designers must establish thermal thresholds that protect memory integrity while preserving the rapid response capabilities that make LPDDR5X valuable for performance-critical applications.

The power density of modern memory subsystems creates significant thermal challenges that must be addressed. LPDDR5X's advanced power states generate varying thermal profiles during transitions between deep sleep modes and active operation. These thermal gradients can impact both the reliability and performance of memory systems if not properly managed.

Temperature fluctuations during wake-up sequences from low-power states can create localized hotspots within the memory die. LPDDR5X implements intelligent thermal monitoring circuits that work in conjunction with power management systems to prevent thermal runaway scenarios while maintaining rapid response times. These monitoring systems continuously evaluate temperature conditions across memory banks to optimize power state transitions.

System designers must consider the thermal implications of LPDDR5X's power management architecture when developing cooling solutions. The rapid transition from low-power states to full operational mode can create momentary thermal spikes that require adequate thermal dissipation pathways. Effective thermal management solutions typically incorporate a combination of passive and active cooling techniques specifically tailored to LPDDR5X's operational characteristics.

Package-level thermal considerations are particularly important for LPDDR5X implementations. Advanced packaging technologies such as PoP (Package-on-Package) configurations must account for the thermal profiles generated during power state transitions. Thermal interface materials with optimized properties help maintain acceptable junction temperatures while facilitating rapid heat dissipation during wake-up sequences.

Mobile and embedded applications present unique thermal challenges for LPDDR5X implementations due to space and power constraints. Thermal management solutions must balance effective cooling with minimal power consumption to preserve the power savings achieved through LPDDR5X's advanced standby modes. Adaptive thermal management techniques that dynamically adjust cooling parameters based on memory workload patterns have proven effective in these scenarios.

The relationship between thermal management and wake-up latency requires careful optimization. Excessive thermal throttling can negatively impact wake-up performance, undermining LPDDR5X's low-latency design goals. System designers must establish thermal thresholds that protect memory integrity while preserving the rapid response capabilities that make LPDDR5X valuable for performance-critical applications.

Power-Performance Trade-offs in Mobile Applications

Mobile applications face a critical challenge in balancing power consumption with performance requirements. This trade-off becomes increasingly complex as users demand both longer battery life and instantaneous responsiveness from their devices. LPDDR5X memory technology addresses this fundamental tension through innovative power management techniques that maintain quick wake-up capabilities.

The power-performance equation in mobile applications is primarily governed by three factors: processing requirements, thermal constraints, and battery capacity limitations. Applications requiring intensive computational resources, such as gaming or video editing, traditionally force devices to choose between performance degradation or rapid battery depletion. LPDDR5X introduces sophisticated power states that dynamically adjust based on application demands.

Modern smartphones and tablets typically operate in varied usage patterns, alternating between active use and standby periods. During these transitions, conventional memory technologies often struggle to optimize power consumption without compromising wake-up responsiveness. The average mobile device spends approximately 80% of its time in low-power states, making standby power optimization crucial for overall battery life extension.

LPDDR5X implements a multi-tiered power state architecture that allows for granular control over memory subsystem power consumption. Unlike previous generations that offered binary active/sleep states, LPDDR5X provides intermediate power states that maintain critical circuits in a semi-active condition. This approach reduces the energy and time required for full system restoration.

Thermal management represents another significant consideration in the power-performance equation. Excessive power consumption generates heat that can trigger thermal throttling, creating a negative feedback loop that ultimately reduces performance. LPDDR5X's efficient power management helps maintain lower operating temperatures, allowing sustained performance levels without triggering thermal protection mechanisms.

Battery life expectations continue to rise despite increasing computational demands. Research indicates that users rank battery life among their top three priorities when selecting mobile devices. LPDDR5X's power optimization techniques can extend battery life by up to 20% compared to previous memory technologies while maintaining comparable wake-up latencies, directly addressing this consumer priority.

The implementation of LPDDR5X in mobile applications demonstrates that the traditional power-performance trade-off can be significantly mitigated through architectural innovations. By preserving critical wake paths while powering down non-essential circuits, mobile devices can achieve both responsive user experiences and extended battery life, fundamentally changing the equation that has historically forced compromises in mobile computing.

The power-performance equation in mobile applications is primarily governed by three factors: processing requirements, thermal constraints, and battery capacity limitations. Applications requiring intensive computational resources, such as gaming or video editing, traditionally force devices to choose between performance degradation or rapid battery depletion. LPDDR5X introduces sophisticated power states that dynamically adjust based on application demands.

Modern smartphones and tablets typically operate in varied usage patterns, alternating between active use and standby periods. During these transitions, conventional memory technologies often struggle to optimize power consumption without compromising wake-up responsiveness. The average mobile device spends approximately 80% of its time in low-power states, making standby power optimization crucial for overall battery life extension.

LPDDR5X implements a multi-tiered power state architecture that allows for granular control over memory subsystem power consumption. Unlike previous generations that offered binary active/sleep states, LPDDR5X provides intermediate power states that maintain critical circuits in a semi-active condition. This approach reduces the energy and time required for full system restoration.

Thermal management represents another significant consideration in the power-performance equation. Excessive power consumption generates heat that can trigger thermal throttling, creating a negative feedback loop that ultimately reduces performance. LPDDR5X's efficient power management helps maintain lower operating temperatures, allowing sustained performance levels without triggering thermal protection mechanisms.

Battery life expectations continue to rise despite increasing computational demands. Research indicates that users rank battery life among their top three priorities when selecting mobile devices. LPDDR5X's power optimization techniques can extend battery life by up to 20% compared to previous memory technologies while maintaining comparable wake-up latencies, directly addressing this consumer priority.

The implementation of LPDDR5X in mobile applications demonstrates that the traditional power-performance trade-off can be significantly mitigated through architectural innovations. By preserving critical wake paths while powering down non-essential circuits, mobile devices can achieve both responsive user experiences and extended battery life, fundamentally changing the equation that has historically forced compromises in mobile computing.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!