LPDDR5X EMI/EMC Compliance: Spread Spectrum, Shielding And Margining

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

LPDDR5X EMI/EMC Background and Objectives

The evolution of memory technologies has been driven by the increasing demands for higher bandwidth, lower power consumption, and improved performance in electronic devices. LPDDR (Low Power Double Data Rate) memory has emerged as a critical component in mobile and embedded systems, with each generation bringing significant advancements. The latest iteration, LPDDR5X, represents a substantial leap forward, offering data rates up to 8.5 Gbps, which is approximately 33% faster than its predecessor, LPDDR5.

As data rates increase, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges become more pronounced. EMI refers to the unwanted electromagnetic emissions that can interfere with other electronic devices, while EMC encompasses the ability of electronic equipment to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances. These issues are particularly critical in LPDDR5X implementations due to the high-frequency signals and fast edge rates involved.

The historical progression of LPDDR standards reveals a consistent trend toward higher performance coupled with increasingly complex EMI/EMC challenges. LPDDR1 operated at relatively modest speeds where EMI concerns were manageable with basic design practices. By LPDDR4, operating frequencies had increased to the point where sophisticated EMI mitigation techniques became essential. With LPDDR5X pushing boundaries even further, comprehensive EMI/EMC compliance strategies are now fundamental requirements rather than optional considerations.

Regulatory bodies worldwide, including the Federal Communications Commission (FCC) in the United States and the European Telecommunications Standards Institute (ETSI) in Europe, have established strict limits on electromagnetic emissions from electronic devices. Compliance with these regulations is mandatory for market access, making EMI/EMC considerations a critical aspect of LPDDR5X implementation.

The primary objective of this technical research is to comprehensively analyze the EMI/EMC compliance challenges specific to LPDDR5X memory interfaces and evaluate the effectiveness of three key mitigation strategies: Spread Spectrum techniques, shielding methodologies, and signal margining approaches. By understanding these technologies in depth, we aim to identify optimal implementation strategies that balance performance requirements with EMI/EMC compliance.

Additionally, this research seeks to establish a technical foundation for future memory interface designs by identifying emerging trends and potential innovations in EMI/EMC management. As memory technologies continue to evolve toward even higher speeds, the insights gained from this analysis will provide valuable guidance for anticipating and addressing future challenges in this critical area.

As data rates increase, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges become more pronounced. EMI refers to the unwanted electromagnetic emissions that can interfere with other electronic devices, while EMC encompasses the ability of electronic equipment to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances. These issues are particularly critical in LPDDR5X implementations due to the high-frequency signals and fast edge rates involved.

The historical progression of LPDDR standards reveals a consistent trend toward higher performance coupled with increasingly complex EMI/EMC challenges. LPDDR1 operated at relatively modest speeds where EMI concerns were manageable with basic design practices. By LPDDR4, operating frequencies had increased to the point where sophisticated EMI mitigation techniques became essential. With LPDDR5X pushing boundaries even further, comprehensive EMI/EMC compliance strategies are now fundamental requirements rather than optional considerations.

Regulatory bodies worldwide, including the Federal Communications Commission (FCC) in the United States and the European Telecommunications Standards Institute (ETSI) in Europe, have established strict limits on electromagnetic emissions from electronic devices. Compliance with these regulations is mandatory for market access, making EMI/EMC considerations a critical aspect of LPDDR5X implementation.

The primary objective of this technical research is to comprehensively analyze the EMI/EMC compliance challenges specific to LPDDR5X memory interfaces and evaluate the effectiveness of three key mitigation strategies: Spread Spectrum techniques, shielding methodologies, and signal margining approaches. By understanding these technologies in depth, we aim to identify optimal implementation strategies that balance performance requirements with EMI/EMC compliance.

Additionally, this research seeks to establish a technical foundation for future memory interface designs by identifying emerging trends and potential innovations in EMI/EMC management. As memory technologies continue to evolve toward even higher speeds, the insights gained from this analysis will provide valuable guidance for anticipating and addressing future challenges in this critical area.

Market Demand for EMI/EMC Compliant Memory Solutions

The demand for EMI/EMC compliant memory solutions has witnessed substantial growth in recent years, driven primarily by the increasing complexity of electronic systems and the proliferation of high-speed data transmission requirements. As LPDDR5X technology emerges as the standard for mobile and embedded applications, the market for solutions that address electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges has expanded significantly.

Consumer electronics manufacturers represent the largest market segment seeking EMI/EMC compliant memory solutions, with smartphone producers leading the demand. The global smartphone market, despite recent fluctuations, continues to drive innovation in memory technologies, particularly as devices incorporate more sophisticated features requiring faster data processing capabilities while maintaining power efficiency.

Automotive applications constitute the fastest-growing segment for EMI/EMC compliant memory solutions. Modern vehicles contain numerous electronic control units and advanced driver assistance systems that require high-speed memory with stringent EMI/EMC compliance to ensure safety and reliability. Industry reports indicate that automotive-grade LPDDR5X implementations are expected to grow at a compound annual rate exceeding that of consumer electronics applications.

Data center and enterprise computing environments also demonstrate increasing demand for EMI/EMC compliant memory solutions. As data centers consolidate more computing power into smaller physical footprints, the potential for electromagnetic interference between components increases dramatically, necessitating robust EMI/EMC compliance measures.

Market research reveals that customers across all segments are prioritizing three key aspects of EMI/EMC compliance: effective spread spectrum techniques to reduce peak emissions, comprehensive shielding solutions that minimize interference without compromising thermal performance, and reliable margining capabilities that ensure operational stability across varying environmental conditions.

Regional analysis shows that Asia-Pacific dominates the market for EMI/EMC compliant memory solutions, with major memory manufacturers and electronics producers concentrated in South Korea, Japan, Taiwan, and China. North America follows as the second-largest market, driven primarily by data center applications and defense sector requirements.

The market demonstrates a clear premium pricing structure for memory solutions with advanced EMI/EMC compliance features. Products incorporating sophisticated spread spectrum clocking, enhanced shielding technologies, and comprehensive margining capabilities command price premiums between 15-30% compared to standard offerings, reflecting the critical nature of these features in high-reliability applications.

Industry forecasts project continued growth in this segment as electronic devices become more densely packed with components operating at increasingly higher frequencies, further exacerbating EMI/EMC challenges and driving demand for innovative compliance solutions.

Consumer electronics manufacturers represent the largest market segment seeking EMI/EMC compliant memory solutions, with smartphone producers leading the demand. The global smartphone market, despite recent fluctuations, continues to drive innovation in memory technologies, particularly as devices incorporate more sophisticated features requiring faster data processing capabilities while maintaining power efficiency.

Automotive applications constitute the fastest-growing segment for EMI/EMC compliant memory solutions. Modern vehicles contain numerous electronic control units and advanced driver assistance systems that require high-speed memory with stringent EMI/EMC compliance to ensure safety and reliability. Industry reports indicate that automotive-grade LPDDR5X implementations are expected to grow at a compound annual rate exceeding that of consumer electronics applications.

Data center and enterprise computing environments also demonstrate increasing demand for EMI/EMC compliant memory solutions. As data centers consolidate more computing power into smaller physical footprints, the potential for electromagnetic interference between components increases dramatically, necessitating robust EMI/EMC compliance measures.

Market research reveals that customers across all segments are prioritizing three key aspects of EMI/EMC compliance: effective spread spectrum techniques to reduce peak emissions, comprehensive shielding solutions that minimize interference without compromising thermal performance, and reliable margining capabilities that ensure operational stability across varying environmental conditions.

Regional analysis shows that Asia-Pacific dominates the market for EMI/EMC compliant memory solutions, with major memory manufacturers and electronics producers concentrated in South Korea, Japan, Taiwan, and China. North America follows as the second-largest market, driven primarily by data center applications and defense sector requirements.

The market demonstrates a clear premium pricing structure for memory solutions with advanced EMI/EMC compliance features. Products incorporating sophisticated spread spectrum clocking, enhanced shielding technologies, and comprehensive margining capabilities command price premiums between 15-30% compared to standard offerings, reflecting the critical nature of these features in high-reliability applications.

Industry forecasts project continued growth in this segment as electronic devices become more densely packed with components operating at increasingly higher frequencies, further exacerbating EMI/EMC challenges and driving demand for innovative compliance solutions.

Current Challenges in LPDDR5X EMI/EMC Compliance

LPDDR5X memory technology, with its increased data rates of up to 8533 Mbps, introduces significant electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges that were less pronounced in previous generations. The higher operating frequencies and faster edge rates generate stronger electromagnetic emissions that can interfere with nearby electronic components and systems, creating compliance hurdles for device manufacturers.

One of the primary challenges is managing the increased EMI generated by the higher-frequency signals. As LPDDR5X operates at frequencies approaching 8.5 GHz, the potential for radiated emissions increases substantially, particularly at harmonic frequencies. These emissions can exceed regulatory limits established by bodies such as the FCC, CE, and VCCI, potentially delaying product certification and market entry.

Signal integrity issues present another significant challenge. The faster edge rates in LPDDR5X create more pronounced reflections, crosstalk, and ground bounce effects. These phenomena can compromise the reliability of data transmission and reception, leading to increased bit error rates and system instability. The reduced voltage margins in LPDDR5X (operating at 1.05V compared to 1.1V in LPDDR5) further exacerbate these challenges by providing less noise immunity.

Power integrity has become increasingly critical with LPDDR5X implementations. The rapid current transitions during high-speed operations create power distribution network (PDN) resonances that can couple into signal paths, generating additional EMI. The simultaneous switching noise (SSN) becomes more pronounced, requiring sophisticated power delivery solutions to maintain stable operation.

Traditional shielding approaches are proving inadequate for LPDDR5X applications. The higher frequencies involved can penetrate conventional shields more easily, requiring more advanced materials and designs. Additionally, the miniaturization trend in mobile and edge computing devices limits the physical space available for implementing robust shielding solutions.

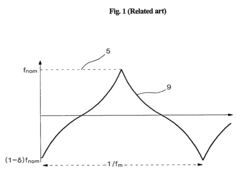

Spread spectrum clocking (SSC), while effective in previous generations, faces new challenges with LPDDR5X. The wider modulation profiles needed to sufficiently reduce peak emissions can potentially impact timing margins, which are already constrained in high-speed memory interfaces. Finding the optimal balance between EMI reduction and maintaining signal integrity becomes increasingly difficult.

Testing and validation methodologies also require significant updates. Conventional EMC testing equipment and procedures may not adequately capture the higher-frequency emissions from LPDDR5X systems. This necessitates investment in more advanced testing equipment and the development of new test methodologies specifically tailored to high-speed memory interfaces.

Regulatory compliance across different global markets adds another layer of complexity, as different regions may have varying EMC requirements that must be simultaneously satisfied without compromising performance or adding excessive cost to the final product.

One of the primary challenges is managing the increased EMI generated by the higher-frequency signals. As LPDDR5X operates at frequencies approaching 8.5 GHz, the potential for radiated emissions increases substantially, particularly at harmonic frequencies. These emissions can exceed regulatory limits established by bodies such as the FCC, CE, and VCCI, potentially delaying product certification and market entry.

Signal integrity issues present another significant challenge. The faster edge rates in LPDDR5X create more pronounced reflections, crosstalk, and ground bounce effects. These phenomena can compromise the reliability of data transmission and reception, leading to increased bit error rates and system instability. The reduced voltage margins in LPDDR5X (operating at 1.05V compared to 1.1V in LPDDR5) further exacerbate these challenges by providing less noise immunity.

Power integrity has become increasingly critical with LPDDR5X implementations. The rapid current transitions during high-speed operations create power distribution network (PDN) resonances that can couple into signal paths, generating additional EMI. The simultaneous switching noise (SSN) becomes more pronounced, requiring sophisticated power delivery solutions to maintain stable operation.

Traditional shielding approaches are proving inadequate for LPDDR5X applications. The higher frequencies involved can penetrate conventional shields more easily, requiring more advanced materials and designs. Additionally, the miniaturization trend in mobile and edge computing devices limits the physical space available for implementing robust shielding solutions.

Spread spectrum clocking (SSC), while effective in previous generations, faces new challenges with LPDDR5X. The wider modulation profiles needed to sufficiently reduce peak emissions can potentially impact timing margins, which are already constrained in high-speed memory interfaces. Finding the optimal balance between EMI reduction and maintaining signal integrity becomes increasingly difficult.

Testing and validation methodologies also require significant updates. Conventional EMC testing equipment and procedures may not adequately capture the higher-frequency emissions from LPDDR5X systems. This necessitates investment in more advanced testing equipment and the development of new test methodologies specifically tailored to high-speed memory interfaces.

Regulatory compliance across different global markets adds another layer of complexity, as different regions may have varying EMC requirements that must be simultaneously satisfied without compromising performance or adding excessive cost to the final product.

Current Spread Spectrum and Shielding Implementation Approaches

01 EMI/EMC shielding solutions for LPDDR5X memory

Various shielding techniques are employed to minimize electromagnetic interference in LPDDR5X memory systems. These include specialized shielding enclosures, conductive coatings, and metal shields that surround memory components to contain electromagnetic emissions. These solutions help maintain signal integrity at the high frequencies used by LPDDR5X memory while preventing interference with nearby components and ensuring compliance with EMC regulations.- EMI/EMC shielding techniques for LPDDR5X memory: Various shielding techniques are employed to minimize electromagnetic interference in LPDDR5X memory systems. These include specialized enclosures, conductive coatings, and metallic shields that contain electromagnetic emissions from high-speed memory components. Effective shielding is crucial for LPDDR5X compliance with EMI/EMC standards, as these memory modules operate at higher frequencies that can generate significant electromagnetic radiation.

- PCB layout optimization for LPDDR5X EMI/EMC compliance: Printed circuit board design plays a critical role in achieving EMI/EMC compliance for LPDDR5X memory systems. Optimized trace routing, controlled impedance, proper ground planes, and strategic component placement help minimize electromagnetic emissions. Advanced PCB layout techniques include differential pair routing, guard traces, and minimizing loop areas to reduce radiation from high-speed LPDDR5X memory interfaces.

- Signal integrity solutions for LPDDR5X compliance: Signal integrity management is essential for LPDDR5X EMI/EMC compliance. Techniques include impedance matching, termination strategies, and controlled slew rates to minimize reflections and ringing that can cause electromagnetic emissions. Advanced filtering components, decoupling capacitors, and ferrite beads are strategically implemented to suppress noise and maintain signal quality in high-speed memory interfaces.

- Power distribution network design for LPDDR5X: Proper power distribution network design is critical for LPDDR5X EMI/EMC compliance. This includes optimized power plane design, strategic decoupling capacitor placement, and power filtering techniques to minimize power supply noise that can contribute to electromagnetic emissions. Advanced power integrity solutions help maintain stable voltage levels during high-speed memory operations, reducing EMI caused by current transients.

- Testing and validation methods for LPDDR5X EMI/EMC compliance: Specialized testing methodologies are employed to verify LPDDR5X memory systems' compliance with EMI/EMC standards. These include pre-compliance testing, near-field scanning, and anechoic chamber measurements to identify and address potential emission issues. Advanced simulation techniques and automated test equipment help predict and validate electromagnetic compatibility before final certification, ensuring that LPDDR5X memory implementations meet regulatory requirements.

02 PCB design techniques for EMI/EMC compliance

Specific printed circuit board design methodologies are critical for LPDDR5X EMI/EMC compliance. These include optimized trace routing, controlled impedance paths, proper ground plane implementation, and strategic component placement. Advanced PCB layouts incorporate signal integrity features such as differential pair routing and guard traces to minimize crosstalk and radiation at the high data rates of LPDDR5X memory interfaces.Expand Specific Solutions03 Filtering and decoupling strategies

Effective filtering and decoupling techniques are essential for LPDDR5X EMI/EMC compliance. These include specialized filter components, strategic placement of decoupling capacitors, and power delivery network optimization. These elements work together to reduce noise on power and signal lines, suppress harmonics, and prevent electromagnetic emissions that could cause compliance failures in high-speed memory systems.Expand Specific Solutions04 Testing and validation methods for EMI/EMC compliance

Specialized testing methodologies are employed to validate LPDDR5X memory systems for EMI/EMC compliance. These include near-field scanning, anechoic chamber testing, and automated test equipment specifically designed for high-speed memory interfaces. Advanced simulation techniques are also used to predict potential EMI issues during the design phase, allowing for proactive mitigation before physical prototyping.Expand Specific Solutions05 System-level integration for EMI/EMC compliance

System-level approaches to LPDDR5X EMI/EMC compliance focus on the integration of memory subsystems within larger electronic devices. These include chassis design considerations, connector selection, cable management, and overall system grounding strategies. Thermal management solutions are also designed to avoid creating new EMI pathways while maintaining optimal operating temperatures for LPDDR5X memory components.Expand Specific Solutions

Key Industry Players in LPDDR5X Memory Ecosystem

The LPDDR5X EMI/EMC compliance market is in a growth phase, driven by increasing demand for high-performance memory in mobile devices, AI applications, and automotive systems. The market is projected to expand significantly as 5G and IoT technologies proliferate. Leading semiconductor companies like Intel, Huawei, and Renesas Electronics are advancing technical solutions for electromagnetic interference challenges, with specialized players such as ChangXin Memory Technologies and NXP Semiconductors developing innovative shielding technologies. The technology maturity varies across applications, with companies like ROHM and LG Innotek focusing on spread spectrum techniques to reduce EMI, while others like Qorvo and Laird Technologies are enhancing margining capabilities to ensure signal integrity in high-speed memory interfaces.

Intel Corp.

Technical Solution: Intel has developed comprehensive LPDDR5X EMI/EMC compliance solutions focusing on three key areas. For Spread Spectrum Clocking (SSC), Intel implements adaptive SSC techniques that dynamically adjust modulation parameters based on operating conditions, reducing EMI by up to 8-10dB in peak emissions. Their shielding approach incorporates multi-layer electromagnetic shields with specialized materials and geometries, creating a "guard band" around high-speed memory interfaces. Intel's margining methodology employs a statistical approach called "Dynamic Margining" that continuously monitors signal integrity parameters during operation, allowing real-time adjustment of voltage and timing margins to maintain compliance while optimizing performance. This is complemented by their "System-Level EMI Management" that coordinates memory subsystem operation with other platform components to minimize overall electromagnetic interference.

Strengths: Intel's solutions benefit from vertical integration capabilities, allowing optimization across silicon, package, and system levels. Their extensive testing infrastructure enables validation across diverse operating conditions. Weaknesses: The adaptive techniques may introduce additional complexity in validation and potentially impact performance in edge cases. The solutions may require more power and silicon area compared to fixed implementations.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has pioneered advanced LPDDR5X EMI/EMC compliance solutions through their "Tri-Shield" architecture. This comprehensive approach addresses electromagnetic interference through three coordinated layers. First, their "Dynamic Frequency Modulation" technology implements adaptive spread spectrum techniques that can reduce EMI by up to 12dB while maintaining memory performance. The modulation profiles are dynamically selected based on operating conditions and system requirements. Second, Huawei employs "Multi-dimensional Shielding" that combines physical barriers, ground planes, and specialized routing techniques to contain electromagnetic emissions. Their proprietary shield designs incorporate nano-composite materials that provide superior attenuation across a wide frequency range. Third, Huawei's "Predictive Margin Management" uses AI-driven algorithms to anticipate potential compliance issues before they occur, adjusting timing and voltage parameters proactively rather than reactively to maintain robust operation.

Strengths: Huawei's solution demonstrates excellent EMI reduction while maintaining high performance, with their AI-driven approach providing adaptive optimization for different usage scenarios. Their integrated hardware-software approach allows for system-level optimization. Weaknesses: The complex implementation may require significant engineering resources and specialized expertise. The solution may also have higher initial implementation costs compared to more traditional approaches.

Critical Patents and Research in EMI/EMC Compliance Technologies

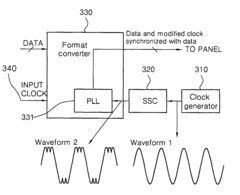

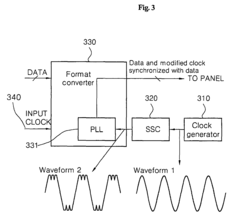

Electromagnetic interference prevention apparatus for flat panel display

PatentInactiveUS7973780B2

Innovation

- Applying a spread spectrum clocking method to modulate the frequency of the clock signal generated by a format converter in flat panel displays, increasing the frequency and reducing the amplitude of the clock signal to minimize EMI, thereby eliminating the need for conventional shielding methods.

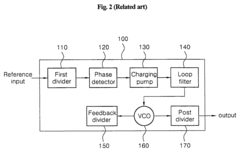

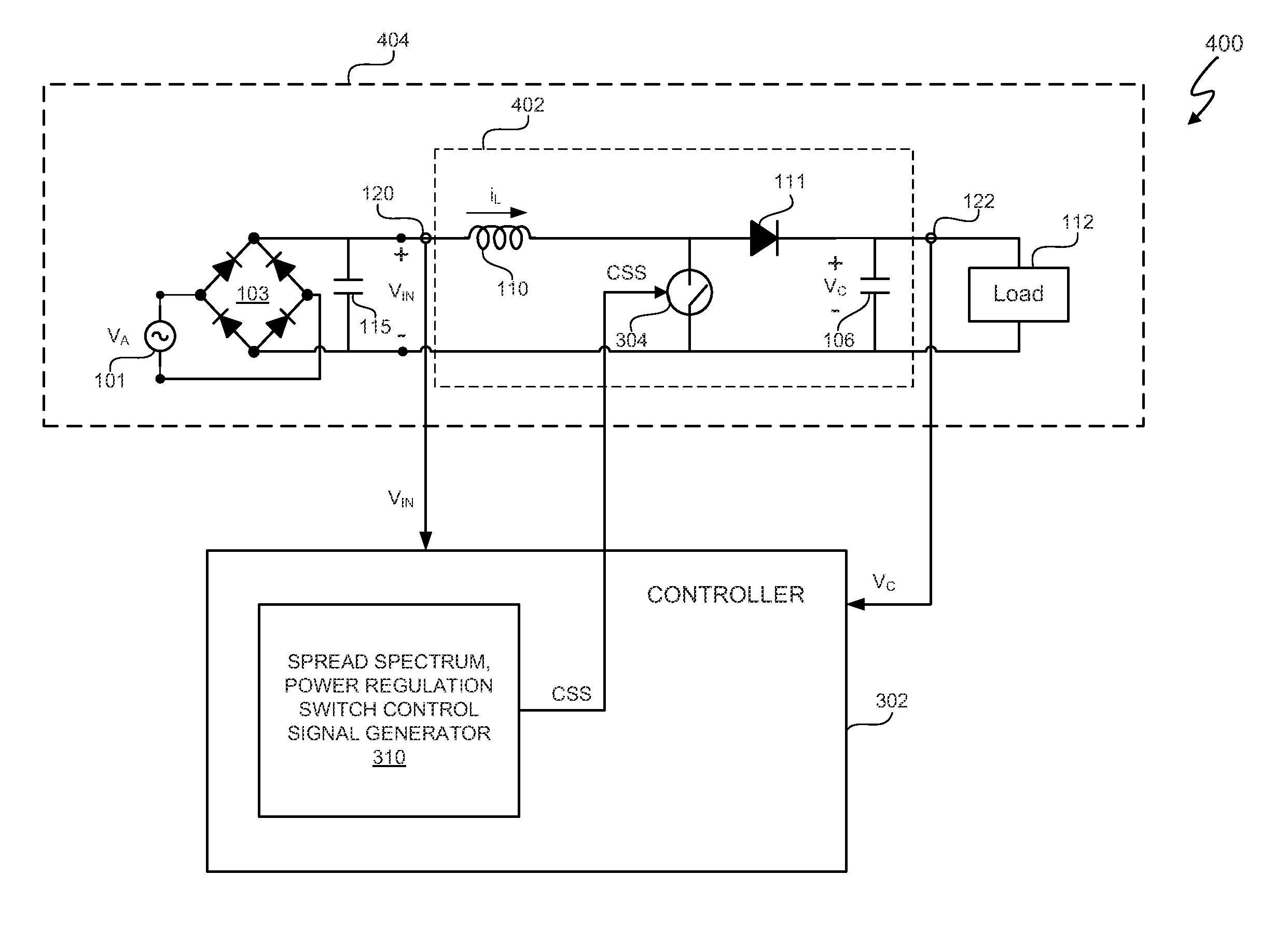

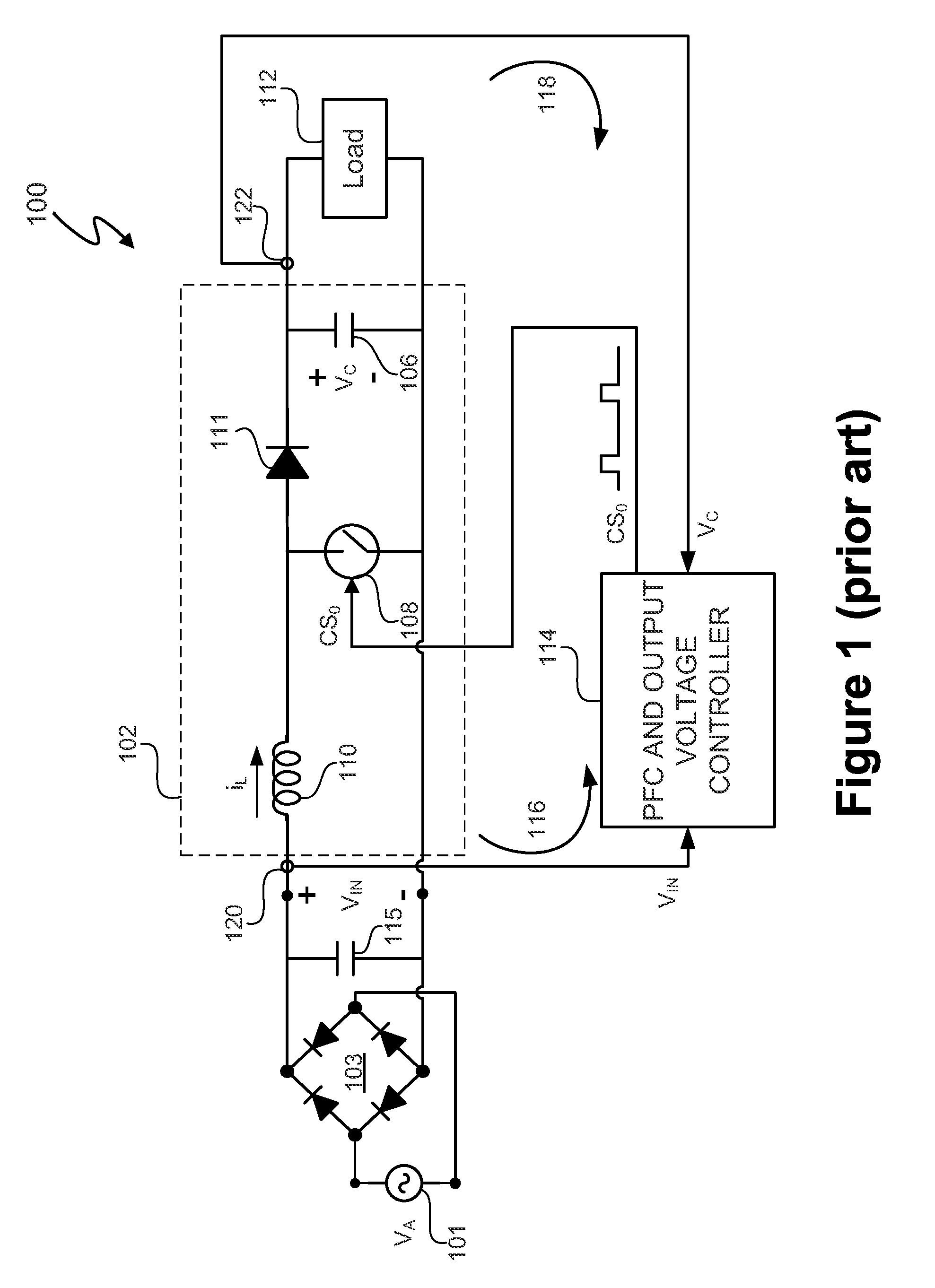

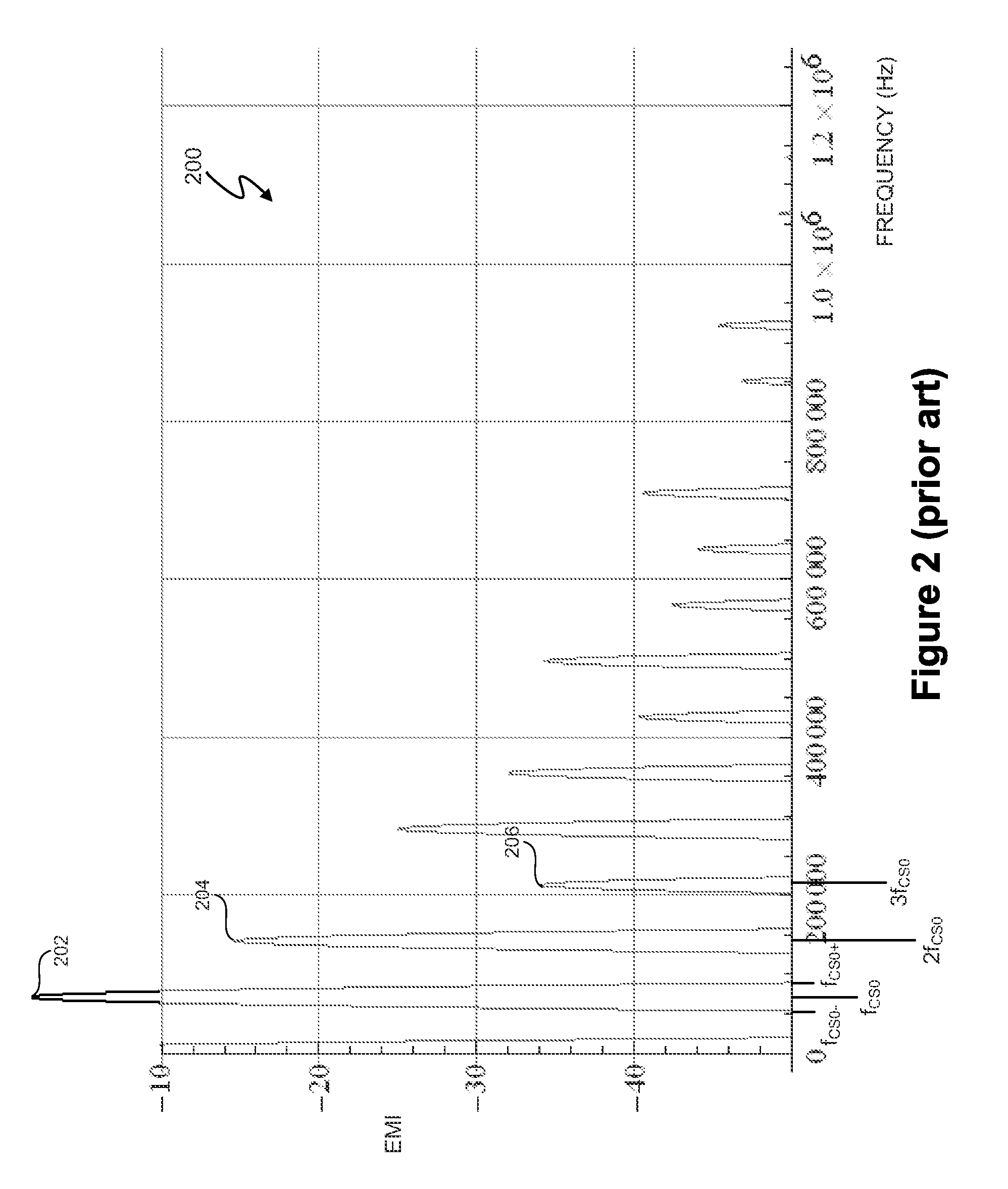

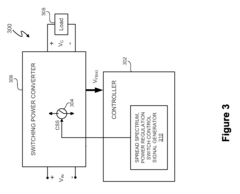

Switch power converter control with spread spectrum based electromagnetic interference reduction

PatentActiveUS8723438B2

Innovation

- A controller modulates the period and pulse width of a switch control signal using a spread spectrum strategy to reduce peak EMI values, incorporating a spread spectrum module that varies the precursor period value to generate a varying period and pulse width of the control signal, thereby spreading the frequency spectrum and reducing EMI, while also providing power factor correction for switching power converters.

Regulatory Standards and Certification Requirements

LPDDR5X memory systems must comply with a comprehensive set of regulatory standards and certification requirements to ensure electromagnetic compatibility across global markets. The International Electrotechnical Commission (IEC) establishes the foundational EMC standards through IEC 61000 series, which defines limits for electromagnetic emissions and immunity requirements that LPDDR5X implementations must meet.

In the United States, the Federal Communications Commission (FCC) mandates compliance with Part 15 regulations for digital devices, categorizing LPDDR5X-equipped systems as either Class A (commercial/industrial) or Class B (residential) devices. These classifications determine the applicable emission limits, with Class B requirements being more stringent due to proximity to sensitive consumer equipment.

The European Union enforces the EMC Directive 2014/30/EU, requiring CE marking for LPDDR5X memory systems sold within the European Economic Area. This directive necessitates conformity with harmonized standards such as EN 55032 for emissions and EN 55035 for immunity, with technical documentation and declarations of conformity maintained by manufacturers.

In Asia, Japan's VCCI (Voluntary Control Council for Interference) standards and China's CCC (China Compulsory Certification) impose region-specific requirements that must be addressed for market access. South Korea's KC certification similarly establishes mandatory EMC compliance parameters.

Certification processes for LPDDR5X systems typically involve pre-compliance testing, formal laboratory assessment by accredited facilities, and documentation submission to regulatory bodies. The testing methodology must adhere to CISPR 22/32 standards for conducted and radiated emissions measurements, with specific attention to the high-frequency operation ranges of LPDDR5X (6400-8533 Mbps).

Spread spectrum clocking techniques employed in LPDDR5X must be carefully implemented to ensure they reduce EMI without compromising system performance or violating regulatory limits. Most standards permit controlled modulation profiles that distribute energy across frequency bands without exceeding peak emission thresholds.

Shielding solutions must be validated through standardized testing procedures that verify their effectiveness across the operational frequency range of LPDDR5X. This includes assessment under various environmental conditions to ensure consistent compliance throughout the product lifecycle.

Margining practices must be documented to demonstrate that LPDDR5X systems maintain compliance even when operating at performance extremes. This requires establishing guard bands that account for manufacturing variations, temperature fluctuations, and aging effects while still meeting regulatory limits.

In the United States, the Federal Communications Commission (FCC) mandates compliance with Part 15 regulations for digital devices, categorizing LPDDR5X-equipped systems as either Class A (commercial/industrial) or Class B (residential) devices. These classifications determine the applicable emission limits, with Class B requirements being more stringent due to proximity to sensitive consumer equipment.

The European Union enforces the EMC Directive 2014/30/EU, requiring CE marking for LPDDR5X memory systems sold within the European Economic Area. This directive necessitates conformity with harmonized standards such as EN 55032 for emissions and EN 55035 for immunity, with technical documentation and declarations of conformity maintained by manufacturers.

In Asia, Japan's VCCI (Voluntary Control Council for Interference) standards and China's CCC (China Compulsory Certification) impose region-specific requirements that must be addressed for market access. South Korea's KC certification similarly establishes mandatory EMC compliance parameters.

Certification processes for LPDDR5X systems typically involve pre-compliance testing, formal laboratory assessment by accredited facilities, and documentation submission to regulatory bodies. The testing methodology must adhere to CISPR 22/32 standards for conducted and radiated emissions measurements, with specific attention to the high-frequency operation ranges of LPDDR5X (6400-8533 Mbps).

Spread spectrum clocking techniques employed in LPDDR5X must be carefully implemented to ensure they reduce EMI without compromising system performance or violating regulatory limits. Most standards permit controlled modulation profiles that distribute energy across frequency bands without exceeding peak emission thresholds.

Shielding solutions must be validated through standardized testing procedures that verify their effectiveness across the operational frequency range of LPDDR5X. This includes assessment under various environmental conditions to ensure consistent compliance throughout the product lifecycle.

Margining practices must be documented to demonstrate that LPDDR5X systems maintain compliance even when operating at performance extremes. This requires establishing guard bands that account for manufacturing variations, temperature fluctuations, and aging effects while still meeting regulatory limits.

Test Methodologies and Validation Frameworks

Comprehensive validation of LPDDR5X EMI/EMC compliance requires structured test methodologies and robust validation frameworks. The industry has established several standardized approaches for evaluating electromagnetic interference and compatibility in high-speed memory systems.

Signal integrity testing forms the foundation of LPDDR5X validation, employing time-domain reflectometry (TDR) and vector network analysis (VNA) to characterize impedance profiles and transmission parameters. These measurements provide critical insights into signal degradation mechanisms that may contribute to EMI/EMC issues at speeds exceeding 8.5 Gbps.

Conducted emissions testing protocols have evolved specifically for LPDDR5X implementations, focusing on common-mode current measurements across frequency ranges from 150 kHz to 1 GHz. The validation framework typically incorporates specialized current probes and spectrum analyzers with resolution bandwidths aligned to international standards such as CISPR 22.

Radiated emissions testing methodologies for LPDDR5X systems employ semi-anechoic chambers or GTEM cells to measure far-field electromagnetic radiation. Test configurations must account for various operational modes, including different refresh rates and power-saving states that can significantly alter the EMI profile.

System-level validation frameworks integrate multiple test methodologies to evaluate EMI/EMC performance under realistic conditions. These frameworks incorporate thermal cycling, voltage margining, and frequency variation to stress the memory subsystem while monitoring electromagnetic compliance across operational boundaries.

Automated test equipment (ATE) platforms have been developed specifically for LPDDR5X validation, featuring integrated spread spectrum analysis capabilities and real-time shielding effectiveness measurements. These systems enable comprehensive characterization of EMI/EMC parameters while maintaining test repeatability and precision.

Statistical validation approaches have gained prominence, employing design of experiments (DoE) methodologies to efficiently explore the complex interaction between spread spectrum clocking parameters, shielding configurations, and operational margins. This approach enables optimization of EMI/EMC performance while minimizing test time and resources.

Compliance validation frameworks increasingly incorporate machine learning algorithms to identify subtle patterns in EMI/EMC test data that may indicate potential field issues. These advanced analytical methods complement traditional pass/fail criteria by providing predictive insights into long-term reliability under varying electromagnetic environments.

Signal integrity testing forms the foundation of LPDDR5X validation, employing time-domain reflectometry (TDR) and vector network analysis (VNA) to characterize impedance profiles and transmission parameters. These measurements provide critical insights into signal degradation mechanisms that may contribute to EMI/EMC issues at speeds exceeding 8.5 Gbps.

Conducted emissions testing protocols have evolved specifically for LPDDR5X implementations, focusing on common-mode current measurements across frequency ranges from 150 kHz to 1 GHz. The validation framework typically incorporates specialized current probes and spectrum analyzers with resolution bandwidths aligned to international standards such as CISPR 22.

Radiated emissions testing methodologies for LPDDR5X systems employ semi-anechoic chambers or GTEM cells to measure far-field electromagnetic radiation. Test configurations must account for various operational modes, including different refresh rates and power-saving states that can significantly alter the EMI profile.

System-level validation frameworks integrate multiple test methodologies to evaluate EMI/EMC performance under realistic conditions. These frameworks incorporate thermal cycling, voltage margining, and frequency variation to stress the memory subsystem while monitoring electromagnetic compliance across operational boundaries.

Automated test equipment (ATE) platforms have been developed specifically for LPDDR5X validation, featuring integrated spread spectrum analysis capabilities and real-time shielding effectiveness measurements. These systems enable comprehensive characterization of EMI/EMC parameters while maintaining test repeatability and precision.

Statistical validation approaches have gained prominence, employing design of experiments (DoE) methodologies to efficiently explore the complex interaction between spread spectrum clocking parameters, shielding configurations, and operational margins. This approach enables optimization of EMI/EMC performance while minimizing test time and resources.

Compliance validation frameworks increasingly incorporate machine learning algorithms to identify subtle patterns in EMI/EMC test data that may indicate potential field issues. These advanced analytical methods complement traditional pass/fail criteria by providing predictive insights into long-term reliability under varying electromagnetic environments.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!