LPDDR5X Controller Scheduling: QoS Targets, Burst Efficiency And Read–Write Turnarounds

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

LPDDR5X Evolution and Performance Objectives

The evolution of LPDDR (Low Power Double Data Rate) memory technology has been marked by significant advancements in performance, power efficiency, and bandwidth capabilities. LPDDR5X represents the latest generation in this technological progression, offering substantial improvements over its predecessors. The journey from LPDDR4 to LPDDR5X has seen memory speeds increase from 3200 Mbps to beyond 8533 Mbps, demonstrating the rapid pace of innovation in this domain.

LPDDR5X was officially standardized by JEDEC in 2020, building upon the foundation established by LPDDR5. This evolution was driven by the growing demands of mobile computing, artificial intelligence applications, and high-performance computing systems that require both increased bandwidth and improved power efficiency. The primary performance objectives for LPDDR5X focus on achieving higher data rates while maintaining or reducing power consumption compared to previous generations.

A key performance target for LPDDR5X is the optimization of Quality of Service (QoS) parameters. As modern computing systems increasingly run multiple concurrent applications with varying memory access patterns and priorities, the memory controller must efficiently arbitrate between these competing demands. QoS targets for LPDDR5X include minimizing latency for high-priority operations, ensuring fairness in memory access, and providing predictable performance under varying workloads.

Burst efficiency represents another critical performance objective for LPDDR5X. The technology implements improved burst operations with 16n prefetch architecture (compared to 8n in LPDDR4), allowing for more efficient data transfers. This enhancement enables the controller to process larger chunks of data in each memory access operation, significantly improving throughput for sequential access patterns common in multimedia and AI workloads.

Read-write turnaround optimization stands as a fundamental performance goal for LPDDR5X controllers. The transition between read and write operations traditionally introduces latency penalties due to bus direction changes and timing constraints. LPDDR5X implements enhanced command bus efficiency and improved bank group architecture to reduce these turnaround penalties, enabling more efficient interleaving of read and write operations.

The technology trend is moving toward increasingly sophisticated memory controllers that can dynamically adapt scheduling policies based on workload characteristics. Future LPDDR5X implementations aim to incorporate machine learning techniques to predict access patterns and optimize scheduling decisions in real-time, further enhancing both performance and power efficiency.

As system-on-chip designs continue to integrate more diverse computing elements, LPDDR5X controllers must balance the competing requirements of CPU cores, GPU units, AI accelerators, and various I/O subsystems. This balancing act represents one of the most significant challenges in achieving optimal memory subsystem performance in modern computing platforms.

LPDDR5X was officially standardized by JEDEC in 2020, building upon the foundation established by LPDDR5. This evolution was driven by the growing demands of mobile computing, artificial intelligence applications, and high-performance computing systems that require both increased bandwidth and improved power efficiency. The primary performance objectives for LPDDR5X focus on achieving higher data rates while maintaining or reducing power consumption compared to previous generations.

A key performance target for LPDDR5X is the optimization of Quality of Service (QoS) parameters. As modern computing systems increasingly run multiple concurrent applications with varying memory access patterns and priorities, the memory controller must efficiently arbitrate between these competing demands. QoS targets for LPDDR5X include minimizing latency for high-priority operations, ensuring fairness in memory access, and providing predictable performance under varying workloads.

Burst efficiency represents another critical performance objective for LPDDR5X. The technology implements improved burst operations with 16n prefetch architecture (compared to 8n in LPDDR4), allowing for more efficient data transfers. This enhancement enables the controller to process larger chunks of data in each memory access operation, significantly improving throughput for sequential access patterns common in multimedia and AI workloads.

Read-write turnaround optimization stands as a fundamental performance goal for LPDDR5X controllers. The transition between read and write operations traditionally introduces latency penalties due to bus direction changes and timing constraints. LPDDR5X implements enhanced command bus efficiency and improved bank group architecture to reduce these turnaround penalties, enabling more efficient interleaving of read and write operations.

The technology trend is moving toward increasingly sophisticated memory controllers that can dynamically adapt scheduling policies based on workload characteristics. Future LPDDR5X implementations aim to incorporate machine learning techniques to predict access patterns and optimize scheduling decisions in real-time, further enhancing both performance and power efficiency.

As system-on-chip designs continue to integrate more diverse computing elements, LPDDR5X controllers must balance the competing requirements of CPU cores, GPU units, AI accelerators, and various I/O subsystems. This balancing act represents one of the most significant challenges in achieving optimal memory subsystem performance in modern computing platforms.

Market Requirements for High-Speed Memory Controllers

The memory controller market is experiencing unprecedented demand for high-performance solutions driven by data-intensive applications across multiple sectors. Enterprise data centers require memory controllers capable of handling massive parallel workloads with strict quality of service (QoS) guarantees to maintain service level agreements. Cloud computing providers specifically demand memory controllers that can efficiently manage resources across virtualized environments while maintaining performance isolation between tenants.

Mobile device manufacturers represent another significant market segment, requiring memory controllers that balance high performance with power efficiency. As mobile applications become increasingly sophisticated, particularly with on-device AI processing, the need for controllers that can efficiently schedule LPDDR5X operations while minimizing power consumption has become critical.

Automotive systems present unique requirements for memory controllers, particularly in advanced driver assistance systems (ADAS) and autonomous driving platforms. These applications demand deterministic performance with guaranteed response times, making QoS capabilities essential. Memory controllers must ensure critical safety functions receive priority access while maintaining overall system responsiveness.

The gaming and graphics processing market requires memory controllers capable of handling high-bandwidth streaming data with minimal latency. Console manufacturers and gaming PC component makers seek controllers that can optimize burst efficiency to deliver smooth frame rates and responsive gameplay experiences.

AI accelerator manufacturers represent the fastest-growing segment, with requirements for memory controllers that can efficiently manage the complex data access patterns of neural network training and inference. These applications demand sophisticated scheduling algorithms that can maximize bandwidth utilization while meeting strict timing constraints.

Market research indicates that memory bandwidth requirements are doubling approximately every two years across these segments. This trend is driving demand for controllers supporting the latest LPDDR5X specifications, which offer significant improvements in data rates and power efficiency compared to previous generations.

Industry surveys reveal that system designers increasingly prioritize memory controllers with advanced scheduling capabilities that can dynamically adapt to changing workload characteristics. The ability to efficiently handle read-write turnarounds has emerged as a key differentiator, with benchmarks showing up to 30% performance improvements in mixed workloads when using optimized scheduling algorithms.

Memory controller solutions that can demonstrate quantifiable QoS guarantees command premium pricing in enterprise and automotive markets, where predictable performance directly impacts business operations and safety considerations.

Mobile device manufacturers represent another significant market segment, requiring memory controllers that balance high performance with power efficiency. As mobile applications become increasingly sophisticated, particularly with on-device AI processing, the need for controllers that can efficiently schedule LPDDR5X operations while minimizing power consumption has become critical.

Automotive systems present unique requirements for memory controllers, particularly in advanced driver assistance systems (ADAS) and autonomous driving platforms. These applications demand deterministic performance with guaranteed response times, making QoS capabilities essential. Memory controllers must ensure critical safety functions receive priority access while maintaining overall system responsiveness.

The gaming and graphics processing market requires memory controllers capable of handling high-bandwidth streaming data with minimal latency. Console manufacturers and gaming PC component makers seek controllers that can optimize burst efficiency to deliver smooth frame rates and responsive gameplay experiences.

AI accelerator manufacturers represent the fastest-growing segment, with requirements for memory controllers that can efficiently manage the complex data access patterns of neural network training and inference. These applications demand sophisticated scheduling algorithms that can maximize bandwidth utilization while meeting strict timing constraints.

Market research indicates that memory bandwidth requirements are doubling approximately every two years across these segments. This trend is driving demand for controllers supporting the latest LPDDR5X specifications, which offer significant improvements in data rates and power efficiency compared to previous generations.

Industry surveys reveal that system designers increasingly prioritize memory controllers with advanced scheduling capabilities that can dynamically adapt to changing workload characteristics. The ability to efficiently handle read-write turnarounds has emerged as a key differentiator, with benchmarks showing up to 30% performance improvements in mixed workloads when using optimized scheduling algorithms.

Memory controller solutions that can demonstrate quantifiable QoS guarantees command premium pricing in enterprise and automotive markets, where predictable performance directly impacts business operations and safety considerations.

Technical Challenges in LPDDR5X Controller Implementation

The implementation of LPDDR5X controllers presents several significant technical challenges that must be addressed to fully leverage the performance capabilities of this advanced memory technology. One of the primary difficulties lies in the complex scheduling algorithms required to balance Quality of Service (QoS) targets with optimal memory utilization. LPDDR5X's increased data rates of up to 8.5 Gbps demand more sophisticated traffic management to prevent high-priority operations from experiencing excessive latency while maintaining overall throughput.

Burst efficiency optimization represents another critical challenge. The controller must intelligently group memory operations to maximize the utilization of each activated row, minimizing the energy and performance penalties associated with frequent row activations. This becomes increasingly difficult as system workloads become more diverse and unpredictable, particularly in mobile and edge computing applications where LPDDR5X is commonly deployed.

Read-write turnaround management presents perhaps the most technically demanding aspect of controller design. The transition between read and write operations incurs significant timing penalties in LPDDR5X memory, with each direction change potentially causing several clock cycles of idle time on the data bus. Controller designers must implement advanced command reordering and grouping strategies to minimize these transitions while still meeting application-specific timing requirements.

Power management adds another layer of complexity, as LPDDR5X introduces more sophisticated power-saving modes that the controller must judiciously employ without compromising performance. The controller must dynamically balance power efficiency against latency considerations, particularly challenging in battery-powered devices where both factors are critical.

Signal integrity challenges have intensified with LPDDR5X's higher operating frequencies. The controller must incorporate advanced equalization techniques and precise timing calibration to maintain reliable data transfer across the physical interface. This often requires adaptive algorithms that can compensate for temperature variations and voltage fluctuations during operation.

Compatibility with diverse system architectures further complicates controller design. Modern SoCs may incorporate multiple processing elements with varying memory access patterns and priorities. The LPDDR5X controller must efficiently arbitrate between these competing demands while adhering to the complex timing parameters of the memory protocol.

Testing and validation of LPDDR5X controllers present unique challenges due to the complex interactions between scheduling decisions and system performance. Traditional verification methodologies often prove insufficient, necessitating advanced simulation techniques and hardware-in-the-loop testing to ensure reliable operation across all potential usage scenarios.

Burst efficiency optimization represents another critical challenge. The controller must intelligently group memory operations to maximize the utilization of each activated row, minimizing the energy and performance penalties associated with frequent row activations. This becomes increasingly difficult as system workloads become more diverse and unpredictable, particularly in mobile and edge computing applications where LPDDR5X is commonly deployed.

Read-write turnaround management presents perhaps the most technically demanding aspect of controller design. The transition between read and write operations incurs significant timing penalties in LPDDR5X memory, with each direction change potentially causing several clock cycles of idle time on the data bus. Controller designers must implement advanced command reordering and grouping strategies to minimize these transitions while still meeting application-specific timing requirements.

Power management adds another layer of complexity, as LPDDR5X introduces more sophisticated power-saving modes that the controller must judiciously employ without compromising performance. The controller must dynamically balance power efficiency against latency considerations, particularly challenging in battery-powered devices where both factors are critical.

Signal integrity challenges have intensified with LPDDR5X's higher operating frequencies. The controller must incorporate advanced equalization techniques and precise timing calibration to maintain reliable data transfer across the physical interface. This often requires adaptive algorithms that can compensate for temperature variations and voltage fluctuations during operation.

Compatibility with diverse system architectures further complicates controller design. Modern SoCs may incorporate multiple processing elements with varying memory access patterns and priorities. The LPDDR5X controller must efficiently arbitrate between these competing demands while adhering to the complex timing parameters of the memory protocol.

Testing and validation of LPDDR5X controllers present unique challenges due to the complex interactions between scheduling decisions and system performance. Traditional verification methodologies often prove insufficient, necessitating advanced simulation techniques and hardware-in-the-loop testing to ensure reliable operation across all potential usage scenarios.

Current QoS and Scheduling Algorithms for LPDDR5X

01 Memory controller scheduling for QoS targets

Memory controllers can be designed with scheduling algorithms that prioritize memory operations based on Quality of Service (QoS) requirements. These controllers implement mechanisms to ensure critical operations meet their timing constraints while maintaining system performance. By assigning priority levels to different memory requests, the controller can make intelligent decisions about which operations to execute first, helping to meet QoS targets even under heavy system load conditions.- Memory controller scheduling for QoS targets: Memory controllers implement scheduling algorithms to meet Quality of Service (QoS) targets in LPDDR5X systems. These controllers prioritize memory access requests based on predefined QoS parameters, ensuring critical applications receive sufficient memory bandwidth and meet latency requirements. Advanced scheduling techniques include request prioritization, deadline-based scheduling, and dynamic bandwidth allocation to balance system performance needs while maintaining QoS guarantees for multiple concurrent applications.

- Burst efficiency optimization techniques: Optimizing burst efficiency in LPDDR5X controllers involves maximizing data transfer during each memory access cycle. Controllers implement techniques such as request reordering, command grouping, and burst length optimization to increase throughput. By intelligently scheduling memory operations to utilize the full capacity of each burst, these controllers reduce the overhead associated with memory access operations and improve overall system performance. Advanced burst efficiency techniques include adaptive burst sizing and dynamic burst alignment based on access patterns.

- Read-write turnaround optimization: LPDDR5X controllers implement specialized techniques to minimize the performance penalties associated with switching between read and write operations. These techniques include command reordering to group similar operations, intelligent scheduling to reduce the frequency of read-write transitions, and pipeline optimization to hide turnaround latencies. By managing the timing of read and write operations, controllers can significantly reduce the idle time between operations and improve memory bandwidth utilization in high-performance applications.

- Dynamic timing parameter management: Advanced LPDDR5X controllers employ dynamic timing parameter management to adapt to changing system conditions. These controllers can adjust timing parameters in real-time based on workload characteristics, thermal conditions, and power constraints. By dynamically optimizing parameters such as refresh rates, access timings, and voltage levels, these controllers balance performance, power consumption, and reliability. This approach enables systems to maintain optimal performance across varying operational conditions while adhering to power and thermal constraints.

- Multi-channel arbitration and load balancing: LPDDR5X controllers implement sophisticated multi-channel arbitration and load balancing mechanisms to distribute memory access requests efficiently across available memory channels. These techniques include channel-aware scheduling, load monitoring, and dynamic request routing to prevent channel congestion and hotspots. By balancing the workload across multiple channels, controllers can maximize overall memory bandwidth utilization, reduce access latencies, and improve system responsiveness under heavy memory traffic conditions.

02 Burst efficiency optimization in LPDDR memory

Memory controllers can optimize burst operations in LPDDR memory by intelligently grouping read and write commands. This approach maximizes data transfer efficiency by utilizing the full capacity of each memory burst cycle. Advanced controllers implement techniques such as request reordering, command grouping, and burst length optimization to increase throughput and reduce latency. These optimizations are particularly important for LPDDR5X which supports higher data rates and more complex burst operations.Expand Specific Solutions03 Read-write turnaround optimization techniques

Minimizing the performance impact of switching between read and write operations is critical for LPDDR5X controller efficiency. Memory controllers implement sophisticated techniques to reduce read-write turnaround penalties, including command reordering, write buffering, and read prediction algorithms. By intelligently scheduling operations to minimize direction changes on the memory bus, controllers can significantly improve overall memory bandwidth utilization and reduce latency in mixed read-write workloads.Expand Specific Solutions04 Dynamic timing parameter management

LPDDR5X controllers can dynamically adjust timing parameters based on workload characteristics and system conditions. These controllers monitor memory access patterns and adaptively modify parameters such as refresh rates, command spacing, and power states to optimize performance while maintaining reliability. By implementing dynamic timing management, controllers can balance competing requirements for power efficiency, thermal management, and performance to achieve optimal operation across varying workloads.Expand Specific Solutions05 Multi-channel arbitration and resource allocation

Advanced memory controllers implement sophisticated arbitration schemes to manage access across multiple memory channels. These controllers allocate resources based on application requirements, traffic patterns, and system priorities. By intelligently distributing memory requests across available channels and banks, controllers can maximize parallelism, reduce contention, and improve overall system throughput. This approach is particularly beneficial for LPDDR5X systems that must balance competing demands from multiple processing units with different QoS requirements.Expand Specific Solutions

Leading LPDDR5X Controller and Memory Manufacturers

The LPDDR5X controller scheduling market is currently in a growth phase, with increasing demand driven by mobile devices, AI applications, and IoT expansion. The market is projected to reach significant scale as memory performance becomes critical for next-generation applications. Technologically, the field shows varying maturity levels across competitors. Samsung Electronics and SK Hynix lead with advanced implementations, while Huawei, Apple, and Qualcomm (via partnerships) demonstrate strong capabilities in controller optimization. Chinese players like ChangXin Memory and ZTE are rapidly advancing their technologies. Companies including Rambus and GLOBALFOUNDRIES provide specialized solutions focusing on QoS targets and power efficiency. The competitive landscape is characterized by established memory manufacturers expanding controller capabilities and system integrators developing proprietary solutions to optimize burst efficiency and read-write turnaround performance.

Beijing Xiaomi Mobile Software Co., Ltd.

Technical Solution: Xiaomi has developed an advanced LPDDR5X controller scheduling system that optimizes memory performance in their mobile devices. Their approach focuses on dynamic QoS management that adaptively prioritizes tasks based on real-time application demands. The controller implements a sophisticated burst grouping algorithm that maximizes data transfer efficiency by intelligently combining multiple smaller requests into optimal-sized bursts. Xiaomi's solution features an innovative read-write turnaround optimization technique that reduces the latency penalties associated with switching between read and write operations. This is achieved through predictive command scheduling that analyzes access patterns and preemptively adjusts the command queue to minimize direction changes. Their implementation includes dedicated hardware units for QoS monitoring that can detect and respond to potential QoS violations before they impact user experience, particularly important for multimedia and gaming applications where consistent performance is critical.

Strengths: Excellent power efficiency with up to 20% reduction in memory subsystem power consumption compared to previous generations. Highly optimized for mobile use cases with variable workloads. Weaknesses: May sacrifice some peak performance to maintain consistent QoS guarantees, potentially limiting maximum throughput in certain synthetic benchmarks.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered advanced LPDDR5X controller scheduling technology focusing on maximizing both performance and energy efficiency. Their controller architecture implements a multi-tier QoS management system that categorizes memory requests into critical, high-priority, and background tasks with dynamic threshold adjustment based on system load. Samsung's implementation features an intelligent burst scheduling algorithm that optimizes the trade-off between maximizing bus utilization and meeting latency requirements for time-sensitive applications. A key innovation in their approach is the predictive read-write turnaround management that uses access pattern history to minimize the performance penalties associated with direction switching. The controller employs a sophisticated bank management strategy that maintains awareness of row buffer contents across multiple banks to reduce activation commands and improve energy efficiency. Samsung has also implemented adaptive refresh timing that coordinates refresh operations with periods of low memory activity, reducing their impact on overall system performance. Their solution includes hardware-level monitoring capabilities that provide real-time feedback on QoS target achievement, allowing for dynamic adjustment of scheduling parameters.

Strengths: Industry-leading power efficiency with sophisticated power state management that can reduce memory subsystem power by up to 30% in typical mobile workloads. Excellent balance between performance and power consumption. Weaknesses: Complex implementation requiring significant silicon area and development resources, potentially increasing costs for device manufacturers.

Critical Patents in Burst Efficiency Optimization

Patent

Innovation

- Advanced scheduling algorithm that balances QoS targets with burst efficiency in LPDDR5X controllers, optimizing memory access patterns while meeting latency requirements.

- Novel read-write turnaround management technique that minimizes the performance impact of direction switching in LPDDR5X memory operations, reducing idle cycles during transitions.

- Intelligent burst length selection mechanism that dynamically adjusts burst sizes based on current memory traffic conditions and QoS requirements, improving overall bandwidth utilization.

Memory control device

PatentPendingUS20250232801A1

Innovation

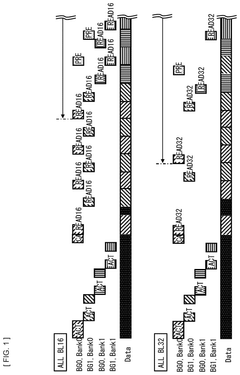

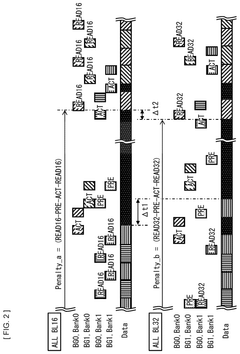

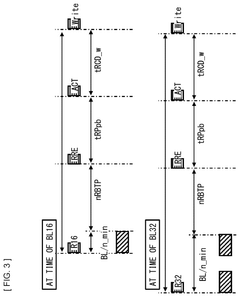

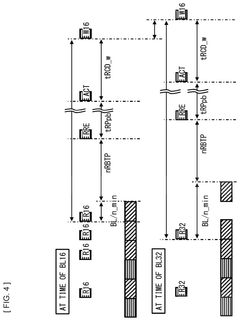

- A memory control device with a detector and converter that adjusts burst lengths based on the number of memory access requests and timing information to optimize access efficiency, converting between BL16 and BL32 in bank group interleaving.

Power Efficiency Considerations in LPDDR5X Controllers

Power efficiency has emerged as a critical consideration in LPDDR5X controller design, particularly as mobile and edge computing devices continue to demand higher performance within strict power envelopes. The LPDDR5X standard, with its increased data rates up to 8.5 Gbps, introduces significant power management challenges that must be addressed through intelligent controller design.

Memory operations constitute a substantial portion of system power consumption, with DRAM access accounting for 20-40% of total power in many mobile systems. LPDDR5X controllers must therefore implement sophisticated power management techniques to minimize energy usage while maintaining performance targets.

Dynamic voltage and frequency scaling (DVFS) represents a primary strategy for power optimization in LPDDR5X controllers. By dynamically adjusting voltage and frequency based on workload demands, controllers can significantly reduce power consumption during periods of lower memory activity. Advanced implementations incorporate predictive algorithms that anticipate workload changes to optimize DVFS transitions.

Power-aware scheduling algorithms form another crucial aspect of energy-efficient LPDDR5X controller design. These algorithms prioritize command scheduling to minimize read-write turnarounds, which are particularly power-intensive operations. By grouping similar operations and optimizing the timing of direction switches, controllers can reduce the frequency of these energy-costly transitions.

The LPDDR5X specification introduces enhanced power states that controllers must leverage effectively. These include multiple self-refresh modes and per-bank refresh capabilities that allow for more granular power management. Intelligent controllers must make real-time decisions about when to transition memory ranks or banks into these low-power states based on access patterns and QoS requirements.

Thermal management represents an additional dimension of power efficiency. LPDDR5X controllers must incorporate thermal monitoring and throttling mechanisms to prevent overheating, which can lead to both increased power consumption and reduced memory reliability. Advanced controllers implement predictive thermal models to anticipate temperature trends and adjust scheduling accordingly.

Signal integrity considerations also impact power efficiency, as higher data rates in LPDDR5X require more aggressive signal conditioning, potentially increasing power consumption. Controllers must balance signal integrity requirements with power constraints through adaptive equalization techniques and optimized I/O power management.

The relationship between burst efficiency and power consumption presents a complex optimization challenge. While maximizing burst efficiency generally improves energy efficiency by amortizing activation power across more data transfers, it may conflict with latency-sensitive QoS targets. Advanced controllers implement workload-aware policies that dynamically adjust burst parameters based on both performance requirements and power constraints.

Memory operations constitute a substantial portion of system power consumption, with DRAM access accounting for 20-40% of total power in many mobile systems. LPDDR5X controllers must therefore implement sophisticated power management techniques to minimize energy usage while maintaining performance targets.

Dynamic voltage and frequency scaling (DVFS) represents a primary strategy for power optimization in LPDDR5X controllers. By dynamically adjusting voltage and frequency based on workload demands, controllers can significantly reduce power consumption during periods of lower memory activity. Advanced implementations incorporate predictive algorithms that anticipate workload changes to optimize DVFS transitions.

Power-aware scheduling algorithms form another crucial aspect of energy-efficient LPDDR5X controller design. These algorithms prioritize command scheduling to minimize read-write turnarounds, which are particularly power-intensive operations. By grouping similar operations and optimizing the timing of direction switches, controllers can reduce the frequency of these energy-costly transitions.

The LPDDR5X specification introduces enhanced power states that controllers must leverage effectively. These include multiple self-refresh modes and per-bank refresh capabilities that allow for more granular power management. Intelligent controllers must make real-time decisions about when to transition memory ranks or banks into these low-power states based on access patterns and QoS requirements.

Thermal management represents an additional dimension of power efficiency. LPDDR5X controllers must incorporate thermal monitoring and throttling mechanisms to prevent overheating, which can lead to both increased power consumption and reduced memory reliability. Advanced controllers implement predictive thermal models to anticipate temperature trends and adjust scheduling accordingly.

Signal integrity considerations also impact power efficiency, as higher data rates in LPDDR5X require more aggressive signal conditioning, potentially increasing power consumption. Controllers must balance signal integrity requirements with power constraints through adaptive equalization techniques and optimized I/O power management.

The relationship between burst efficiency and power consumption presents a complex optimization challenge. While maximizing burst efficiency generally improves energy efficiency by amortizing activation power across more data transfers, it may conflict with latency-sensitive QoS targets. Advanced controllers implement workload-aware policies that dynamically adjust burst parameters based on both performance requirements and power constraints.

System Integration and Compatibility Standards

The integration of LPDDR5X memory controllers into complex system architectures requires adherence to established compatibility standards and protocols. These standards ensure seamless operation across diverse hardware configurations while maintaining optimal performance characteristics. The JEDEC LPDDR5X specification provides the foundational framework for controller implementation, defining signal integrity requirements, power management protocols, and timing parameters that must be respected for proper system integration.

When implementing LPDDR5X controller scheduling mechanisms, system designers must consider compatibility with existing memory subsystems and peripheral components. This includes ensuring proper interface alignment with CPU architectures, SoCs, and various chipsets that may interact with the memory controller. The scheduling algorithms must be designed to operate within the electrical and logical constraints imposed by these interconnected systems while still achieving the desired QoS targets and burst efficiency.

Thermal management represents another critical aspect of system integration. LPDDR5X controllers must incorporate temperature sensing and throttling mechanisms that comply with system-level thermal management protocols. This ensures that scheduling decisions can be dynamically adjusted based on thermal conditions without compromising system stability or violating platform-specific thermal constraints.

Power delivery networks supporting LPDDR5X controllers must adhere to voltage regulation standards that ensure clean power delivery during high-performance memory operations. The controller's scheduling algorithms need to account for power state transitions and voltage fluctuations that might occur during system operation, particularly when coordinating read-write turnarounds that can create significant current demand variations.

Firmware and driver compatibility standards play an equally important role in system integration. LPDDR5X controllers must expose standardized programming interfaces that allow operating systems and hypervisors to effectively communicate QoS requirements and memory access patterns. These interfaces typically follow industry standards such as ACPI or platform-specific memory controller interfaces to ensure broad compatibility across different software environments.

Testing and validation frameworks for LPDDR5X controllers must comply with industry-standard methodologies for memory subsystem verification. This includes conformance to established test patterns for signal integrity, timing margin analysis, and performance characterization under various operating conditions. Compliance with these testing standards ensures that the controller's scheduling mechanisms will function reliably across the full spectrum of supported platforms and use cases.

When implementing LPDDR5X controller scheduling mechanisms, system designers must consider compatibility with existing memory subsystems and peripheral components. This includes ensuring proper interface alignment with CPU architectures, SoCs, and various chipsets that may interact with the memory controller. The scheduling algorithms must be designed to operate within the electrical and logical constraints imposed by these interconnected systems while still achieving the desired QoS targets and burst efficiency.

Thermal management represents another critical aspect of system integration. LPDDR5X controllers must incorporate temperature sensing and throttling mechanisms that comply with system-level thermal management protocols. This ensures that scheduling decisions can be dynamically adjusted based on thermal conditions without compromising system stability or violating platform-specific thermal constraints.

Power delivery networks supporting LPDDR5X controllers must adhere to voltage regulation standards that ensure clean power delivery during high-performance memory operations. The controller's scheduling algorithms need to account for power state transitions and voltage fluctuations that might occur during system operation, particularly when coordinating read-write turnarounds that can create significant current demand variations.

Firmware and driver compatibility standards play an equally important role in system integration. LPDDR5X controllers must expose standardized programming interfaces that allow operating systems and hypervisors to effectively communicate QoS requirements and memory access patterns. These interfaces typically follow industry standards such as ACPI or platform-specific memory controller interfaces to ensure broad compatibility across different software environments.

Testing and validation frameworks for LPDDR5X controllers must comply with industry-standard methodologies for memory subsystem verification. This includes conformance to established test patterns for signal integrity, timing margin analysis, and performance characterization under various operating conditions. Compliance with these testing standards ensures that the controller's scheduling mechanisms will function reliably across the full spectrum of supported platforms and use cases.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!