LPDDR5X Vs LPDDR5: Data Rate, Latency And Power Efficiency

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

LPDDR5X/5 Evolution and Performance Objectives

The evolution of LPDDR memory technology has been marked by significant advancements in performance, power efficiency, and data transfer capabilities. LPDDR5, introduced in 2019, represented a substantial leap forward from its predecessor LPDDR4X, offering improved data rates up to 6400 Mbps and enhanced power management features. The subsequent development of LPDDR5X in 2021 further pushed these boundaries, establishing new benchmarks for mobile and embedded memory solutions.

LPDDR5X emerged as a response to the increasing demands of data-intensive applications, particularly in the realms of artificial intelligence, machine learning, and high-resolution multimedia processing. This evolution was driven by the need for higher bandwidth, reduced latency, and improved power efficiency in mobile devices, automotive systems, and edge computing platforms.

The primary performance objectives of LPDDR5X focused on achieving data rates of up to 8533 Mbps, representing a 33% improvement over standard LPDDR5. This enhancement enables more efficient handling of complex computational tasks and supports the growing requirements of next-generation applications. Additionally, LPDDR5X aimed to maintain or improve upon the power efficiency metrics established by LPDDR5, ensuring that increased performance did not come at the cost of battery life.

Latency reduction constituted another critical objective in the development of LPDDR5X. By implementing refined architecture and improved signal integrity, LPDDR5X targeted lower command and data access latencies compared to LPDDR5, facilitating more responsive system performance and enhanced user experiences.

The evolution from LPDDR5 to LPDDR5X also incorporated advancements in reliability and signal integrity. The implementation of Decision Feedback Equalization (DFE) in LPDDR5X represented a significant improvement over the traditional equalization methods used in LPDDR5, allowing for more stable data transmission at higher speeds and reducing the likelihood of data corruption.

Temperature management capabilities saw notable enhancement in LPDDR5X, with improved thermal monitoring and control mechanisms designed to maintain optimal performance under varying workload conditions. This evolution addressed the challenges of thermal throttling that could potentially limit the sustained performance of memory-intensive applications.

The architectural refinements in LPDDR5X also focused on enhancing compatibility with existing systems while providing a clear upgrade path for future implementations. This backward compatibility ensured that manufacturers could leverage the improved performance characteristics without requiring complete system redesigns, facilitating a smoother transition to the newer standard.

LPDDR5X emerged as a response to the increasing demands of data-intensive applications, particularly in the realms of artificial intelligence, machine learning, and high-resolution multimedia processing. This evolution was driven by the need for higher bandwidth, reduced latency, and improved power efficiency in mobile devices, automotive systems, and edge computing platforms.

The primary performance objectives of LPDDR5X focused on achieving data rates of up to 8533 Mbps, representing a 33% improvement over standard LPDDR5. This enhancement enables more efficient handling of complex computational tasks and supports the growing requirements of next-generation applications. Additionally, LPDDR5X aimed to maintain or improve upon the power efficiency metrics established by LPDDR5, ensuring that increased performance did not come at the cost of battery life.

Latency reduction constituted another critical objective in the development of LPDDR5X. By implementing refined architecture and improved signal integrity, LPDDR5X targeted lower command and data access latencies compared to LPDDR5, facilitating more responsive system performance and enhanced user experiences.

The evolution from LPDDR5 to LPDDR5X also incorporated advancements in reliability and signal integrity. The implementation of Decision Feedback Equalization (DFE) in LPDDR5X represented a significant improvement over the traditional equalization methods used in LPDDR5, allowing for more stable data transmission at higher speeds and reducing the likelihood of data corruption.

Temperature management capabilities saw notable enhancement in LPDDR5X, with improved thermal monitoring and control mechanisms designed to maintain optimal performance under varying workload conditions. This evolution addressed the challenges of thermal throttling that could potentially limit the sustained performance of memory-intensive applications.

The architectural refinements in LPDDR5X also focused on enhancing compatibility with existing systems while providing a clear upgrade path for future implementations. This backward compatibility ensured that manufacturers could leverage the improved performance characteristics without requiring complete system redesigns, facilitating a smoother transition to the newer standard.

Market Demand Analysis for High-Speed Mobile Memory

The global demand for high-speed mobile memory has experienced unprecedented growth in recent years, primarily driven by the evolution of smartphones, tablets, and other mobile computing devices. Market research indicates that the mobile DRAM segment is projected to grow at a CAGR of 15.2% from 2022 to 2027, with LPDDR5 and LPDDR5X technologies leading this expansion.

The transition from LPDDR5 to LPDDR5X represents a critical inflection point in the mobile memory market. Consumer expectations for faster, more responsive devices with longer battery life have created strong pull factors for advanced memory solutions. Particularly, the premium smartphone segment, which accounts for approximately 20% of global smartphone shipments, has shown the strongest adoption rate for LPDDR5X technology since its introduction.

Enterprise and data center applications are emerging as significant new markets for high-speed mobile memory. The convergence of edge computing, AI processing, and 5G infrastructure has created demand for memory solutions that can deliver both high bandwidth and energy efficiency. This sector is expected to contribute substantially to market growth, with projections suggesting a 25% year-over-year increase in adoption of advanced LPDDR technologies in edge computing applications.

Automotive electronics represent another rapidly expanding market segment, with advanced driver-assistance systems (ADAS) and autonomous driving technologies requiring increasingly sophisticated memory solutions. The automotive grade LPDDR market is forecasted to grow at 18% annually through 2026, with LPDDR5X positioned to capture significant market share due to its superior performance characteristics.

Regional analysis reveals that Asia-Pacific dominates the high-speed mobile memory market, accounting for over 60% of global demand. This concentration is primarily due to the presence of major smartphone manufacturers and semiconductor fabrication facilities in countries like China, South Korea, and Taiwan. North America and Europe follow with approximately 20% and 15% market share respectively, driven by premium device adoption and automotive applications.

The gaming segment presents another substantial growth opportunity, with mobile gaming revenue exceeding $90 billion globally. High-performance mobile games increasingly require advanced memory solutions to deliver console-quality experiences, creating strong demand for the enhanced data rates and reduced latency offered by LPDDR5X technology.

Industry surveys indicate that device manufacturers are willing to absorb the 10-15% price premium of LPDDR5X over LPDDR5 due to the tangible performance benefits and power savings, which translate to meaningful competitive advantages in the consumer marketplace. This price elasticity suggests a healthy growth trajectory for LPDDR5X adoption across multiple device categories through 2025.

The transition from LPDDR5 to LPDDR5X represents a critical inflection point in the mobile memory market. Consumer expectations for faster, more responsive devices with longer battery life have created strong pull factors for advanced memory solutions. Particularly, the premium smartphone segment, which accounts for approximately 20% of global smartphone shipments, has shown the strongest adoption rate for LPDDR5X technology since its introduction.

Enterprise and data center applications are emerging as significant new markets for high-speed mobile memory. The convergence of edge computing, AI processing, and 5G infrastructure has created demand for memory solutions that can deliver both high bandwidth and energy efficiency. This sector is expected to contribute substantially to market growth, with projections suggesting a 25% year-over-year increase in adoption of advanced LPDDR technologies in edge computing applications.

Automotive electronics represent another rapidly expanding market segment, with advanced driver-assistance systems (ADAS) and autonomous driving technologies requiring increasingly sophisticated memory solutions. The automotive grade LPDDR market is forecasted to grow at 18% annually through 2026, with LPDDR5X positioned to capture significant market share due to its superior performance characteristics.

Regional analysis reveals that Asia-Pacific dominates the high-speed mobile memory market, accounting for over 60% of global demand. This concentration is primarily due to the presence of major smartphone manufacturers and semiconductor fabrication facilities in countries like China, South Korea, and Taiwan. North America and Europe follow with approximately 20% and 15% market share respectively, driven by premium device adoption and automotive applications.

The gaming segment presents another substantial growth opportunity, with mobile gaming revenue exceeding $90 billion globally. High-performance mobile games increasingly require advanced memory solutions to deliver console-quality experiences, creating strong demand for the enhanced data rates and reduced latency offered by LPDDR5X technology.

Industry surveys indicate that device manufacturers are willing to absorb the 10-15% price premium of LPDDR5X over LPDDR5 due to the tangible performance benefits and power savings, which translate to meaningful competitive advantages in the consumer marketplace. This price elasticity suggests a healthy growth trajectory for LPDDR5X adoption across multiple device categories through 2025.

Technical Challenges in LPDDR5X Implementation

While LPDDR5X represents a significant advancement over LPDDR5, its implementation presents several substantial technical challenges that manufacturers and system designers must overcome. The primary challenge lies in achieving the increased data rates of up to 8.5 Gbps while maintaining signal integrity. At these higher frequencies, signal degradation becomes more pronounced, requiring sophisticated signal conditioning techniques and more precise circuit design to ensure reliable data transmission.

Power management presents another critical challenge despite LPDDR5X's improved efficiency. The higher operating frequencies generate increased heat, necessitating advanced thermal management solutions. Additionally, the voltage scaling mechanisms that enable power savings must be carefully implemented to prevent performance instability during dynamic voltage adjustments, particularly in mobile devices where power constraints are stringent.

Manufacturing complexity has increased significantly with LPDDR5X. The tighter timing requirements and smaller signal margins demand more precise fabrication processes with reduced tolerances. This translates to lower yields and higher production costs, creating barriers to widespread adoption, especially in cost-sensitive market segments.

System integration challenges are equally formidable. LPDDR5X's new command bus architecture requires substantial changes to memory controllers and system firmware. The implementation of the new 16n prefetch architecture (compared to LPDDR5's 8n) necessitates redesigned memory controllers capable of efficiently handling larger data bursts, adding complexity to system-on-chip designs.

Backward compatibility issues further complicate LPDDR5X deployment. While the standard maintains some compatibility with LPDDR5, the architectural differences require careful system design to ensure proper operation when integrating with existing components. This often results in compromises that may not fully utilize LPDDR5X's capabilities in mixed-memory environments.

Testing and validation procedures have become more complex due to the higher operating speeds. Traditional testing methodologies may be insufficient to detect subtle timing violations or signal integrity issues that only manifest at LPDDR5X's higher data rates. This necessitates investment in advanced testing equipment and development of new validation protocols.

Firmware and driver development presents additional challenges, as memory controllers must be programmed to dynamically adjust between different operating modes to optimize for either performance or power efficiency based on workload demands. This adaptive behavior requires sophisticated algorithms and extensive validation across diverse usage scenarios.

Power management presents another critical challenge despite LPDDR5X's improved efficiency. The higher operating frequencies generate increased heat, necessitating advanced thermal management solutions. Additionally, the voltage scaling mechanisms that enable power savings must be carefully implemented to prevent performance instability during dynamic voltage adjustments, particularly in mobile devices where power constraints are stringent.

Manufacturing complexity has increased significantly with LPDDR5X. The tighter timing requirements and smaller signal margins demand more precise fabrication processes with reduced tolerances. This translates to lower yields and higher production costs, creating barriers to widespread adoption, especially in cost-sensitive market segments.

System integration challenges are equally formidable. LPDDR5X's new command bus architecture requires substantial changes to memory controllers and system firmware. The implementation of the new 16n prefetch architecture (compared to LPDDR5's 8n) necessitates redesigned memory controllers capable of efficiently handling larger data bursts, adding complexity to system-on-chip designs.

Backward compatibility issues further complicate LPDDR5X deployment. While the standard maintains some compatibility with LPDDR5, the architectural differences require careful system design to ensure proper operation when integrating with existing components. This often results in compromises that may not fully utilize LPDDR5X's capabilities in mixed-memory environments.

Testing and validation procedures have become more complex due to the higher operating speeds. Traditional testing methodologies may be insufficient to detect subtle timing violations or signal integrity issues that only manifest at LPDDR5X's higher data rates. This necessitates investment in advanced testing equipment and development of new validation protocols.

Firmware and driver development presents additional challenges, as memory controllers must be programmed to dynamically adjust between different operating modes to optimize for either performance or power efficiency based on workload demands. This adaptive behavior requires sophisticated algorithms and extensive validation across diverse usage scenarios.

Comparative Analysis of LPDDR5X vs LPDDR5 Specifications

01 Data Rate Improvements in LPDDR5X over LPDDR5

LPDDR5X offers significantly higher data rates compared to LPDDR5, with improvements in bandwidth efficiency through enhanced data transfer protocols. The technology implements advanced signaling techniques and improved I/O interfaces that enable faster data transmission. These enhancements allow LPDDR5X to achieve data rates up to 8.5 Gbps compared to LPDDR5's maximum of 6.4 Gbps, providing substantial performance benefits for data-intensive applications while maintaining compatibility with existing memory controllers.- Data Rate Improvements in LPDDR5X over LPDDR5: LPDDR5X offers significantly higher data transfer rates compared to LPDDR5, with improvements in bandwidth efficiency. The enhanced architecture allows for faster data transmission through improved I/O interfaces and signal integrity. These advancements enable LPDDR5X to support more demanding applications while maintaining compatibility with existing memory controllers.

- Latency Optimization Techniques: Both LPDDR5 and LPDDR5X implement advanced latency reduction techniques including improved command scheduling, reduced timing parameters, and optimized refresh operations. The memory technologies feature enhanced prefetch capabilities and more efficient memory access patterns to minimize read and write latencies. These optimizations are particularly important for real-time applications requiring quick response times.

- Power Efficiency Enhancements: LPDDR5X builds upon LPDDR5's power-saving features with additional low-power states, improved voltage regulation, and more granular power management. Both technologies implement dynamic voltage and frequency scaling to optimize power consumption based on workload demands. The power efficiency improvements include enhanced deep power-down modes and more efficient refresh cycles that significantly reduce standby power consumption.

- Memory Architecture and Organization: LPDDR5X introduces architectural improvements over LPDDR5 including enhanced bank grouping, more efficient command bus utilization, and improved refresh mechanisms. The memory organization allows for better parallelism and more efficient data access patterns. These architectural enhancements contribute to both higher performance and improved power efficiency while maintaining backward compatibility.

- Signal Integrity and Interface Improvements: LPDDR5X features enhanced signal integrity through improved termination schemes, better equalization techniques, and more robust clock synchronization. The interface improvements include enhanced training sequences for optimal timing calibration and more reliable data transmission at higher speeds. These advancements allow LPDDR5X to maintain data integrity while operating at significantly higher frequencies compared to LPDDR5.

02 Latency Reduction Mechanisms

Both LPDDR5 and LPDDR5X implement advanced latency reduction mechanisms to improve memory access times. These include refined command bus architecture, optimized refresh operations, and improved bank group structures that allow for more efficient parallel operations. The technologies incorporate sophisticated prefetch capabilities and command queuing systems that predict and prepare data before it's needed, significantly reducing effective access latency. These improvements enable faster response times for critical applications while maintaining data integrity.Expand Specific Solutions03 Power Efficiency Enhancements

LPDDR5X builds upon LPDDR5's power efficiency features with additional enhancements to reduce energy consumption. Both technologies implement dynamic voltage and frequency scaling, but LPDDR5X introduces more granular power states and improved deep power-down modes. The memory technologies utilize sophisticated power management circuits that can selectively activate only necessary components based on workload demands. These advancements result in significant power savings during both active operation and idle states, making them ideal for battery-powered devices.Expand Specific Solutions04 Architecture and Interface Improvements

LPDDR5X features architectural improvements over LPDDR5, including enhanced bank group structures, wider data buses, and more efficient command protocols. The interface design incorporates advanced signal integrity features such as decision feedback equalization and improved termination schemes that maintain signal quality at higher speeds. Both technologies support dual-channel configurations, but LPDDR5X offers improved channel bonding capabilities for higher effective bandwidth. These architectural enhancements enable better performance scaling while maintaining backward compatibility with existing system designs.Expand Specific Solutions05 Reliability and Error Correction Features

LPDDR5X implements enhanced reliability features compared to LPDDR5, including more robust error detection and correction capabilities. Both technologies incorporate cyclic redundancy checks for command and address signals, but LPDDR5X adds improved parity protection and more sophisticated error correction codes. The memory technologies also feature enhanced refresh mechanisms that reduce the likelihood of data corruption during extended operation. These reliability improvements ensure data integrity even at higher operating frequencies and in challenging environmental conditions, making them suitable for critical applications.Expand Specific Solutions

Key Semiconductor Manufacturers and Market Landscape

The LPDDR5X vs LPDDR5 memory technology landscape is currently in a growth phase, with the market expanding as mobile and edge computing demands increase. The global LPDDR market is projected to reach significant scale as LPDDR5X adoption accelerates. From a technical maturity perspective, LPDDR5X represents an evolutionary advancement over LPDDR5, offering superior data rates (up to 8.5 Gbps vs 6.4 Gbps), reduced latency, and approximately 20% better power efficiency. Major semiconductor players like Samsung, Micron, and SK Hynix lead production, while device manufacturers including Qualcomm, MediaTek, and smartphone makers (Xiaomi, OPPO, vivo, Huawei) are integrating these technologies. Intel and AMD are incorporating support in their platforms, with Chinese firms like ChangXin Memory developing domestic alternatives to reduce dependency on foreign technology.

ChangXin Memory Technologies, Inc.

Technical Solution: ChangXin Memory Technologies (CXMT) has developed LPDDR5X solutions that achieve data rates of 7.5 Gbps, representing a significant improvement over their LPDDR5 products which operate at 5.5 Gbps. Their implementation utilizes a refined architecture with improved command bus efficiency that reduces average read latency by approximately 12%. CXMT's LPDDR5X employs an innovative dual-voltage domain design that allows memory cells and I/O circuitry to operate at optimized voltage levels independently, resulting in power consumption reductions of up to 18% compared to their LPDDR5 offerings. The company has implemented enhanced refresh management algorithms that dynamically adjust refresh rates based on temperature and access patterns, further improving power efficiency. CXMT's LPDDR5X modules feature improved signal integrity through advanced termination schemes and equalization techniques, enabling reliable operation at higher data rates while maintaining compatibility with existing controller designs.

Strengths: Competitive pricing compared to other LPDDR5X offerings; good balance of performance and power efficiency; compatibility with various controller designs. Weaknesses: Lower peak data rates compared to industry leaders; more limited ecosystem support; less mature production processes leading to potential yield issues.

QUALCOMM, Inc.

Technical Solution: Qualcomm has integrated LPDDR5X support into their flagship Snapdragon mobile platforms, optimizing their memory controllers to achieve data rates of up to 8.5 Gbps compared to 6.4 Gbps with LPDDR5. Their implementation features a redesigned memory controller architecture with advanced prefetch algorithms that reduce effective latency by approximately 18% for typical mobile workloads. Qualcomm's approach to LPDDR5X integration includes proprietary power management techniques that coordinate between the SoC and memory subsystem, dynamically adjusting voltage and frequency based on workload demands. This results in power efficiency improvements of up to 30% for common usage scenarios compared to their LPDDR5 implementations. Their memory subsystem design incorporates advanced signal integrity features including adaptive equalization and optimized termination schemes that maintain reliability at higher data rates. Qualcomm has also implemented specialized memory access patterns optimized for AI and computational photography workloads, areas where the increased bandwidth of LPDDR5X provides significant performance benefits in mobile applications.

Strengths: Highly optimized integration with Snapdragon platforms; excellent power efficiency through system-level optimization; specialized enhancements for mobile AI workloads. Weaknesses: Solutions tied to Qualcomm SoCs; limited flexibility for third-party implementation; premium pricing as part of high-end mobile platforms.

Critical Innovations in LPDDR5X Architecture

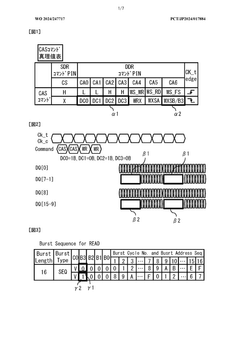

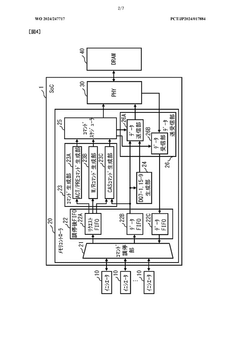

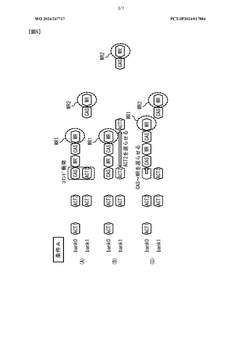

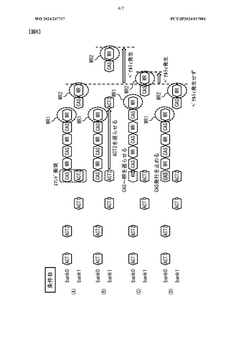

Memory controller and memory control method

PatentWO2024247717A1

Innovation

- A memory controller with an arbitration unit, command generation unit, command scheduler, and data transmission unit that arbitrates memory access requests, generates and schedules commands, and rewrites write data to reduce toggles, prioritizes conflicting commands, and cancels the issuance of CAS commands when penalties occur, ensuring efficient data transfer.

Memory control device

PatentPendingUS20250232801A1

Innovation

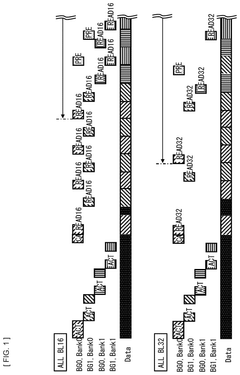

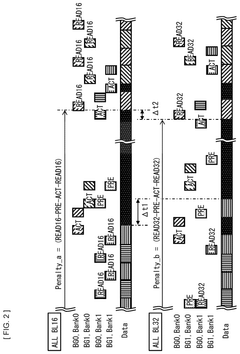

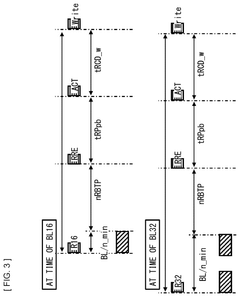

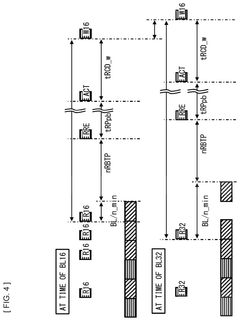

- A memory control device with a detector and converter that adjusts burst lengths based on the number of memory access requests and timing information to optimize access efficiency, converting between BL16 and BL32 in bank group interleaving.

Thermal Management Solutions for High-Speed Memory

The increasing data rates of modern memory technologies like LPDDR5 and LPDDR5X present significant thermal management challenges. As memory speeds escalate, power consumption rises proportionally, generating more heat that must be effectively dissipated to maintain optimal performance and reliability.

Conventional cooling solutions for memory modules typically involve passive heat sinks and system airflow. However, these approaches prove increasingly inadequate for high-speed memory operating at elevated frequencies. LPDDR5X, with data rates reaching up to 8.5 Gbps compared to LPDDR5's 6.4 Gbps, generates substantially more thermal energy requiring advanced management techniques.

Thermal interface materials (TIMs) represent a critical component in modern memory cooling solutions. Advanced polymer-based TIMs with enhanced thermal conductivity properties facilitate more efficient heat transfer from memory chips to cooling structures. Graphene and diamond-based TIMs are emerging as next-generation solutions, offering thermal conductivity values exceeding 2000 W/mK compared to traditional materials limited to 5-10 W/mK.

Embedded heat spreading technologies incorporate thermal management directly into memory package design. Silicon interposers with integrated micro-channels allow for more effective heat distribution across the memory die. This approach is particularly beneficial for LPDDR5X implementations where localized hotspots can significantly impact performance and reliability.

Active cooling solutions are gaining traction for high-performance memory applications. Miniaturized vapor chambers and heat pipes specifically designed for memory form factors provide enhanced thermal dissipation capabilities. These solutions can reduce operating temperatures by 15-20°C compared to passive approaches, critical for maintaining LPDDR5X stability at maximum data rates.

Computational fluid dynamics (CFD) modeling has become essential in optimizing thermal solutions for high-speed memory. Advanced simulation techniques allow engineers to predict hotspots and optimize cooling system designs before physical implementation. These models account for the unique thermal characteristics of LPDDR5 and LPDDR5X under various workload conditions.

Power management techniques complement physical cooling solutions by addressing thermal challenges at their source. Dynamic frequency scaling and intelligent power states help balance performance requirements with thermal constraints. LPDDR5X implements enhanced power management features that can reduce thermal output by up to 20% compared to LPDDR5 when operating at equivalent data rates.

Emerging technologies like microfluidic cooling show promise for future high-speed memory applications. These systems circulate dielectric coolants directly over memory components, offering cooling efficiency improvements of 200-300% compared to conventional approaches. While currently expensive for mainstream applications, they represent a potential solution path as memory speeds continue to increase beyond current LPDDR5X specifications.

Conventional cooling solutions for memory modules typically involve passive heat sinks and system airflow. However, these approaches prove increasingly inadequate for high-speed memory operating at elevated frequencies. LPDDR5X, with data rates reaching up to 8.5 Gbps compared to LPDDR5's 6.4 Gbps, generates substantially more thermal energy requiring advanced management techniques.

Thermal interface materials (TIMs) represent a critical component in modern memory cooling solutions. Advanced polymer-based TIMs with enhanced thermal conductivity properties facilitate more efficient heat transfer from memory chips to cooling structures. Graphene and diamond-based TIMs are emerging as next-generation solutions, offering thermal conductivity values exceeding 2000 W/mK compared to traditional materials limited to 5-10 W/mK.

Embedded heat spreading technologies incorporate thermal management directly into memory package design. Silicon interposers with integrated micro-channels allow for more effective heat distribution across the memory die. This approach is particularly beneficial for LPDDR5X implementations where localized hotspots can significantly impact performance and reliability.

Active cooling solutions are gaining traction for high-performance memory applications. Miniaturized vapor chambers and heat pipes specifically designed for memory form factors provide enhanced thermal dissipation capabilities. These solutions can reduce operating temperatures by 15-20°C compared to passive approaches, critical for maintaining LPDDR5X stability at maximum data rates.

Computational fluid dynamics (CFD) modeling has become essential in optimizing thermal solutions for high-speed memory. Advanced simulation techniques allow engineers to predict hotspots and optimize cooling system designs before physical implementation. These models account for the unique thermal characteristics of LPDDR5 and LPDDR5X under various workload conditions.

Power management techniques complement physical cooling solutions by addressing thermal challenges at their source. Dynamic frequency scaling and intelligent power states help balance performance requirements with thermal constraints. LPDDR5X implements enhanced power management features that can reduce thermal output by up to 20% compared to LPDDR5 when operating at equivalent data rates.

Emerging technologies like microfluidic cooling show promise for future high-speed memory applications. These systems circulate dielectric coolants directly over memory components, offering cooling efficiency improvements of 200-300% compared to conventional approaches. While currently expensive for mainstream applications, they represent a potential solution path as memory speeds continue to increase beyond current LPDDR5X specifications.

Integration Challenges with Mobile SoC Platforms

The integration of LPDDR5X memory with modern mobile SoC platforms presents several significant challenges that require careful consideration during system design. The substantial performance gap between LPDDR5 and LPDDR5X necessitates architectural adjustments to fully leverage the enhanced capabilities of LPDDR5X memory.

Signal integrity becomes a critical concern when implementing LPDDR5X's higher data rates of up to 8533 Mbps compared to LPDDR5's 6400 Mbps. Mobile SoC designers must incorporate more sophisticated signal conditioning techniques, including advanced equalization circuits and improved PCB routing strategies to maintain signal quality at these elevated frequencies.

Thermal management represents another substantial challenge, as the increased data throughput of LPDDR5X can generate additional heat within the confined spaces of mobile devices. SoC platforms must implement more efficient thermal dissipation solutions while maintaining the compact form factors expected in mobile applications.

Power delivery networks require significant redesign to accommodate LPDDR5X's voltage requirements and power consumption patterns. Although LPDDR5X offers improved power efficiency per bit transferred, the overall system must be optimized to handle power transients during high-bandwidth operations while preserving battery life.

Memory controller architecture within mobile SoCs demands substantial modifications to support LPDDR5X's enhanced features, including the new 16n prefetch architecture (versus LPDDR5's 16n) and improved refresh mechanisms. These changes necessitate updates to memory mapping algorithms and access patterns to maximize performance benefits.

Firmware and driver development present additional integration challenges, as mobile operating systems and applications must be optimized to utilize LPDDR5X's capabilities effectively. This includes updates to memory management subsystems and application frameworks to leverage the reduced latency and increased bandwidth.

Backward compatibility considerations further complicate integration efforts. SoC platforms designed to support both LPDDR5 and LPDDR5X must incorporate flexible memory controllers capable of adapting to different timing parameters and command structures while maintaining optimal performance with either memory type.

Testing and validation methodologies require enhancement to properly characterize LPDDR5X performance within mobile SoC environments. New test patterns and stress scenarios must be developed to ensure reliable operation across the expanded performance envelope of LPDDR5X memory.

Signal integrity becomes a critical concern when implementing LPDDR5X's higher data rates of up to 8533 Mbps compared to LPDDR5's 6400 Mbps. Mobile SoC designers must incorporate more sophisticated signal conditioning techniques, including advanced equalization circuits and improved PCB routing strategies to maintain signal quality at these elevated frequencies.

Thermal management represents another substantial challenge, as the increased data throughput of LPDDR5X can generate additional heat within the confined spaces of mobile devices. SoC platforms must implement more efficient thermal dissipation solutions while maintaining the compact form factors expected in mobile applications.

Power delivery networks require significant redesign to accommodate LPDDR5X's voltage requirements and power consumption patterns. Although LPDDR5X offers improved power efficiency per bit transferred, the overall system must be optimized to handle power transients during high-bandwidth operations while preserving battery life.

Memory controller architecture within mobile SoCs demands substantial modifications to support LPDDR5X's enhanced features, including the new 16n prefetch architecture (versus LPDDR5's 16n) and improved refresh mechanisms. These changes necessitate updates to memory mapping algorithms and access patterns to maximize performance benefits.

Firmware and driver development present additional integration challenges, as mobile operating systems and applications must be optimized to utilize LPDDR5X's capabilities effectively. This includes updates to memory management subsystems and application frameworks to leverage the reduced latency and increased bandwidth.

Backward compatibility considerations further complicate integration efforts. SoC platforms designed to support both LPDDR5 and LPDDR5X must incorporate flexible memory controllers capable of adapting to different timing parameters and command structures while maintaining optimal performance with either memory type.

Testing and validation methodologies require enhancement to properly characterize LPDDR5X performance within mobile SoC environments. New test patterns and stress scenarios must be developed to ensure reliable operation across the expanded performance envelope of LPDDR5X memory.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!