How to Leverage Logic Chips for Intelligent Network Solutions

APR 2, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Logic Chip Intelligence Network Background and Objectives

The evolution of logic chips has fundamentally transformed the landscape of network infrastructure, progressing from simple switching components to sophisticated processing units capable of intelligent decision-making. Traditional network architectures relied heavily on dedicated hardware for specific functions, creating rigid systems with limited adaptability. The emergence of programmable logic devices, field-programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs) has revolutionized this paradigm by enabling dynamic reconfiguration and real-time processing capabilities within network nodes.

Modern intelligent networks demand unprecedented levels of performance, flexibility, and autonomous operation. The exponential growth in data traffic, driven by cloud computing, Internet of Things (IoT) deployments, and edge computing applications, has created bottlenecks that conventional network solutions cannot adequately address. Logic chips offer a compelling solution by providing hardware-accelerated processing power directly at network junction points, enabling real-time analytics, traffic optimization, and adaptive routing decisions without relying on centralized processing units.

The convergence of artificial intelligence and network infrastructure has established new requirements for distributed intelligence capabilities. Logic chips equipped with machine learning accelerators can perform pattern recognition, anomaly detection, and predictive maintenance functions directly within network equipment. This distributed approach reduces latency, improves system resilience, and enables autonomous network management capabilities that were previously impossible with traditional architectures.

The primary objective of leveraging logic chips for intelligent network solutions centers on achieving autonomous network operation through embedded intelligence. This involves developing systems capable of self-optimization, automatic fault detection and recovery, and dynamic resource allocation based on real-time network conditions. The integration aims to create networks that can adapt to changing traffic patterns, security threats, and performance requirements without human intervention.

Another critical objective focuses on enhancing network performance through hardware acceleration of critical functions. Logic chips can offload computationally intensive tasks such as encryption, compression, and protocol processing from general-purpose processors, significantly improving throughput and reducing power consumption. This hardware-software co-design approach enables networks to handle increasing data volumes while maintaining low latency and high reliability standards.

The strategic goal encompasses creating scalable and future-proof network infrastructures that can evolve with emerging technologies. By incorporating programmable logic elements, networks can be updated and enhanced through firmware modifications rather than complete hardware replacements, extending equipment lifecycles and reducing operational costs while maintaining cutting-edge capabilities.

Modern intelligent networks demand unprecedented levels of performance, flexibility, and autonomous operation. The exponential growth in data traffic, driven by cloud computing, Internet of Things (IoT) deployments, and edge computing applications, has created bottlenecks that conventional network solutions cannot adequately address. Logic chips offer a compelling solution by providing hardware-accelerated processing power directly at network junction points, enabling real-time analytics, traffic optimization, and adaptive routing decisions without relying on centralized processing units.

The convergence of artificial intelligence and network infrastructure has established new requirements for distributed intelligence capabilities. Logic chips equipped with machine learning accelerators can perform pattern recognition, anomaly detection, and predictive maintenance functions directly within network equipment. This distributed approach reduces latency, improves system resilience, and enables autonomous network management capabilities that were previously impossible with traditional architectures.

The primary objective of leveraging logic chips for intelligent network solutions centers on achieving autonomous network operation through embedded intelligence. This involves developing systems capable of self-optimization, automatic fault detection and recovery, and dynamic resource allocation based on real-time network conditions. The integration aims to create networks that can adapt to changing traffic patterns, security threats, and performance requirements without human intervention.

Another critical objective focuses on enhancing network performance through hardware acceleration of critical functions. Logic chips can offload computationally intensive tasks such as encryption, compression, and protocol processing from general-purpose processors, significantly improving throughput and reducing power consumption. This hardware-software co-design approach enables networks to handle increasing data volumes while maintaining low latency and high reliability standards.

The strategic goal encompasses creating scalable and future-proof network infrastructures that can evolve with emerging technologies. By incorporating programmable logic elements, networks can be updated and enhanced through firmware modifications rather than complete hardware replacements, extending equipment lifecycles and reducing operational costs while maintaining cutting-edge capabilities.

Market Demand for Intelligent Network Infrastructure Solutions

The global intelligent network infrastructure market is experiencing unprecedented growth driven by the digital transformation across industries and the proliferation of connected devices. Organizations worldwide are increasingly demanding network solutions that can autonomously adapt, optimize performance, and provide predictive maintenance capabilities. This surge in demand stems from the exponential increase in data traffic, the need for ultra-low latency applications, and the complexity of managing heterogeneous network environments.

Enterprise networks are evolving beyond traditional static configurations toward dynamic, self-healing systems that can respond to changing conditions in real-time. The rise of edge computing, Internet of Things deployments, and artificial intelligence applications has created a pressing need for network infrastructure that can process and analyze data at unprecedented speeds while maintaining reliability and security. Logic chips serve as the foundational technology enabling these intelligent capabilities through their ability to perform complex computations and decision-making processes at the hardware level.

Telecommunications service providers are particularly driving demand for intelligent network solutions as they transition to software-defined networks and network function virtualization. The deployment of advanced wireless technologies requires network infrastructure capable of handling massive data volumes while optimizing resource allocation and ensuring quality of service. Logic chips embedded within network equipment enable real-time traffic analysis, automated load balancing, and predictive failure detection.

The data center segment represents another significant demand driver, where operators seek solutions that can optimize power consumption, enhance security, and improve overall operational efficiency. Modern data centers require intelligent switching and routing capabilities that can adapt to varying workloads and automatically reconfigure network paths to maintain optimal performance. Logic chips facilitate these advanced functionalities by providing the computational power necessary for complex algorithmic processing within network hardware.

Cloud service providers are increasingly investing in intelligent network infrastructure to support their expanding service portfolios and ensure competitive advantage. The demand extends beyond basic connectivity to encompass advanced features such as network slicing, quality of service guarantees, and automated security threat detection. These requirements necessitate sophisticated logic chip implementations that can execute multiple parallel processing tasks while maintaining deterministic performance characteristics.

The market demand is further amplified by regulatory requirements for network security and data protection, driving organizations to seek intelligent solutions capable of real-time threat detection and automated response mechanisms. Logic chips enable the implementation of hardware-based security features and encryption capabilities that provide enhanced protection compared to software-only approaches.

Enterprise networks are evolving beyond traditional static configurations toward dynamic, self-healing systems that can respond to changing conditions in real-time. The rise of edge computing, Internet of Things deployments, and artificial intelligence applications has created a pressing need for network infrastructure that can process and analyze data at unprecedented speeds while maintaining reliability and security. Logic chips serve as the foundational technology enabling these intelligent capabilities through their ability to perform complex computations and decision-making processes at the hardware level.

Telecommunications service providers are particularly driving demand for intelligent network solutions as they transition to software-defined networks and network function virtualization. The deployment of advanced wireless technologies requires network infrastructure capable of handling massive data volumes while optimizing resource allocation and ensuring quality of service. Logic chips embedded within network equipment enable real-time traffic analysis, automated load balancing, and predictive failure detection.

The data center segment represents another significant demand driver, where operators seek solutions that can optimize power consumption, enhance security, and improve overall operational efficiency. Modern data centers require intelligent switching and routing capabilities that can adapt to varying workloads and automatically reconfigure network paths to maintain optimal performance. Logic chips facilitate these advanced functionalities by providing the computational power necessary for complex algorithmic processing within network hardware.

Cloud service providers are increasingly investing in intelligent network infrastructure to support their expanding service portfolios and ensure competitive advantage. The demand extends beyond basic connectivity to encompass advanced features such as network slicing, quality of service guarantees, and automated security threat detection. These requirements necessitate sophisticated logic chip implementations that can execute multiple parallel processing tasks while maintaining deterministic performance characteristics.

The market demand is further amplified by regulatory requirements for network security and data protection, driving organizations to seek intelligent solutions capable of real-time threat detection and automated response mechanisms. Logic chips enable the implementation of hardware-based security features and encryption capabilities that provide enhanced protection compared to software-only approaches.

Current State and Challenges of Logic Chip Network Applications

Logic chips have emerged as fundamental components in modern network infrastructure, serving as the computational backbone for intelligent network solutions. Currently, these semiconductor devices are primarily deployed in network switches, routers, and data processing units where they handle packet forwarding, traffic management, and protocol processing. The integration of logic chips in network applications has evolved from simple switching functions to complex programmable platforms capable of supporting software-defined networking and network function virtualization.

The present landscape of logic chip network applications spans multiple domains including telecommunications infrastructure, enterprise networking, and cloud computing environments. Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs) dominate the market, with major deployments in 5G base stations, high-frequency trading networks, and hyperscale data centers. These implementations demonstrate varying degrees of intelligence, from basic rule-based processing to machine learning-enabled traffic optimization.

Despite significant progress, several critical challenges impede the full realization of intelligent network solutions using logic chips. Power consumption remains a primary constraint, particularly in edge computing scenarios where thermal management and energy efficiency are paramount. The complexity of programming and configuring logic chips for network applications creates substantial barriers for widespread adoption, requiring specialized expertise that is often scarce in the industry.

Latency optimization presents another significant challenge, especially in real-time applications such as autonomous vehicle networks and industrial IoT systems. While logic chips offer superior processing capabilities compared to traditional software-based solutions, achieving consistent sub-microsecond response times across diverse network conditions remains problematic. Additionally, the integration of artificial intelligence algorithms directly onto logic chips faces limitations in memory bandwidth and computational parallelism.

Scalability issues emerge when deploying logic chip-based solutions across heterogeneous network environments. The lack of standardized interfaces and programming models creates fragmentation, making it difficult to achieve seamless interoperability between different vendors' solutions. Security vulnerabilities also pose growing concerns, as the increased complexity of logic chip firmware and the potential for hardware-level attacks require sophisticated countermeasures that are still under development.

The present landscape of logic chip network applications spans multiple domains including telecommunications infrastructure, enterprise networking, and cloud computing environments. Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs) dominate the market, with major deployments in 5G base stations, high-frequency trading networks, and hyperscale data centers. These implementations demonstrate varying degrees of intelligence, from basic rule-based processing to machine learning-enabled traffic optimization.

Despite significant progress, several critical challenges impede the full realization of intelligent network solutions using logic chips. Power consumption remains a primary constraint, particularly in edge computing scenarios where thermal management and energy efficiency are paramount. The complexity of programming and configuring logic chips for network applications creates substantial barriers for widespread adoption, requiring specialized expertise that is often scarce in the industry.

Latency optimization presents another significant challenge, especially in real-time applications such as autonomous vehicle networks and industrial IoT systems. While logic chips offer superior processing capabilities compared to traditional software-based solutions, achieving consistent sub-microsecond response times across diverse network conditions remains problematic. Additionally, the integration of artificial intelligence algorithms directly onto logic chips faces limitations in memory bandwidth and computational parallelism.

Scalability issues emerge when deploying logic chip-based solutions across heterogeneous network environments. The lack of standardized interfaces and programming models creates fragmentation, making it difficult to achieve seamless interoperability between different vendors' solutions. Security vulnerabilities also pose growing concerns, as the increased complexity of logic chip firmware and the potential for hardware-level attacks require sophisticated countermeasures that are still under development.

Existing Logic Chip-Based Intelligent Network Architectures

01 Logic chip architecture and design structures

Logic chips can be designed with specific architectural structures to optimize performance and functionality. These designs may include novel circuit configurations, gate arrangements, and interconnection schemes that enhance processing capabilities. The architecture can incorporate various logic elements and their spatial arrangements to achieve desired computational operations while maintaining efficiency and reducing power consumption.- Logic chip architecture and design structures: Logic chips can be designed with specific architectural structures to optimize performance and functionality. These designs may include novel circuit configurations, interconnection schemes, and layout methodologies that enhance processing capabilities. The architecture can incorporate various logic gates, flip-flops, and other fundamental building blocks arranged in efficient patterns to achieve desired computational operations.

- Manufacturing processes and fabrication methods for logic chips: Various manufacturing techniques can be employed to fabricate logic chips with improved characteristics. These processes may involve advanced lithography methods, etching techniques, deposition processes, and doping procedures. The fabrication methods can include steps for forming transistors, creating interconnect layers, and implementing isolation structures to ensure proper chip functionality and reliability.

- Integration of logic chips with memory components: Logic chips can be integrated with various memory elements to create comprehensive computing systems. This integration may involve combining processing logic with different types of memory such as cache, registers, or embedded memory arrays. The integration approaches can enhance data access speeds, reduce latency, and improve overall system performance by minimizing the distance between logic and storage elements.

- Power management and optimization in logic chips: Logic chips can incorporate power management features to reduce energy consumption and improve efficiency. These features may include voltage scaling techniques, clock gating mechanisms, power domain partitioning, and dynamic power control circuits. The optimization strategies can help extend battery life in portable devices and reduce heat generation in high-performance computing applications.

- Testing and verification methodologies for logic chips: Various testing and verification approaches can be implemented to ensure logic chip functionality and reliability. These methodologies may include built-in self-test circuits, scan chain designs, fault detection mechanisms, and diagnostic features. The testing strategies can identify manufacturing defects, verify correct operation, and enable field diagnostics to maintain chip quality throughout its lifecycle.

02 Manufacturing processes and fabrication methods for logic chips

Various manufacturing techniques and fabrication processes can be employed to produce logic chips with improved characteristics. These methods may involve specific material deposition techniques, etching processes, lithography approaches, and layer formation strategies. The fabrication processes can be optimized to achieve better yield, reduced defects, and enhanced electrical properties of the resulting logic circuits.Expand Specific Solutions03 Integration and packaging of logic chips

Logic chips can be integrated into larger systems through various packaging and assembly techniques. These approaches include methods for connecting multiple chips, creating multi-chip modules, and establishing electrical connections between logic circuits and external components. The integration strategies focus on optimizing signal integrity, thermal management, and overall system performance while minimizing footprint and cost.Expand Specific Solutions04 Testing and verification methods for logic chips

Various testing methodologies and verification techniques can be applied to ensure the proper functionality and reliability of logic chips. These methods may include built-in self-test mechanisms, scan chain implementations, fault detection circuits, and diagnostic procedures. The testing approaches enable identification of manufacturing defects, functional errors, and performance issues during production and operation.Expand Specific Solutions05 Power management and optimization in logic chips

Logic chips can incorporate power management features and optimization techniques to reduce energy consumption and improve efficiency. These implementations may include voltage regulation circuits, clock gating mechanisms, power domain isolation, and dynamic power scaling capabilities. The power management strategies help extend battery life in portable devices and reduce overall system power requirements while maintaining performance levels.Expand Specific Solutions

Key Players in Logic Chip and Network Solution Industry

The intelligent network solutions leveraging logic chips market is experiencing rapid evolution driven by increasing demand for AI-enabled networking infrastructure. The industry is in a growth phase with substantial market expansion fueled by 5G deployment, edge computing, and IoT proliferation. Technology maturity varies significantly across market segments, with established players like Intel, NVIDIA, and Huawei leading in advanced chip architectures and AI acceleration capabilities. Traditional networking giants including VMware, Siemens, and IBM are integrating logic chip innovations into comprehensive network solutions. Emerging specialists such as Graphcore and Pensando Systems are pushing technological boundaries with specialized processors. Asian manufacturers like TSMC, ZTE, and Ruijie Networks are strengthening their positions through manufacturing excellence and regional market penetration, while research institutions contribute foundational innovations, creating a competitive landscape characterized by both technological convergence and specialization.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei implements intelligent network solutions through their Kunpeng processors and Ascend AI chips, creating a comprehensive logic chip ecosystem for network intelligence. Their approach integrates ARM-based processing units with specialized network processing engines and AI accelerators on a single platform. The solution supports intelligent traffic management, automated network slicing for 5G applications, and real-time network optimization through machine learning algorithms. Huawei's logic chips feature dedicated security processing units and support for network function virtualization, enabling dynamic service deployment and intelligent resource allocation across network infrastructure.

Strengths: Integrated 5G and networking expertise, cost-effective solutions, strong presence in telecom infrastructure. Weaknesses: Limited global market access due to regulatory restrictions, reduced third-party software ecosystem support.

Intel Corp.

Technical Solution: Intel leverages its advanced logic chip architectures including Xeon processors and FPGA solutions to enable intelligent network infrastructure. Their approach integrates hardware acceleration with software-defined networking capabilities, utilizing specialized logic circuits for packet processing, traffic analysis, and network optimization. Intel's Smart Edge platform combines CPU, GPU, and FPGA resources to deliver real-time network intelligence, enabling dynamic bandwidth allocation, predictive maintenance, and automated network configuration. The company's logic chips feature built-in AI acceleration units that can process network telemetry data in real-time, supporting machine learning algorithms for network anomaly detection and performance optimization.

Strengths: Market-leading processor performance, extensive ecosystem support, proven enterprise reliability. Weaknesses: Higher power consumption compared to specialized chips, complex integration requirements.

Core Innovations in Logic Chip Network Intelligence Patents

Method of using electronically reconfigurable gate array logic and apparatus formed thereby

PatentInactiveCA2025096C

Innovation

- A system comprising a plurality of reprogrammable logic devices and interconnect devices, connected via fixed electrical conductors, allowing for the configuration of functional elements and interconnections to realize large digital networks, utilizing a partial crossbar interconnect architecture for efficient signal passing between logic chips.

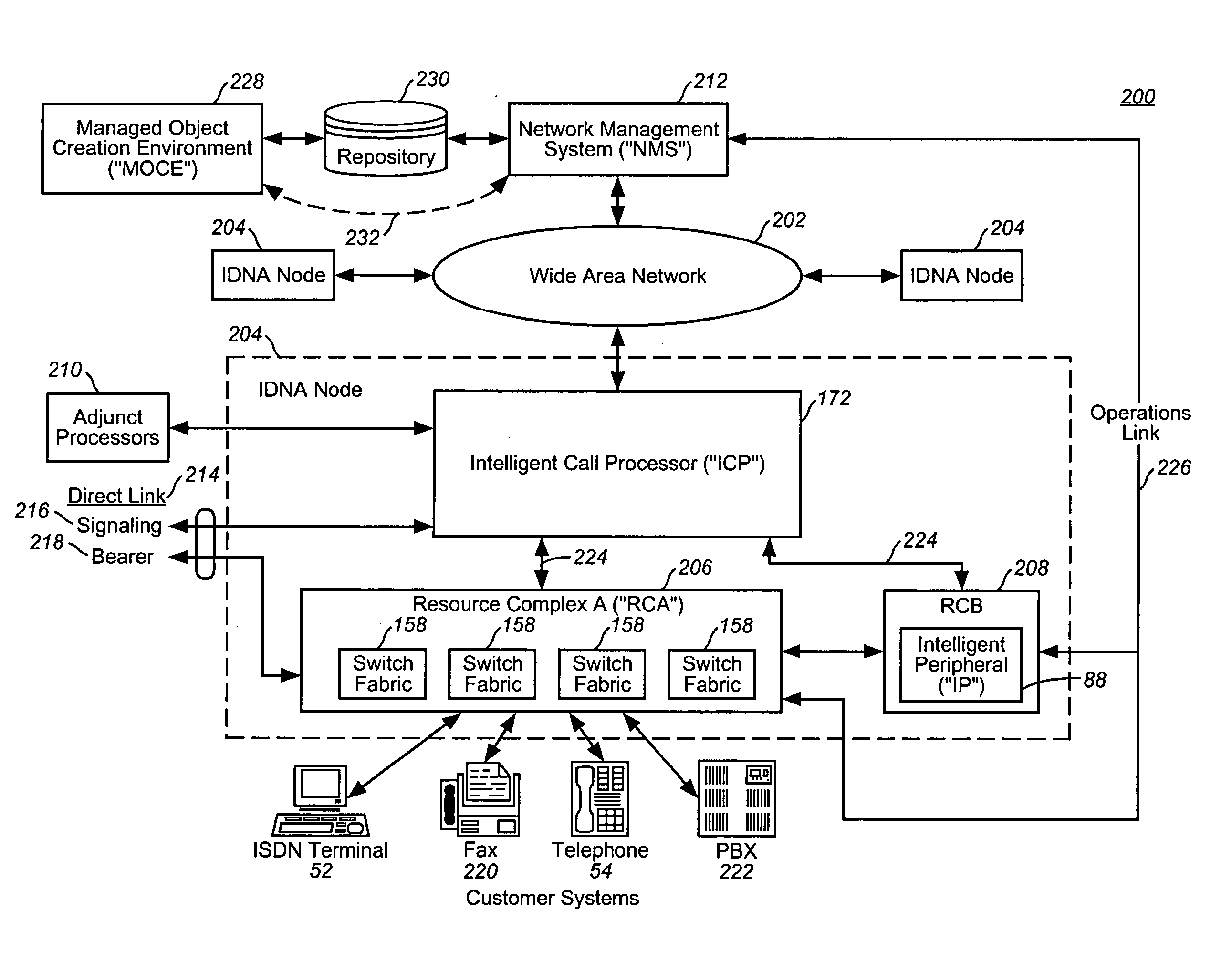

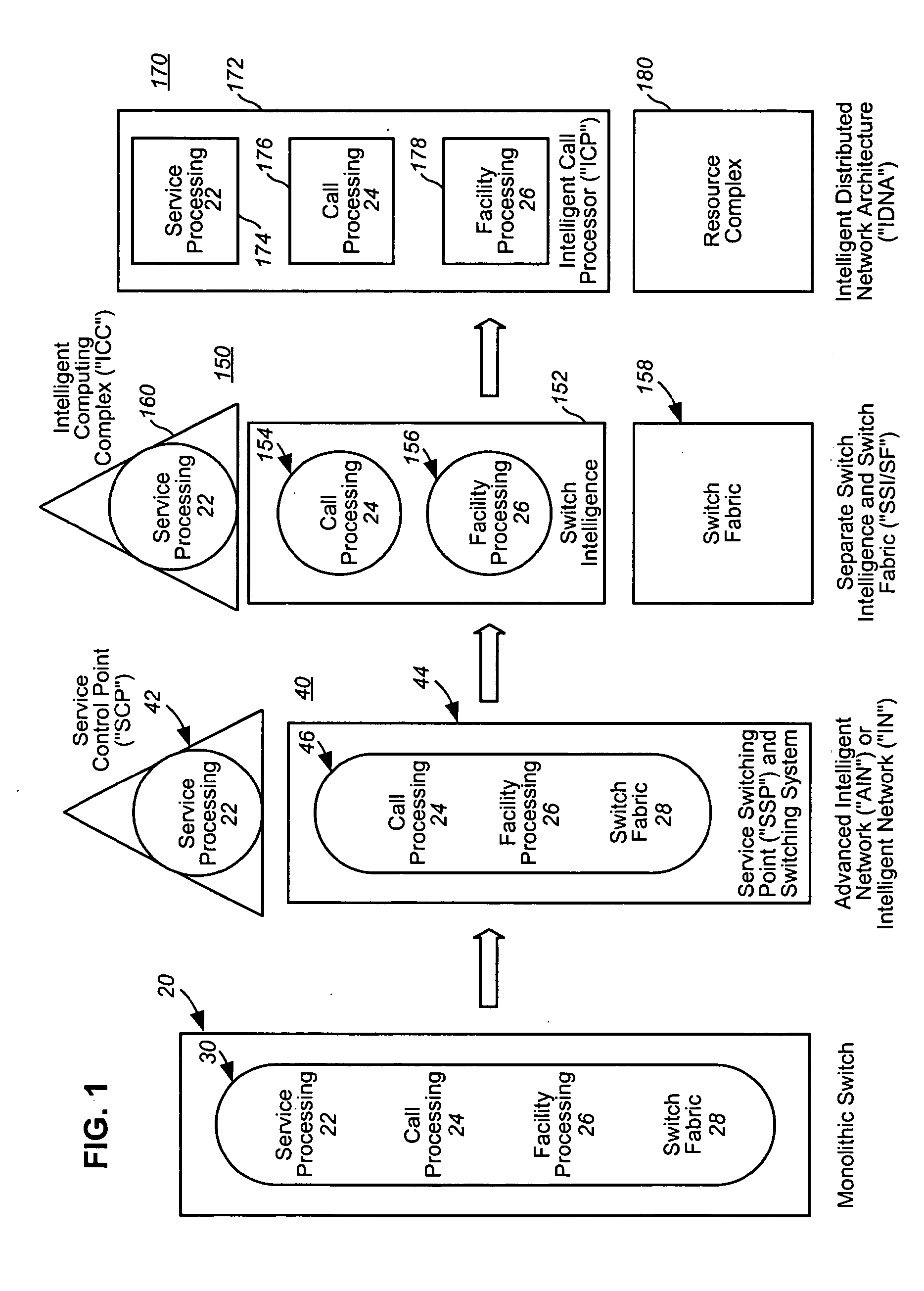

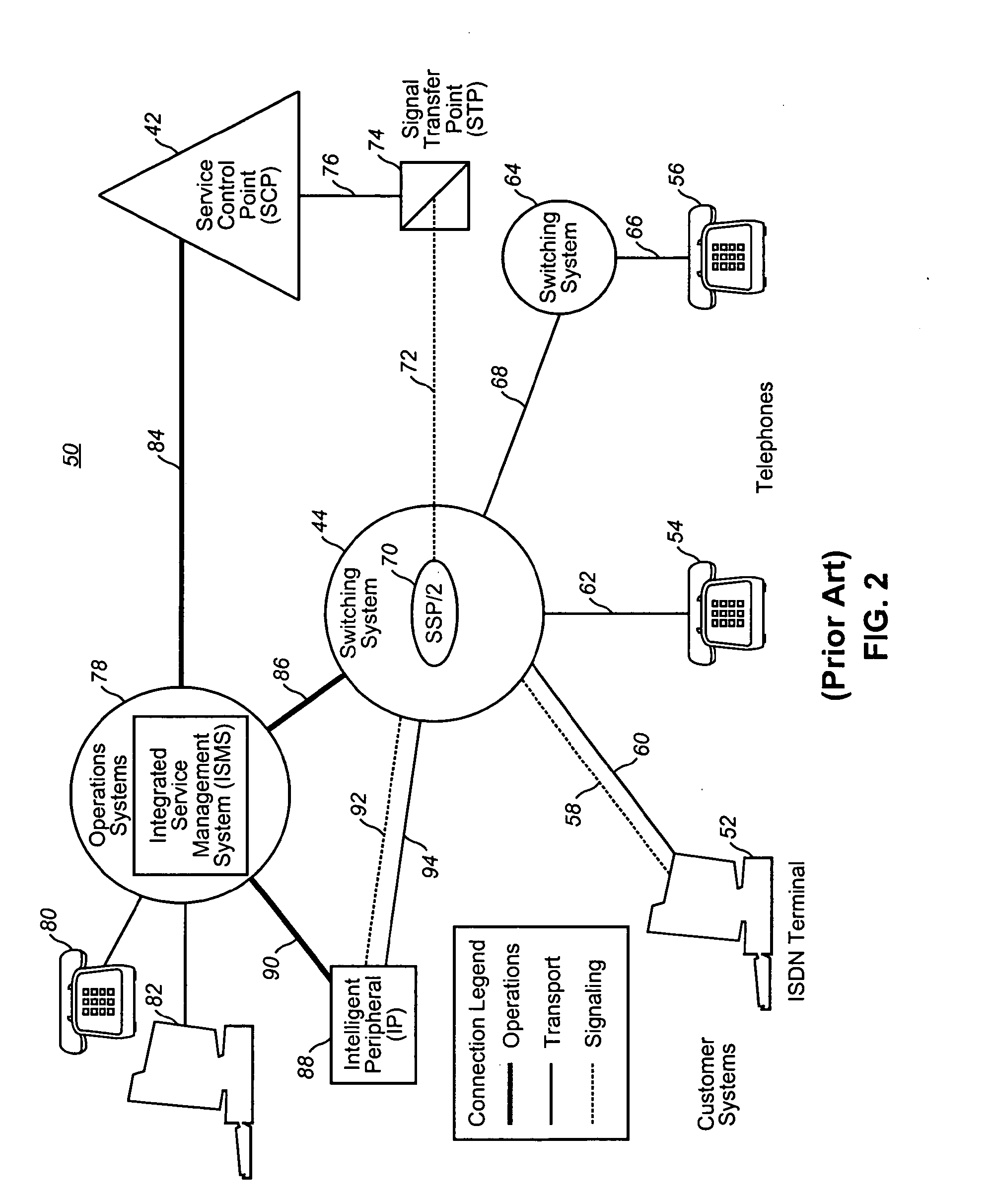

Intelligent network

PatentInactiveUS20050021713A1

Innovation

- The introduction of an intelligent network architecture with distributed service nodes that provide a platform-independent execution environment for call processing, allowing modular software processes to run on various platforms and eliminating the need for specialized service nodes, along with a centralized service administration system for managing and distributing service modules.

Standards and Protocols for Logic Chip Network Integration

The integration of logic chips into intelligent network solutions requires adherence to established standards and protocols that ensure seamless interoperability, reliable performance, and scalable deployment. Current standardization efforts focus on creating unified frameworks that bridge the gap between traditional networking protocols and emerging logic chip architectures.

IEEE 802.11 and Ethernet standards have been extended to accommodate logic chip integration through specialized adaptation layers. These adaptations include modified frame structures that can carry logic processing instructions alongside conventional data packets. The Open Network Computing Research Center has proposed amendments to existing protocols that enable dynamic logic allocation and real-time processing coordination across distributed network nodes.

Software-defined networking protocols, particularly OpenFlow and P4, have emerged as critical enablers for logic chip network integration. P4 programming language allows network operators to define custom packet processing behaviors directly on logic chips, while OpenFlow provides the control plane mechanisms necessary for centralized management of distributed logic resources. These protocols support fine-grained control over packet forwarding decisions and enable dynamic reconfiguration of logic chip functionalities.

Network Function Virtualization standards, including ETSI NFV specifications, have been adapted to support logic chip-based implementations. The NFV Management and Orchestration framework now incorporates logic chip resource abstraction layers that treat processing units as virtualized network functions. This approach enables seamless migration of network services between traditional software implementations and hardware-accelerated logic chip solutions.

Emerging protocols specifically designed for logic chip networks include the Logic Processing Protocol, which defines standardized interfaces for inter-chip communication and coordination. This protocol establishes common messaging formats for distributing computational tasks across multiple logic chips and synchronizing processing results. Additionally, the Network Logic Abstraction Layer provides standardized APIs that allow network applications to leverage logic chip capabilities without requiring detailed hardware knowledge.

Quality of Service protocols have been enhanced to account for the unique characteristics of logic chip processing, including deterministic latency guarantees and priority-based resource allocation mechanisms that ensure critical network functions receive adequate processing resources.

IEEE 802.11 and Ethernet standards have been extended to accommodate logic chip integration through specialized adaptation layers. These adaptations include modified frame structures that can carry logic processing instructions alongside conventional data packets. The Open Network Computing Research Center has proposed amendments to existing protocols that enable dynamic logic allocation and real-time processing coordination across distributed network nodes.

Software-defined networking protocols, particularly OpenFlow and P4, have emerged as critical enablers for logic chip network integration. P4 programming language allows network operators to define custom packet processing behaviors directly on logic chips, while OpenFlow provides the control plane mechanisms necessary for centralized management of distributed logic resources. These protocols support fine-grained control over packet forwarding decisions and enable dynamic reconfiguration of logic chip functionalities.

Network Function Virtualization standards, including ETSI NFV specifications, have been adapted to support logic chip-based implementations. The NFV Management and Orchestration framework now incorporates logic chip resource abstraction layers that treat processing units as virtualized network functions. This approach enables seamless migration of network services between traditional software implementations and hardware-accelerated logic chip solutions.

Emerging protocols specifically designed for logic chip networks include the Logic Processing Protocol, which defines standardized interfaces for inter-chip communication and coordination. This protocol establishes common messaging formats for distributing computational tasks across multiple logic chips and synchronizing processing results. Additionally, the Network Logic Abstraction Layer provides standardized APIs that allow network applications to leverage logic chip capabilities without requiring detailed hardware knowledge.

Quality of Service protocols have been enhanced to account for the unique characteristics of logic chip processing, including deterministic latency guarantees and priority-based resource allocation mechanisms that ensure critical network functions receive adequate processing resources.

Security Considerations in Logic Chip Network Deployments

Security considerations in logic chip network deployments represent a critical dimension that fundamentally shapes the viability and trustworthiness of intelligent network solutions. As logic chips become increasingly integrated into network infrastructure, they introduce both unprecedented capabilities and novel attack vectors that require comprehensive security frameworks.

The distributed nature of logic chip deployments creates multiple potential entry points for malicious actors. Unlike traditional centralized network architectures, intelligent networks leveraging logic chips distribute processing capabilities across numerous nodes, each representing a potential vulnerability. These chips often operate with elevated privileges to perform real-time network optimization, making them attractive targets for adversaries seeking to compromise network integrity or extract sensitive information.

Hardware-level security emerges as a fundamental concern, as logic chips must be protected against physical tampering, side-channel attacks, and supply chain vulnerabilities. The manufacturing process itself introduces risks, particularly when chips are produced across multiple facilities or involve third-party components. Ensuring the authenticity and integrity of logic chips throughout their lifecycle requires robust verification mechanisms and secure boot processes.

Firmware and software security layers present additional challenges, as logic chips typically run specialized operating systems or embedded software that may lack traditional security hardening. Regular security updates become complex when chips are deployed across geographically distributed network infrastructure, necessitating secure remote update mechanisms that do not compromise network availability.

Data protection and privacy considerations are paramount, as logic chips process and potentially store sensitive network traffic data. Encryption of data both at rest and in transit becomes essential, along with secure key management systems that can operate efficiently within the resource constraints of embedded logic chip environments.

Network segmentation and access control mechanisms must be redesigned to accommodate the unique characteristics of logic chip deployments. Traditional perimeter-based security models prove insufficient when intelligent processing occurs at multiple network layers simultaneously. Zero-trust architectures become increasingly relevant, requiring continuous authentication and authorization of logic chip communications.

Monitoring and incident response capabilities require enhancement to detect anomalous behavior in logic chip networks. The autonomous nature of these systems demands sophisticated behavioral analysis tools that can distinguish between legitimate adaptive responses and potential security breaches, ensuring rapid detection and mitigation of threats while maintaining network performance.

The distributed nature of logic chip deployments creates multiple potential entry points for malicious actors. Unlike traditional centralized network architectures, intelligent networks leveraging logic chips distribute processing capabilities across numerous nodes, each representing a potential vulnerability. These chips often operate with elevated privileges to perform real-time network optimization, making them attractive targets for adversaries seeking to compromise network integrity or extract sensitive information.

Hardware-level security emerges as a fundamental concern, as logic chips must be protected against physical tampering, side-channel attacks, and supply chain vulnerabilities. The manufacturing process itself introduces risks, particularly when chips are produced across multiple facilities or involve third-party components. Ensuring the authenticity and integrity of logic chips throughout their lifecycle requires robust verification mechanisms and secure boot processes.

Firmware and software security layers present additional challenges, as logic chips typically run specialized operating systems or embedded software that may lack traditional security hardening. Regular security updates become complex when chips are deployed across geographically distributed network infrastructure, necessitating secure remote update mechanisms that do not compromise network availability.

Data protection and privacy considerations are paramount, as logic chips process and potentially store sensitive network traffic data. Encryption of data both at rest and in transit becomes essential, along with secure key management systems that can operate efficiently within the resource constraints of embedded logic chip environments.

Network segmentation and access control mechanisms must be redesigned to accommodate the unique characteristics of logic chip deployments. Traditional perimeter-based security models prove insufficient when intelligent processing occurs at multiple network layers simultaneously. Zero-trust architectures become increasingly relevant, requiring continuous authentication and authorization of logic chip communications.

Monitoring and incident response capabilities require enhancement to detect anomalous behavior in logic chip networks. The autonomous nature of these systems demands sophisticated behavioral analysis tools that can distinguish between legitimate adaptive responses and potential security breaches, ensuring rapid detection and mitigation of threats while maintaining network performance.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!