Logic Chips vs FPGA Fabrics: Reconfiguration Efficiency Analysis

APR 2, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Logic Chips vs FPGA Reconfiguration Background and Objectives

The evolution of digital computing architectures has been fundamentally shaped by the trade-off between performance optimization and flexibility requirements. Traditional logic chips, including Application-Specific Integrated Circuits (ASICs) and standard processors, have dominated computing landscapes through their optimized performance for specific computational tasks. However, the increasing demand for adaptable computing solutions has elevated Field-Programmable Gate Arrays (FPGAs) as a compelling alternative architecture.

Logic chips represent the conventional approach to digital circuit design, where functionality is permanently embedded during the manufacturing process. These circuits achieve maximum performance efficiency through dedicated silicon real estate allocation and optimized signal pathways. The architectural rigidity that enables superior performance simultaneously creates limitations in post-deployment adaptability, requiring complete hardware replacement for functional modifications.

FPGA fabrics emerged as a revolutionary paradigm shift, introducing reconfigurable logic blocks interconnected through programmable routing matrices. This architecture enables dynamic functionality modification through configuration bitstream updates, fundamentally altering the relationship between hardware capabilities and software-defined behavior. The reconfiguration capability transforms FPGAs from static computing elements into adaptive processing platforms.

The reconfiguration efficiency analysis becomes critical as modern applications increasingly demand both high performance and operational flexibility. Edge computing, artificial intelligence acceleration, and software-defined networking represent domains where reconfiguration capabilities directly impact system effectiveness. The ability to modify hardware functionality without physical replacement offers significant advantages in deployment cost, maintenance overhead, and feature evolution.

Contemporary technological trends emphasize the importance of understanding reconfiguration trade-offs. The proliferation of heterogeneous computing environments requires careful evaluation of when fixed-function logic chips provide optimal solutions versus scenarios where FPGA reconfigurability justifies potential performance compromises. This analysis extends beyond simple performance metrics to encompass power consumption, development complexity, and long-term adaptability requirements.

The primary objective centers on establishing comprehensive evaluation frameworks for comparing reconfiguration efficiency between logic chips and FPGA fabrics. This involves quantifying reconfiguration overhead, analyzing performance implications of programmable architectures, and identifying optimal application domains for each approach. Understanding these efficiency characteristics enables informed architectural decisions that balance immediate performance requirements with future adaptability needs, ultimately guiding strategic technology adoption in evolving computing landscapes.

Logic chips represent the conventional approach to digital circuit design, where functionality is permanently embedded during the manufacturing process. These circuits achieve maximum performance efficiency through dedicated silicon real estate allocation and optimized signal pathways. The architectural rigidity that enables superior performance simultaneously creates limitations in post-deployment adaptability, requiring complete hardware replacement for functional modifications.

FPGA fabrics emerged as a revolutionary paradigm shift, introducing reconfigurable logic blocks interconnected through programmable routing matrices. This architecture enables dynamic functionality modification through configuration bitstream updates, fundamentally altering the relationship between hardware capabilities and software-defined behavior. The reconfiguration capability transforms FPGAs from static computing elements into adaptive processing platforms.

The reconfiguration efficiency analysis becomes critical as modern applications increasingly demand both high performance and operational flexibility. Edge computing, artificial intelligence acceleration, and software-defined networking represent domains where reconfiguration capabilities directly impact system effectiveness. The ability to modify hardware functionality without physical replacement offers significant advantages in deployment cost, maintenance overhead, and feature evolution.

Contemporary technological trends emphasize the importance of understanding reconfiguration trade-offs. The proliferation of heterogeneous computing environments requires careful evaluation of when fixed-function logic chips provide optimal solutions versus scenarios where FPGA reconfigurability justifies potential performance compromises. This analysis extends beyond simple performance metrics to encompass power consumption, development complexity, and long-term adaptability requirements.

The primary objective centers on establishing comprehensive evaluation frameworks for comparing reconfiguration efficiency between logic chips and FPGA fabrics. This involves quantifying reconfiguration overhead, analyzing performance implications of programmable architectures, and identifying optimal application domains for each approach. Understanding these efficiency characteristics enables informed architectural decisions that balance immediate performance requirements with future adaptability needs, ultimately guiding strategic technology adoption in evolving computing landscapes.

Market Demand for Reconfigurable Computing Solutions

The global reconfigurable computing market is experiencing unprecedented growth driven by the increasing demand for flexible, high-performance computing solutions across diverse industries. Traditional fixed-function processors are proving inadequate for emerging applications that require adaptive computational capabilities, creating substantial market opportunities for both logic chips and FPGA fabrics.

Data centers represent the largest market segment for reconfigurable computing solutions, where operators seek to optimize performance per watt while maintaining flexibility for evolving workloads. Cloud service providers are increasingly adopting FPGA-based acceleration to handle diverse computational tasks ranging from machine learning inference to network packet processing. The ability to reconfigure hardware resources dynamically allows these providers to maximize resource utilization and reduce operational costs.

The telecommunications sector demonstrates strong demand for reconfigurable solutions, particularly with the deployment of 5G networks and edge computing infrastructure. Network equipment manufacturers require platforms capable of adapting to evolving communication standards and protocols without hardware replacement. This flexibility is crucial for managing the diverse requirements of network slicing and real-time processing in modern telecommunications systems.

Automotive and aerospace industries are driving demand for reconfigurable computing in safety-critical applications. Advanced driver assistance systems and autonomous vehicle platforms require computational flexibility to adapt to changing environmental conditions and regulatory requirements. Similarly, aerospace applications benefit from the ability to update and modify system functionality through software rather than hardware changes.

The artificial intelligence and machine learning market segment shows particularly strong growth potential for reconfigurable computing solutions. As AI algorithms continue to evolve rapidly, organizations need hardware platforms that can adapt to new neural network architectures and computational patterns without requiring complete system redesigns.

Industrial automation and Internet of Things applications create additional market demand for reconfigurable solutions. Manufacturing systems require flexible computing platforms that can adapt to changing production requirements and integrate new sensors or control algorithms without extensive hardware modifications.

Market growth is further accelerated by the increasing complexity of modern applications that require heterogeneous computing approaches, combining different processing paradigms within single systems to achieve optimal performance and efficiency.

Data centers represent the largest market segment for reconfigurable computing solutions, where operators seek to optimize performance per watt while maintaining flexibility for evolving workloads. Cloud service providers are increasingly adopting FPGA-based acceleration to handle diverse computational tasks ranging from machine learning inference to network packet processing. The ability to reconfigure hardware resources dynamically allows these providers to maximize resource utilization and reduce operational costs.

The telecommunications sector demonstrates strong demand for reconfigurable solutions, particularly with the deployment of 5G networks and edge computing infrastructure. Network equipment manufacturers require platforms capable of adapting to evolving communication standards and protocols without hardware replacement. This flexibility is crucial for managing the diverse requirements of network slicing and real-time processing in modern telecommunications systems.

Automotive and aerospace industries are driving demand for reconfigurable computing in safety-critical applications. Advanced driver assistance systems and autonomous vehicle platforms require computational flexibility to adapt to changing environmental conditions and regulatory requirements. Similarly, aerospace applications benefit from the ability to update and modify system functionality through software rather than hardware changes.

The artificial intelligence and machine learning market segment shows particularly strong growth potential for reconfigurable computing solutions. As AI algorithms continue to evolve rapidly, organizations need hardware platforms that can adapt to new neural network architectures and computational patterns without requiring complete system redesigns.

Industrial automation and Internet of Things applications create additional market demand for reconfigurable solutions. Manufacturing systems require flexible computing platforms that can adapt to changing production requirements and integrate new sensors or control algorithms without extensive hardware modifications.

Market growth is further accelerated by the increasing complexity of modern applications that require heterogeneous computing approaches, combining different processing paradigms within single systems to achieve optimal performance and efficiency.

Current State and Challenges in FPGA Reconfiguration Efficiency

FPGA reconfiguration efficiency currently faces significant limitations that constrain its competitive advantage over traditional logic chips. Modern FPGA architectures achieve reconfiguration times ranging from milliseconds to seconds, depending on the configuration size and method employed. Partial reconfiguration capabilities have improved substantially, with leading vendors like Xilinx and Intel achieving sub-millisecond reconfiguration for small logic blocks. However, full device reconfiguration still requires considerable time overhead, typically 100-500 milliseconds for mid-range devices.

The primary technical challenge lies in the configuration memory architecture and data transfer mechanisms. Current FPGAs utilize SRAM-based configuration cells that require complete reloading of bitstream data through relatively narrow configuration interfaces. This creates a fundamental bottleneck where configuration bandwidth becomes the limiting factor. Advanced devices implement multiple configuration ports and enhanced Direct Memory Access controllers, yet the sequential nature of bitstream loading remains problematic.

Power consumption during reconfiguration presents another critical constraint. Dynamic reconfiguration events can consume 2-5 times the normal operating power, creating thermal management challenges and limiting battery-powered applications. The power surge occurs due to simultaneous switching of numerous configuration cells and associated routing resources, compounded by the need to maintain state information during partial reconfigurations.

Configuration memory overhead significantly impacts resource utilization efficiency. SRAM-based configuration requires approximately 20-30 times more silicon area compared to the actual logic resources being configured. This overhead directly affects cost-effectiveness when compared to dedicated logic chips, particularly for applications requiring frequent reconfiguration cycles.

Verification and validation of reconfigured designs pose substantial challenges in dynamic environments. Unlike static logic chips with predictable timing characteristics, FPGA reconfiguration introduces timing uncertainties and potential glitches during transition periods. Current design tools lack comprehensive support for analyzing multi-configuration scenarios, making it difficult to guarantee system reliability across all possible reconfiguration states.

Emerging non-volatile configuration technologies, including Flash-based and resistive memory approaches, show promise for addressing some limitations. However, these technologies currently suffer from limited write endurance and slower programming speeds compared to SRAM-based solutions, creating new trade-offs between reconfiguration frequency and long-term reliability.

The primary technical challenge lies in the configuration memory architecture and data transfer mechanisms. Current FPGAs utilize SRAM-based configuration cells that require complete reloading of bitstream data through relatively narrow configuration interfaces. This creates a fundamental bottleneck where configuration bandwidth becomes the limiting factor. Advanced devices implement multiple configuration ports and enhanced Direct Memory Access controllers, yet the sequential nature of bitstream loading remains problematic.

Power consumption during reconfiguration presents another critical constraint. Dynamic reconfiguration events can consume 2-5 times the normal operating power, creating thermal management challenges and limiting battery-powered applications. The power surge occurs due to simultaneous switching of numerous configuration cells and associated routing resources, compounded by the need to maintain state information during partial reconfigurations.

Configuration memory overhead significantly impacts resource utilization efficiency. SRAM-based configuration requires approximately 20-30 times more silicon area compared to the actual logic resources being configured. This overhead directly affects cost-effectiveness when compared to dedicated logic chips, particularly for applications requiring frequent reconfiguration cycles.

Verification and validation of reconfigured designs pose substantial challenges in dynamic environments. Unlike static logic chips with predictable timing characteristics, FPGA reconfiguration introduces timing uncertainties and potential glitches during transition periods. Current design tools lack comprehensive support for analyzing multi-configuration scenarios, making it difficult to guarantee system reliability across all possible reconfiguration states.

Emerging non-volatile configuration technologies, including Flash-based and resistive memory approaches, show promise for addressing some limitations. However, these technologies currently suffer from limited write endurance and slower programming speeds compared to SRAM-based solutions, creating new trade-offs between reconfiguration frequency and long-term reliability.

Existing Reconfiguration Efficiency Solutions

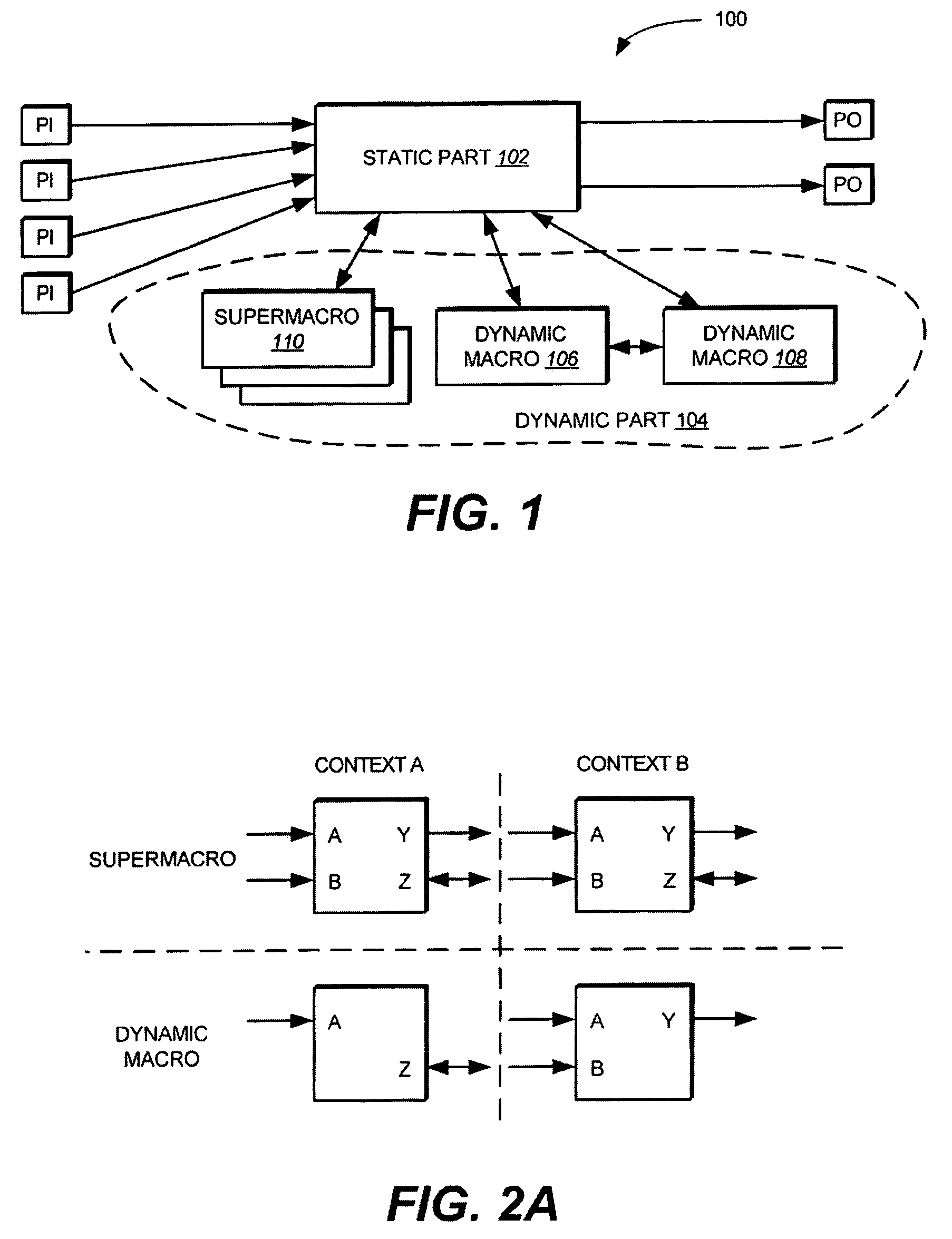

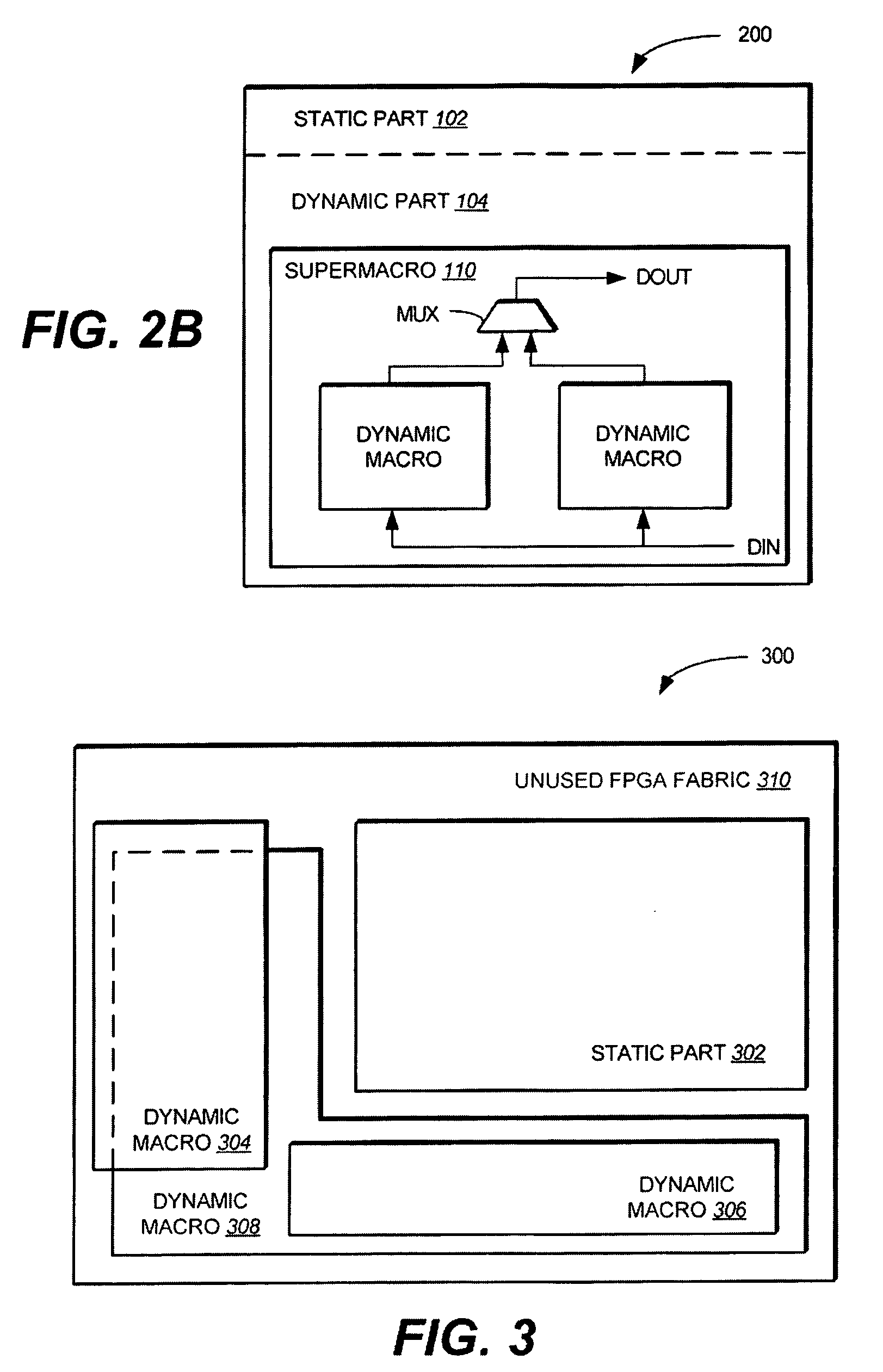

01 Dynamic partial reconfiguration techniques for FPGA fabrics

Dynamic partial reconfiguration allows portions of an FPGA to be reconfigured while other portions continue operating, significantly improving reconfiguration efficiency. This technique enables runtime adaptation of logic resources without complete system shutdown. Methods include bitstream management, configuration memory partitioning, and selective logic block updates to minimize reconfiguration time and maintain system functionality during the reconfiguration process.- Partial reconfiguration techniques for FPGA fabrics: Partial reconfiguration allows specific regions of an FPGA to be reconfigured while other portions continue operating, significantly improving reconfiguration efficiency. This technique enables dynamic modification of logic functions without complete system shutdown, reducing reconfiguration time and power consumption. Advanced methods include frame-based reconfiguration and module-based partial reconfiguration that optimize the granularity of reconfigurable regions.

- Configuration memory architecture optimization: Efficient configuration memory structures are critical for fast FPGA reconfiguration. Innovations include hierarchical memory organizations, compressed bitstream storage, and parallel configuration data paths. These architectures reduce the amount of data that needs to be transferred during reconfiguration and enable faster access to configuration information, thereby improving overall reconfiguration speed and reducing latency.

- Hardware acceleration for configuration processing: Dedicated hardware accelerators can significantly enhance FPGA reconfiguration efficiency by processing configuration data in parallel and performing on-the-fly decompression or decryption. These accelerators include specialized configuration controllers, DMA engines, and preprocessing units that handle bitstream manipulation tasks, reducing the burden on general-purpose processors and minimizing reconfiguration overhead.

- Dynamic reconfiguration scheduling and management: Intelligent scheduling algorithms and management systems optimize when and how reconfiguration occurs in FPGA fabrics. These systems analyze application requirements, predict reconfiguration needs, and coordinate multiple reconfiguration requests to minimize performance impact. Advanced techniques include priority-based scheduling, resource allocation optimization, and context switching mechanisms that enable seamless transitions between different configurations.

- Reconfiguration interface and protocol enhancements: Improved interfaces and communication protocols between configuration controllers and FPGA fabrics enhance reconfiguration efficiency. These enhancements include high-speed serial configuration interfaces, parallel configuration buses with increased bandwidth, and optimized protocol stacks that reduce handshaking overhead. Advanced error detection and correction mechanisms ensure reliable configuration data transfer while maintaining high throughput.

02 Fast configuration memory access and bitstream compression

Efficient configuration memory architectures and compressed bitstream formats reduce the time required to load configuration data into FPGA fabrics. Techniques include optimized memory interfaces, parallel configuration paths, and bitstream compression algorithms that decrease data transfer requirements. These methods enable faster reconfiguration cycles by reducing the amount of data that must be transferred and the time needed to write configuration information to memory cells.Expand Specific Solutions03 Hierarchical and modular reconfiguration architectures

Hierarchical reconfiguration structures organize FPGA resources into modules or regions that can be independently reconfigured, improving overall efficiency. This approach allows for granular control over which portions of the fabric are modified, reducing unnecessary reconfiguration overhead. Modular architectures support parallel reconfiguration operations and enable better resource utilization by isolating changes to specific functional blocks while preserving the state of unaffected regions.Expand Specific Solutions04 Configuration caching and prefetching mechanisms

Configuration caching stores frequently used bitstreams or configuration patterns in fast-access memory, while prefetching anticipates future reconfiguration needs to reduce latency. These techniques minimize the delay associated with retrieving configuration data from external storage. By maintaining commonly used configurations in local cache and predicting reconfiguration sequences, systems can achieve near-instantaneous switching between different logic configurations and improve overall throughput.Expand Specific Solutions05 Hardware-accelerated reconfiguration controllers and interfaces

Dedicated hardware controllers and optimized interfaces manage the reconfiguration process with minimal processor intervention, enhancing efficiency. These specialized circuits handle bitstream parsing, configuration sequencing, and error checking at hardware speeds. Advanced interfaces support high-bandwidth data transfer and parallel configuration operations, while intelligent controllers can optimize reconfiguration scheduling and resource allocation to minimize system disruption and maximize reconfiguration throughput.Expand Specific Solutions

Key Players in Logic Chip and FPGA Industry

The logic chips versus FPGA fabrics reconfiguration efficiency landscape represents a mature yet rapidly evolving market driven by diverse application demands across computing, telecommunications, and AI acceleration. The industry has reached a consolidation phase, with established players like Intel (through Altera acquisition), Xilinx (now AMD), and NVIDIA dominating traditional segments, while emerging companies such as SambaNova Systems and Achronix Semiconductor push boundaries in specialized reconfigurable architectures. Market size continues expanding, particularly in AI inference and edge computing applications. Technology maturity varies significantly - conventional FPGA architectures from Xilinx and Altera represent mature solutions, while next-generation reconfigurable dataflow units from SambaNova and adaptive computing platforms from companies like Corerain Technologies indicate ongoing innovation in reconfiguration efficiency optimization for specific workloads.

Altera Corp.

Technical Solution: Altera (now part of Intel) has pioneered hierarchical reconfiguration techniques in their Stratix and Arria FPGA families, implementing multi-level configuration management that optimizes reconfiguration time based on the scope of changes required. Their Quartus Prime software provides detailed analysis of reconfiguration efficiency, including metrics for partial reconfiguration region sizing and interconnect overhead assessment. The company's recent focus on heterogeneous computing platforms combines traditional FPGA fabric with hardened processor cores and dedicated accelerator blocks, enabling selective reconfiguration strategies that minimize system disruption while maximizing computational flexibility and resource utilization efficiency.

Strengths: Strong integration with Intel ecosystem and advanced partial reconfiguration capabilities with comprehensive design tools. Weaknesses: Vendor lock-in concerns and potentially higher licensing costs for advanced features.

NVIDIA Corp.

Technical Solution: NVIDIA approaches reconfiguration efficiency through their GPU architecture combined with CUDA programming model, offering software-based reconfiguration that avoids hardware reconfiguration overhead entirely. Their Jetson platform integrates GPU cores with ARM processors, enabling dynamic workload allocation between fixed-function units and programmable cores. The company's recent developments in AI accelerators focus on dataflow architectures that provide FPGA-like flexibility while maintaining the performance characteristics of dedicated logic chips. NVIDIA's approach emphasizes compile-time optimization and runtime scheduling to achieve reconfiguration-like adaptability without traditional FPGA reconfiguration penalties.

Strengths: Superior performance for parallel computing workloads and mature software ecosystem with extensive developer support. Weaknesses: Limited fine-grained reconfigurability compared to FPGAs and higher cost for low-volume applications.

Core Innovations in FPGA Reconfiguration Architectures

Technologies for rapid configuration of field-programmable gate arrays

PatentWO2019000362A1

Innovation

- Enables partial reconfiguration of FPGA logic blocks without requiring complete overwrite of existing configuration, allowing selective updates while maintaining operation of unchanged blocks.

- Addresses the inefficiency of traditional full-configuration approaches by implementing rapid reconfiguration technologies that minimize downtime in high-performance applications.

- Provides configuration management capabilities that can handle similar or incremental configuration updates more efficiently than complete system reloads.

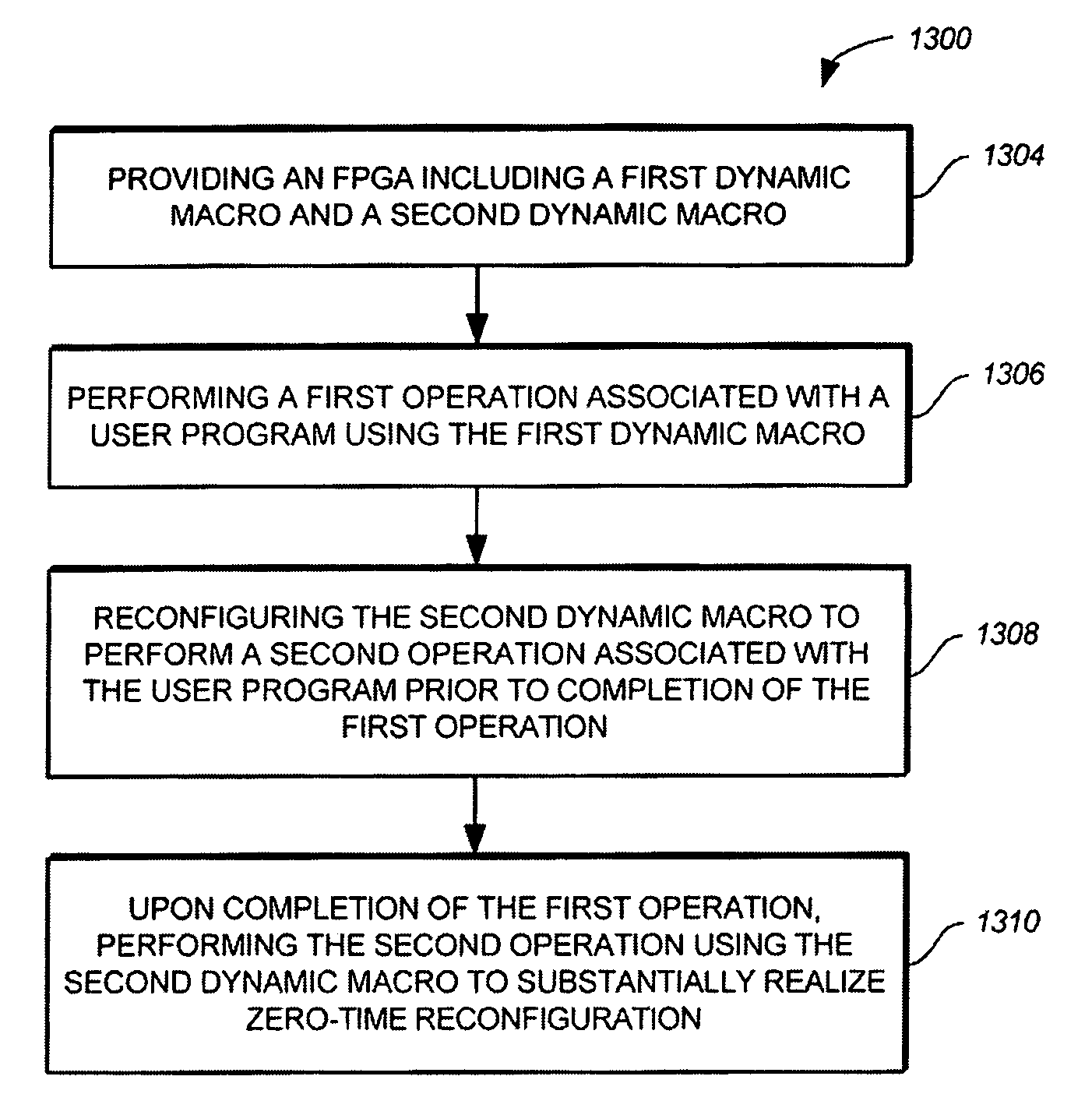

Method and system for dynamic reconfiguration of field programmable gate arrays

PatentInactiveUS20070283311A1

Innovation

- The implementation of a system and method that uses first and second dynamic macros within an FPGA, allowing for zero-time reconfiguration by executing operations concurrently and reconfiguring the second macro during the first operation, with a master bitstream file organizing configuration data for efficient reconfiguration.

Power Consumption Analysis in Reconfigurable Systems

Power consumption represents a critical performance metric when evaluating reconfigurable systems, particularly in the context of logic chips versus FPGA fabrics. The fundamental architectural differences between these technologies create distinct power consumption profiles that significantly impact their deployment in various applications.

Static power consumption in FPGA fabrics typically exceeds that of dedicated logic chips due to the inherent overhead of reconfigurable routing resources and configuration memory. The extensive interconnect networks required for runtime reconfiguration contribute to substantial leakage currents, especially in advanced process nodes. Modern FPGAs implement power gating techniques and multiple voltage domains to mitigate these effects, yet baseline power consumption remains elevated compared to application-specific integrated circuits.

Dynamic power consumption patterns differ markedly between the two approaches. Logic chips optimized for specific functions demonstrate superior power efficiency during active operation, as their fixed routing paths minimize switching activity and parasitic capacitances. Conversely, FPGA implementations often exhibit higher dynamic power due to longer routing paths and additional logic layers required for flexibility.

Reconfiguration events themselves introduce significant power spikes in FPGA systems. Partial reconfiguration can consume substantial energy during the configuration process, with power requirements varying based on the reconfiguration granularity and frequency. Fine-grained reconfiguration typically demands more power per operation but enables more precise resource utilization, while coarse-grained approaches reduce configuration overhead at the expense of flexibility.

Advanced power management strategies have emerged to address these challenges. Dynamic voltage and frequency scaling techniques allow FPGA fabrics to adapt power consumption based on computational requirements. Clock gating and power island methodologies help minimize unnecessary power dissipation in unused logic blocks. Additionally, intelligent reconfiguration scheduling algorithms can optimize power consumption by batching configuration operations and leveraging temporal locality in reconfiguration patterns.

The power efficiency trade-offs become particularly pronounced in battery-powered and thermally constrained environments, where the flexibility benefits of FPGA fabrics must be carefully weighed against their inherently higher power consumption characteristics.

Static power consumption in FPGA fabrics typically exceeds that of dedicated logic chips due to the inherent overhead of reconfigurable routing resources and configuration memory. The extensive interconnect networks required for runtime reconfiguration contribute to substantial leakage currents, especially in advanced process nodes. Modern FPGAs implement power gating techniques and multiple voltage domains to mitigate these effects, yet baseline power consumption remains elevated compared to application-specific integrated circuits.

Dynamic power consumption patterns differ markedly between the two approaches. Logic chips optimized for specific functions demonstrate superior power efficiency during active operation, as their fixed routing paths minimize switching activity and parasitic capacitances. Conversely, FPGA implementations often exhibit higher dynamic power due to longer routing paths and additional logic layers required for flexibility.

Reconfiguration events themselves introduce significant power spikes in FPGA systems. Partial reconfiguration can consume substantial energy during the configuration process, with power requirements varying based on the reconfiguration granularity and frequency. Fine-grained reconfiguration typically demands more power per operation but enables more precise resource utilization, while coarse-grained approaches reduce configuration overhead at the expense of flexibility.

Advanced power management strategies have emerged to address these challenges. Dynamic voltage and frequency scaling techniques allow FPGA fabrics to adapt power consumption based on computational requirements. Clock gating and power island methodologies help minimize unnecessary power dissipation in unused logic blocks. Additionally, intelligent reconfiguration scheduling algorithms can optimize power consumption by batching configuration operations and leveraging temporal locality in reconfiguration patterns.

The power efficiency trade-offs become particularly pronounced in battery-powered and thermally constrained environments, where the flexibility benefits of FPGA fabrics must be carefully weighed against their inherently higher power consumption characteristics.

Performance Benchmarking Methodologies for Logic vs FPGA

Establishing robust performance benchmarking methodologies for comparing logic chips and FPGA fabrics requires a comprehensive framework that addresses the unique characteristics of both architectures. Traditional benchmarking approaches often fall short when evaluating reconfiguration efficiency, as they typically focus on static performance metrics rather than dynamic reconfiguration capabilities that distinguish FPGAs from fixed-function logic chips.

The foundation of effective benchmarking lies in developing standardized test suites that encompass both computational workloads and reconfiguration scenarios. These test suites must include representative applications from various domains such as digital signal processing, cryptography, machine learning inference, and real-time control systems. Each benchmark should capture not only the steady-state performance but also the transition costs associated with reconfiguration events in FPGA implementations.

Temporal analysis methodologies form a critical component of the benchmarking framework. Unlike logic chips that maintain consistent performance characteristics, FPGAs exhibit time-varying behavior during reconfiguration phases. Benchmarking protocols must therefore incorporate metrics such as reconfiguration latency, partial reconfiguration overhead, and context switching delays. These measurements require specialized instrumentation capable of capturing microsecond-level timing variations across different reconfiguration scenarios.

Power consumption benchmarking presents unique challenges when comparing these architectures. Logic chips typically demonstrate predictable power profiles, while FPGA power consumption varies significantly based on resource utilization and reconfiguration frequency. Comprehensive power benchmarking must account for static power during idle states, dynamic power during active computation, and transient power spikes during reconfiguration events.

Resource utilization metrics require architecture-specific adaptations to enable meaningful comparisons. For logic chips, benchmarking focuses on throughput per unit area and performance per watt. FPGA benchmarking must additionally consider lookup table utilization, routing congestion, and the efficiency of partial reconfiguration regions. These metrics provide insights into how effectively each architecture utilizes available silicon resources for specific workloads.

Scalability benchmarking methodologies must evaluate how performance characteristics change with increasing problem sizes and complexity. This includes analyzing how logic chips handle workload scaling through parallel processing units versus how FPGAs adapt through dynamic resource allocation and reconfiguration strategies. Such analysis reveals the crossover points where one architecture becomes more advantageous than the other for specific application domains.

The foundation of effective benchmarking lies in developing standardized test suites that encompass both computational workloads and reconfiguration scenarios. These test suites must include representative applications from various domains such as digital signal processing, cryptography, machine learning inference, and real-time control systems. Each benchmark should capture not only the steady-state performance but also the transition costs associated with reconfiguration events in FPGA implementations.

Temporal analysis methodologies form a critical component of the benchmarking framework. Unlike logic chips that maintain consistent performance characteristics, FPGAs exhibit time-varying behavior during reconfiguration phases. Benchmarking protocols must therefore incorporate metrics such as reconfiguration latency, partial reconfiguration overhead, and context switching delays. These measurements require specialized instrumentation capable of capturing microsecond-level timing variations across different reconfiguration scenarios.

Power consumption benchmarking presents unique challenges when comparing these architectures. Logic chips typically demonstrate predictable power profiles, while FPGA power consumption varies significantly based on resource utilization and reconfiguration frequency. Comprehensive power benchmarking must account for static power during idle states, dynamic power during active computation, and transient power spikes during reconfiguration events.

Resource utilization metrics require architecture-specific adaptations to enable meaningful comparisons. For logic chips, benchmarking focuses on throughput per unit area and performance per watt. FPGA benchmarking must additionally consider lookup table utilization, routing congestion, and the efficiency of partial reconfiguration regions. These metrics provide insights into how effectively each architecture utilizes available silicon resources for specific workloads.

Scalability benchmarking methodologies must evaluate how performance characteristics change with increasing problem sizes and complexity. This includes analyzing how logic chips handle workload scaling through parallel processing units versus how FPGAs adapt through dynamic resource allocation and reconfiguration strategies. Such analysis reveals the crossover points where one architecture becomes more advantageous than the other for specific application domains.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!