Logic Chips in Predictive Maintenance: Fault Detection Efficacy

APR 2, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Logic Chip Predictive Maintenance Background and Objectives

The integration of logic chips in predictive maintenance systems represents a paradigm shift from traditional reactive maintenance approaches to proactive, data-driven strategies. This technological evolution has emerged from the convergence of semiconductor miniaturization, advanced signal processing capabilities, and the growing demand for operational efficiency across industrial sectors. Logic chips serve as the computational backbone for real-time fault detection algorithms, enabling continuous monitoring and analysis of equipment health parameters.

The historical development of predictive maintenance can be traced back to the 1960s when basic vibration monitoring techniques were first employed in industrial settings. However, the incorporation of sophisticated logic chips began gaining momentum in the 1990s with the advent of digital signal processors and microcontrollers capable of handling complex mathematical operations. The exponential growth in processing power, coupled with reduced chip costs, has made advanced predictive maintenance solutions accessible to a broader range of industries.

Current technological trends indicate a significant shift toward edge computing architectures, where logic chips are embedded directly into machinery and equipment. This distributed approach enables real-time processing of sensor data, reducing latency and bandwidth requirements while improving system responsiveness. Field-programmable gate arrays, application-specific integrated circuits, and system-on-chip solutions are increasingly being deployed to handle specialized fault detection algorithms with enhanced efficiency.

The primary objective of implementing logic chips in predictive maintenance systems is to achieve superior fault detection efficacy through advanced pattern recognition and anomaly detection capabilities. These systems aim to identify potential equipment failures before they occur, thereby minimizing unplanned downtime, reducing maintenance costs, and extending asset lifespan. The integration seeks to establish intelligent monitoring networks capable of processing multiple sensor inputs simultaneously while maintaining high accuracy rates in fault classification.

Furthermore, the technology evolution targets the development of adaptive learning systems that can continuously improve their diagnostic capabilities through machine learning algorithms implemented directly on logic chips. This approach enables the creation of self-optimizing maintenance systems that can adapt to changing operational conditions and equipment degradation patterns over time.

The historical development of predictive maintenance can be traced back to the 1960s when basic vibration monitoring techniques were first employed in industrial settings. However, the incorporation of sophisticated logic chips began gaining momentum in the 1990s with the advent of digital signal processors and microcontrollers capable of handling complex mathematical operations. The exponential growth in processing power, coupled with reduced chip costs, has made advanced predictive maintenance solutions accessible to a broader range of industries.

Current technological trends indicate a significant shift toward edge computing architectures, where logic chips are embedded directly into machinery and equipment. This distributed approach enables real-time processing of sensor data, reducing latency and bandwidth requirements while improving system responsiveness. Field-programmable gate arrays, application-specific integrated circuits, and system-on-chip solutions are increasingly being deployed to handle specialized fault detection algorithms with enhanced efficiency.

The primary objective of implementing logic chips in predictive maintenance systems is to achieve superior fault detection efficacy through advanced pattern recognition and anomaly detection capabilities. These systems aim to identify potential equipment failures before they occur, thereby minimizing unplanned downtime, reducing maintenance costs, and extending asset lifespan. The integration seeks to establish intelligent monitoring networks capable of processing multiple sensor inputs simultaneously while maintaining high accuracy rates in fault classification.

Furthermore, the technology evolution targets the development of adaptive learning systems that can continuously improve their diagnostic capabilities through machine learning algorithms implemented directly on logic chips. This approach enables the creation of self-optimizing maintenance systems that can adapt to changing operational conditions and equipment degradation patterns over time.

Market Demand for Predictive Maintenance Solutions

The global predictive maintenance market has experienced substantial growth driven by increasing industrial digitization and the rising costs of unplanned equipment downtime. Manufacturing sectors, particularly automotive, aerospace, and heavy machinery industries, represent the largest demand segments as these sectors face significant financial losses from unexpected equipment failures. The integration of Internet of Things sensors, advanced analytics, and machine learning capabilities has created unprecedented opportunities for logic chip applications in fault detection systems.

Industrial facilities are increasingly recognizing the economic benefits of transitioning from reactive and scheduled maintenance approaches to predictive strategies. Traditional maintenance methods often result in either premature component replacement or catastrophic failures, both of which generate substantial operational costs. Logic chips equipped with sophisticated algorithms can process real-time sensor data to identify subtle patterns indicating potential equipment degradation, enabling maintenance teams to intervene at optimal timing.

The energy sector, including oil and gas operations, power generation facilities, and renewable energy installations, demonstrates particularly strong demand for predictive maintenance solutions. These industries operate critical infrastructure where equipment failures can result in safety hazards, environmental incidents, and significant revenue losses. Logic chips capable of processing complex vibration, temperature, and acoustic signatures provide essential capabilities for early fault detection in rotating machinery, transformers, and pipeline systems.

Transportation and logistics industries are driving additional market demand as fleet operators seek to minimize vehicle downtime and optimize maintenance scheduling. Railway systems, shipping companies, and aviation operators require sophisticated fault detection capabilities to ensure safety compliance while maximizing asset utilization. Logic chips designed for predictive maintenance applications must handle diverse sensor inputs and operate reliably in challenging environmental conditions.

The pharmaceutical and food processing industries present emerging market opportunities as regulatory requirements increasingly emphasize equipment reliability and product quality assurance. These sectors require predictive maintenance solutions that can integrate with existing quality management systems while providing detailed documentation of equipment performance trends. Logic chips supporting these applications must offer high precision analytics and secure data handling capabilities.

Small and medium-sized enterprises represent an expanding market segment as cloud-based predictive maintenance platforms reduce implementation barriers and initial investment requirements. These organizations typically lack dedicated maintenance engineering resources, creating demand for logic chip solutions that provide automated fault detection with minimal configuration requirements.

Industrial facilities are increasingly recognizing the economic benefits of transitioning from reactive and scheduled maintenance approaches to predictive strategies. Traditional maintenance methods often result in either premature component replacement or catastrophic failures, both of which generate substantial operational costs. Logic chips equipped with sophisticated algorithms can process real-time sensor data to identify subtle patterns indicating potential equipment degradation, enabling maintenance teams to intervene at optimal timing.

The energy sector, including oil and gas operations, power generation facilities, and renewable energy installations, demonstrates particularly strong demand for predictive maintenance solutions. These industries operate critical infrastructure where equipment failures can result in safety hazards, environmental incidents, and significant revenue losses. Logic chips capable of processing complex vibration, temperature, and acoustic signatures provide essential capabilities for early fault detection in rotating machinery, transformers, and pipeline systems.

Transportation and logistics industries are driving additional market demand as fleet operators seek to minimize vehicle downtime and optimize maintenance scheduling. Railway systems, shipping companies, and aviation operators require sophisticated fault detection capabilities to ensure safety compliance while maximizing asset utilization. Logic chips designed for predictive maintenance applications must handle diverse sensor inputs and operate reliably in challenging environmental conditions.

The pharmaceutical and food processing industries present emerging market opportunities as regulatory requirements increasingly emphasize equipment reliability and product quality assurance. These sectors require predictive maintenance solutions that can integrate with existing quality management systems while providing detailed documentation of equipment performance trends. Logic chips supporting these applications must offer high precision analytics and secure data handling capabilities.

Small and medium-sized enterprises represent an expanding market segment as cloud-based predictive maintenance platforms reduce implementation barriers and initial investment requirements. These organizations typically lack dedicated maintenance engineering resources, creating demand for logic chip solutions that provide automated fault detection with minimal configuration requirements.

Current State of Logic Chip Fault Detection Technologies

Logic chip fault detection technologies have evolved significantly over the past decade, driven by the increasing complexity of semiconductor devices and the critical need for reliable predictive maintenance systems. Current approaches primarily rely on a combination of electrical parameter monitoring, thermal analysis, and advanced signal processing techniques to identify potential failures before they occur.

Traditional fault detection methods focus on monitoring key electrical characteristics such as voltage fluctuations, current leakage, and timing variations. These parameters serve as early indicators of degradation in logic circuits. Modern systems employ high-resolution analog-to-digital converters and specialized measurement circuits integrated directly onto the chip substrate, enabling real-time monitoring of critical performance metrics.

Machine learning algorithms have become increasingly prevalent in contemporary fault detection frameworks. Support vector machines, neural networks, and ensemble methods are commonly deployed to analyze patterns in electrical signatures and predict failure modes. These algorithms process vast amounts of operational data to establish baseline performance profiles and detect anomalous behavior that may indicate impending failures.

Built-in self-test (BIST) architectures represent another significant advancement in current technology. These systems incorporate dedicated test circuits within the logic chip design, enabling autonomous fault detection without external test equipment. BIST implementations typically include linear feedback shift registers for test pattern generation and signature analysis circuits for response evaluation.

Thermal monitoring has emerged as a critical component of modern fault detection systems. Temperature sensors distributed across the chip surface provide real-time thermal mapping, allowing detection of hotspots and thermal cycling effects that contribute to reliability degradation. Advanced thermal models correlate temperature variations with electrical performance to predict failure probability.

Power consumption analysis offers additional insights into chip health status. Dynamic power monitoring circuits track current consumption patterns and identify deviations that may indicate developing faults. This approach is particularly effective for detecting early-stage degradation in transistor characteristics and interconnect resistance changes.

Current limitations include the challenge of distinguishing between normal operational variations and genuine fault conditions, particularly in harsh environmental conditions. Additionally, the integration of comprehensive monitoring systems introduces area and power overhead concerns that must be balanced against detection accuracy requirements.

Traditional fault detection methods focus on monitoring key electrical characteristics such as voltage fluctuations, current leakage, and timing variations. These parameters serve as early indicators of degradation in logic circuits. Modern systems employ high-resolution analog-to-digital converters and specialized measurement circuits integrated directly onto the chip substrate, enabling real-time monitoring of critical performance metrics.

Machine learning algorithms have become increasingly prevalent in contemporary fault detection frameworks. Support vector machines, neural networks, and ensemble methods are commonly deployed to analyze patterns in electrical signatures and predict failure modes. These algorithms process vast amounts of operational data to establish baseline performance profiles and detect anomalous behavior that may indicate impending failures.

Built-in self-test (BIST) architectures represent another significant advancement in current technology. These systems incorporate dedicated test circuits within the logic chip design, enabling autonomous fault detection without external test equipment. BIST implementations typically include linear feedback shift registers for test pattern generation and signature analysis circuits for response evaluation.

Thermal monitoring has emerged as a critical component of modern fault detection systems. Temperature sensors distributed across the chip surface provide real-time thermal mapping, allowing detection of hotspots and thermal cycling effects that contribute to reliability degradation. Advanced thermal models correlate temperature variations with electrical performance to predict failure probability.

Power consumption analysis offers additional insights into chip health status. Dynamic power monitoring circuits track current consumption patterns and identify deviations that may indicate developing faults. This approach is particularly effective for detecting early-stage degradation in transistor characteristics and interconnect resistance changes.

Current limitations include the challenge of distinguishing between normal operational variations and genuine fault conditions, particularly in harsh environmental conditions. Additionally, the integration of comprehensive monitoring systems introduces area and power overhead concerns that must be balanced against detection accuracy requirements.

Existing Fault Detection Solutions for Logic Chips

01 Built-in self-test (BIST) mechanisms for logic chips

Built-in self-test mechanisms enable logic chips to perform autonomous fault detection without external test equipment. These mechanisms incorporate dedicated test circuits within the chip architecture that can generate test patterns, apply them to the logic circuits, and analyze the responses to identify faults. This approach improves fault detection efficacy by enabling comprehensive testing during manufacturing, field operation, and maintenance phases.- Built-in self-test (BIST) mechanisms for logic chips: Built-in self-test mechanisms enable logic chips to perform autonomous fault detection without external test equipment. These systems incorporate dedicated test pattern generators and response analyzers within the chip architecture to identify manufacturing defects and operational faults. The BIST approach improves test coverage while reducing testing time and costs, making it particularly effective for complex integrated circuits where external testing would be impractical.

- Scan chain and boundary scan testing techniques: Scan chain methodologies involve connecting sequential elements in a chain configuration to enable systematic testing of internal logic states. Boundary scan techniques provide standardized test access to chip pins and internal nodes, facilitating comprehensive fault detection at the chip boundaries and interconnections. These approaches allow for efficient testing of complex logic structures and improve observability and controllability of internal circuit nodes.

- Signature analysis and compression methods: Signature analysis techniques compress test response data into compact signatures that can be compared against known good values to detect faults. These methods utilize linear feedback shift registers or similar compression circuits to reduce the volume of test data while maintaining high fault detection capability. The compression approach enables efficient testing of large logic circuits by minimizing data storage and transmission requirements.

- Machine learning and AI-based fault detection: Advanced fault detection systems employ machine learning algorithms and artificial intelligence to identify anomalous behavior patterns in logic chip operation. These intelligent systems can learn normal operational characteristics and detect deviations that indicate potential faults, including subtle defects that traditional methods might miss. The adaptive nature of these approaches enables improved detection efficacy over time as the system accumulates operational data.

- Redundancy and error correction techniques: Fault detection efficacy can be enhanced through redundancy schemes that incorporate duplicate logic elements or error correction codes. These techniques enable the system to not only detect faults but also identify their location and potentially correct errors in real-time. Redundancy-based approaches are particularly valuable for mission-critical applications where continuous operation and high reliability are essential requirements.

02 Scan chain and boundary scan techniques

Scan chain and boundary scan techniques provide systematic methods for testing logic chips by converting sequential logic into a testable configuration. These techniques allow test data to be shifted through the chip's internal registers, enabling observation and control of internal nodes that are otherwise inaccessible. This methodology significantly enhances fault detection coverage and reduces the complexity of identifying defects in complex integrated circuits.Expand Specific Solutions03 Signature analysis and response compression

Signature analysis and response compression techniques reduce the volume of test data by compressing circuit responses into compact signatures that can be compared against known good values. These methods employ linear feedback shift registers or similar structures to generate characteristic signatures from test responses, enabling efficient fault detection while minimizing test time and data storage requirements. This approach is particularly effective for detecting both stuck-at faults and transition faults.Expand Specific Solutions04 Machine learning and AI-based fault detection

Machine learning and artificial intelligence techniques are increasingly applied to enhance fault detection efficacy in logic chips. These approaches utilize trained models to identify patterns indicative of faults, predict potential failures, and classify defect types based on test data analysis. By learning from historical test data and failure modes, these systems can improve detection accuracy and identify subtle or intermittent faults that traditional methods might miss.Expand Specific Solutions05 Delay fault testing and timing analysis

Delay fault testing and timing analysis methods focus on detecting faults that affect the propagation delay of signals through logic circuits rather than causing logical errors. These techniques apply at-speed testing to identify defects that may cause timing violations, which are increasingly important in high-performance chips. The methods involve generating test patterns that sensitize critical paths and measuring whether signals arrive within specified timing windows, thereby improving the detection of performance-related defects.Expand Specific Solutions

Key Players in Logic Chip Predictive Maintenance Industry

The predictive maintenance sector utilizing logic chips for fault detection represents a rapidly maturing market experiencing significant growth driven by Industry 4.0 initiatives. The competitive landscape spans multiple development stages, from established industrial automation leaders to emerging AI-specialized firms. Market incumbents like Siemens AG, Mitsubishi Electric, and OMRON dominate with comprehensive industrial IoT platforms, while technology giants such as NVIDIA and Applied Materials provide essential semiconductor infrastructure. The technology demonstrates high maturity in traditional sectors, evidenced by Hitachi's integrated solutions and Bosch's automotive applications. However, emerging players like ODYSIGHT.AI represent the cutting-edge AI-driven analytics segment. The convergence of established industrial expertise with advanced semiconductor capabilities from companies like Fujitsu and NEC creates a highly competitive environment where fault detection efficacy increasingly depends on sophisticated logic chip integration and machine learning algorithms.

Siemens AG

Technical Solution: Siemens has developed comprehensive predictive maintenance solutions utilizing advanced logic chips integrated with their MindSphere IoT platform. Their approach combines edge computing devices equipped with specialized processors for real-time data acquisition and analysis. The system employs machine learning algorithms running on embedded logic chips to detect anomalies in industrial equipment, achieving fault detection accuracy rates of up to 95% in manufacturing environments. Their SIMATIC edge devices incorporate ARM-based processors and FPGA chips optimized for predictive analytics, enabling continuous monitoring of vibration, temperature, and acoustic signatures to predict equipment failures before they occur.

Strengths: Comprehensive industrial IoT ecosystem, high fault detection accuracy, real-time processing capabilities. Weaknesses: High implementation costs, complex system integration requirements.

Mitsubishi Electric Corp.

Technical Solution: Mitsubishi Electric has developed the MELSEC iQ-R series PLCs integrated with AI-enhanced predictive maintenance capabilities. Their solution incorporates dedicated signal processing chips and embedded controllers that perform real-time condition monitoring and fault prediction. The system utilizes proprietary algorithms running on ARM Cortex processors to analyze equipment performance data, achieving fault detection lead times of 2-4 weeks before actual failures occur. Their e-F@ctory concept integrates these logic chips across manufacturing lines, enabling comprehensive asset health monitoring with detection accuracy rates of approximately 92% for rotating machinery and 88% for static equipment components.

Strengths: Proven industrial automation expertise, integrated factory-wide solutions, reliable hardware platform. Weaknesses: Limited AI processing capabilities compared to specialized chips, proprietary ecosystem constraints.

Core Innovations in Logic Chip Fault Prediction

Failure Detection and Mitigation in Logic Circuits

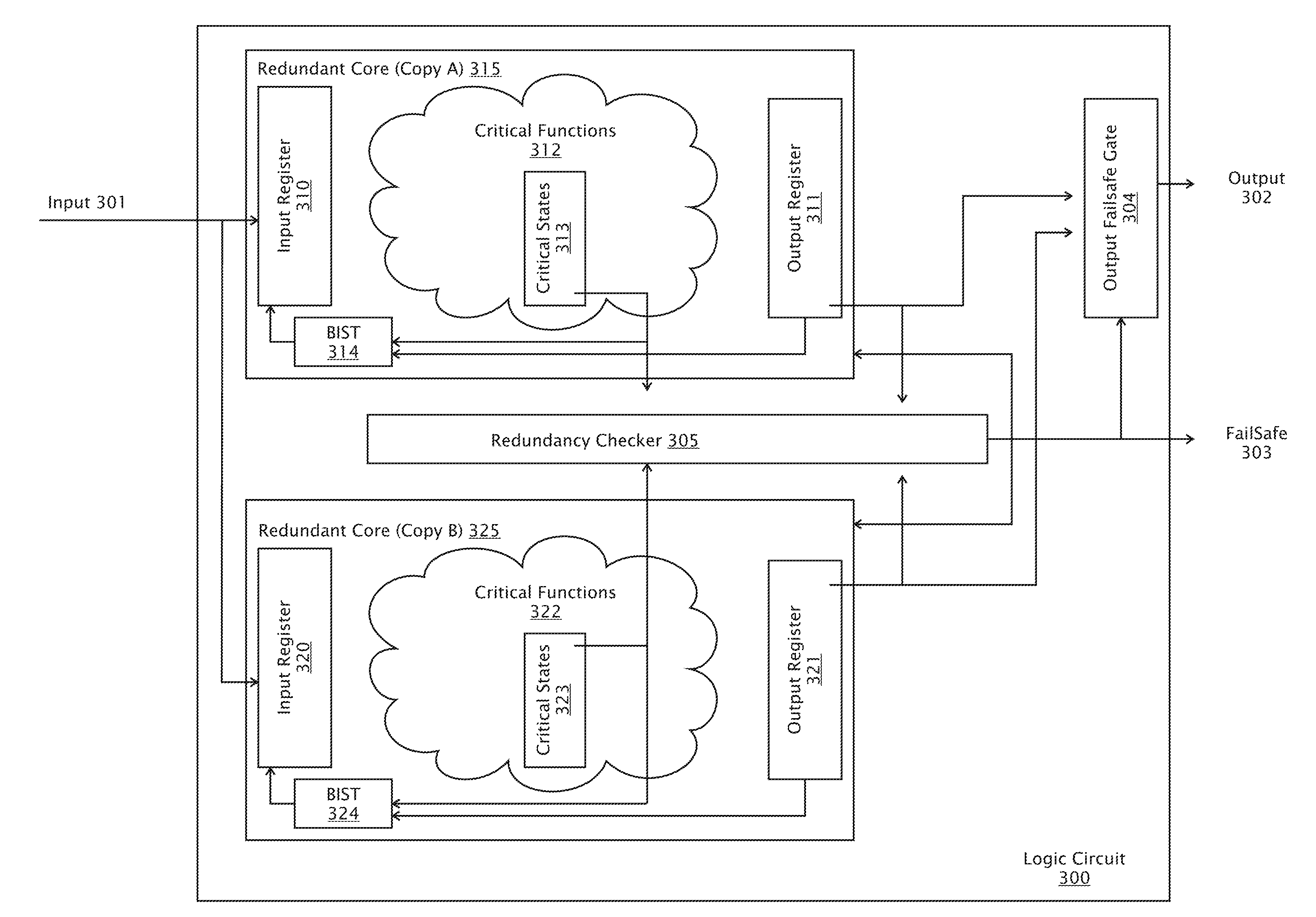

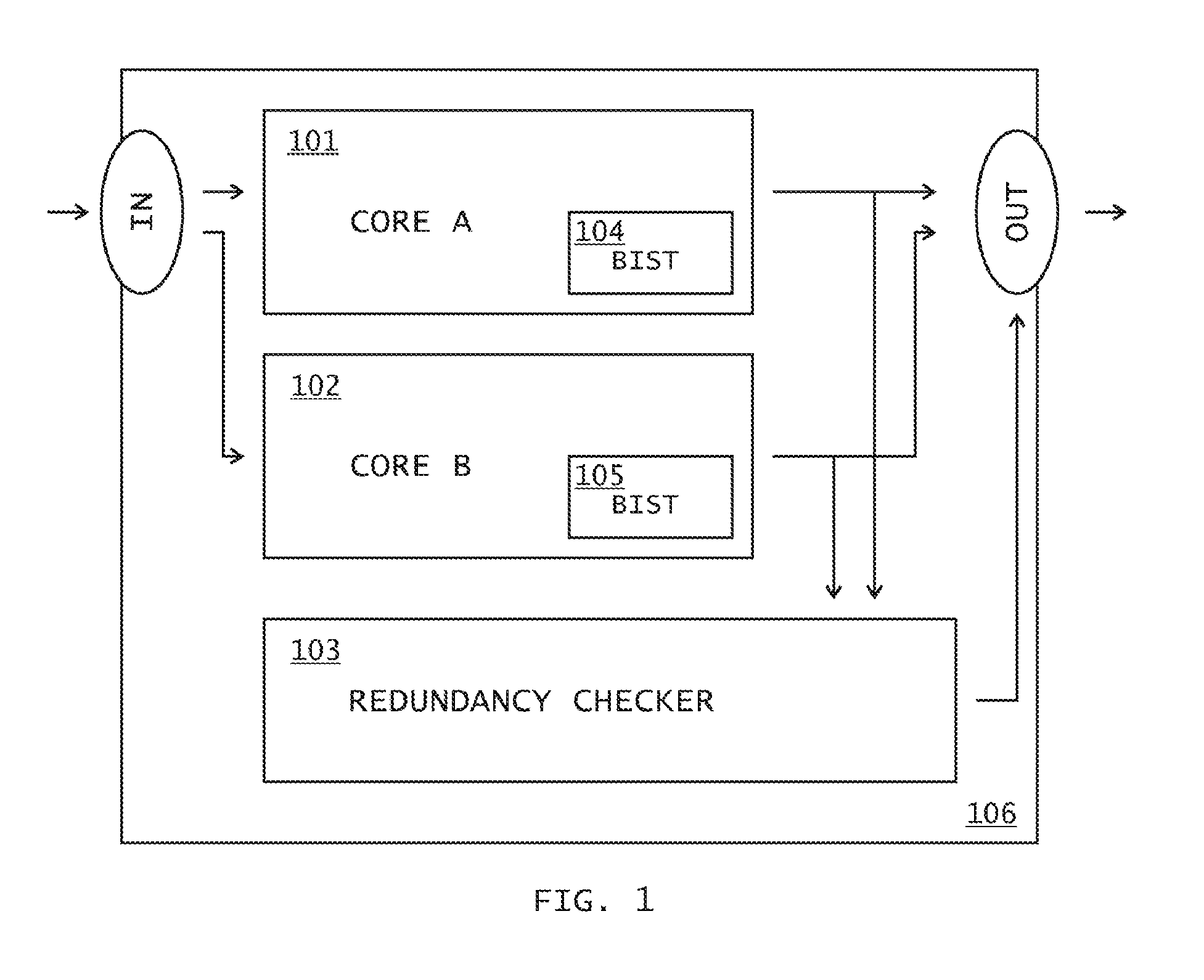

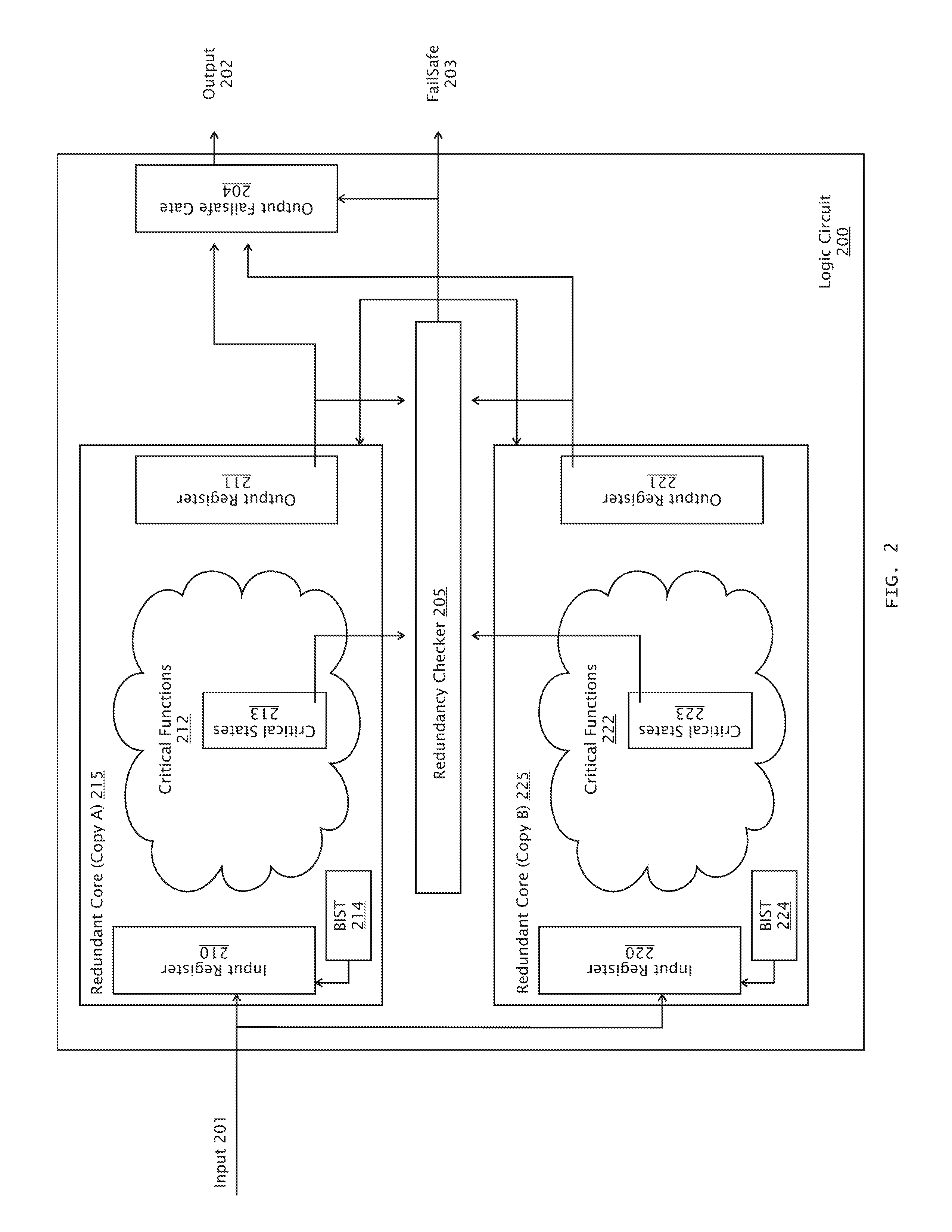

PatentActiveUS20110209021A1

Innovation

- The implementation of parallel logic circuit cores with a redundancy checker to detect failures by comparing parallel paths for equivalence and a built-in self-test engine to periodically exercise individual paths, ensuring unannounced failures are exposed without affecting ongoing processes, combined with hardware-based logic devices to minimize software dependency.

Logic circuit fault diagnosis method and apparatus

PatentActiveKR1020230101977A

Innovation

- A neural network is trained using fault images formed from input test patterns injected into logic circuits, where output bit values are mapped to pixel values to quickly detect failures.

Industrial Standards for Predictive Maintenance Systems

The industrial standardization landscape for predictive maintenance systems has evolved significantly to address the growing complexity of fault detection technologies, particularly those incorporating advanced logic chips. Current standards framework encompasses multiple layers of requirements, from hardware specifications to data interoperability protocols, ensuring that predictive maintenance solutions can operate effectively across diverse industrial environments.

ISO 13374 series represents the foundational framework for condition monitoring and diagnostics of machines, establishing comprehensive guidelines for data acquisition, processing, and analysis in predictive maintenance applications. This standard specifically addresses the integration of intelligent processing units, including logic chips, within monitoring systems. The standard defines six-block architecture that encompasses data acquisition, data manipulation, state detection, health assessment, prognostic assessment, and advisory generation, providing clear guidelines for implementing chip-based fault detection systems.

IEEE 1451 family of standards plays a crucial role in defining smart transducer interfaces, which directly impacts how logic chips communicate within predictive maintenance networks. These standards establish protocols for sensor-to-network connectivity, enabling seamless integration of intelligent fault detection devices. The standardization ensures that logic chip-based sensors can communicate effectively with central monitoring systems, regardless of manufacturer or specific implementation details.

IEC 62264 and IEC 62443 standards address enterprise-control system integration and industrial communication network security respectively. These frameworks are particularly relevant for logic chip implementations in predictive maintenance, as they define how intelligent monitoring devices should integrate with broader manufacturing execution systems while maintaining cybersecurity requirements. The standards ensure that chip-based fault detection systems can operate within existing industrial infrastructure without compromising operational security.

MIMOSA standards, particularly the Open Systems Architecture for Enterprise Application Integration (OSA-EAI), provide specific guidelines for predictive maintenance data management and system interoperability. These standards define how logic chip-generated fault detection data should be structured, stored, and shared across different platforms and applications, ensuring consistency in predictive maintenance implementations across various industrial sectors.

ISO 13374 series represents the foundational framework for condition monitoring and diagnostics of machines, establishing comprehensive guidelines for data acquisition, processing, and analysis in predictive maintenance applications. This standard specifically addresses the integration of intelligent processing units, including logic chips, within monitoring systems. The standard defines six-block architecture that encompasses data acquisition, data manipulation, state detection, health assessment, prognostic assessment, and advisory generation, providing clear guidelines for implementing chip-based fault detection systems.

IEEE 1451 family of standards plays a crucial role in defining smart transducer interfaces, which directly impacts how logic chips communicate within predictive maintenance networks. These standards establish protocols for sensor-to-network connectivity, enabling seamless integration of intelligent fault detection devices. The standardization ensures that logic chip-based sensors can communicate effectively with central monitoring systems, regardless of manufacturer or specific implementation details.

IEC 62264 and IEC 62443 standards address enterprise-control system integration and industrial communication network security respectively. These frameworks are particularly relevant for logic chip implementations in predictive maintenance, as they define how intelligent monitoring devices should integrate with broader manufacturing execution systems while maintaining cybersecurity requirements. The standards ensure that chip-based fault detection systems can operate within existing industrial infrastructure without compromising operational security.

MIMOSA standards, particularly the Open Systems Architecture for Enterprise Application Integration (OSA-EAI), provide specific guidelines for predictive maintenance data management and system interoperability. These standards define how logic chip-generated fault detection data should be structured, stored, and shared across different platforms and applications, ensuring consistency in predictive maintenance implementations across various industrial sectors.

Cost-Benefit Analysis of Logic Chip Predictive Solutions

The economic evaluation of logic chip-based predictive maintenance solutions reveals compelling financial advantages across multiple operational dimensions. Initial capital expenditure typically ranges from $50,000 to $500,000 per facility, depending on system complexity and coverage scope. However, the return on investment demonstrates substantial value creation through reduced unplanned downtime, which can cost manufacturing facilities between $50,000 to $2 million per hour depending on industry sector.

Operational cost savings emerge through optimized maintenance scheduling and resource allocation. Logic chip solutions enable condition-based maintenance strategies that reduce routine maintenance costs by 25-35% while extending equipment lifespan by 15-20%. The precision of fault detection algorithms minimizes false positives, preventing unnecessary maintenance interventions that traditionally consume 20-30% of maintenance budgets.

Labor efficiency improvements constitute another significant benefit stream. Automated fault detection reduces the need for manual inspection routines, allowing maintenance teams to focus on value-added activities. Organizations typically report 40-60% reduction in diagnostic time and 30% improvement in maintenance crew productivity within the first year of implementation.

Risk mitigation benefits provide substantial but often undervalued returns. Logic chip systems reduce catastrophic failure probability by 70-85%, preventing potential safety incidents, environmental damage, and regulatory penalties. Insurance premium reductions of 10-15% are commonly achieved due to improved risk profiles.

The total cost of ownership analysis over a five-year period typically shows break-even points between 8-18 months, with cumulative savings reaching 300-500% of initial investment. Energy efficiency gains through optimized equipment operation contribute additional savings of 5-12% in operational energy costs.

However, implementation costs extend beyond hardware acquisition to include system integration, staff training, and ongoing software licensing fees. Organizations must also consider cybersecurity infrastructure investments and potential production disruptions during deployment phases.

Operational cost savings emerge through optimized maintenance scheduling and resource allocation. Logic chip solutions enable condition-based maintenance strategies that reduce routine maintenance costs by 25-35% while extending equipment lifespan by 15-20%. The precision of fault detection algorithms minimizes false positives, preventing unnecessary maintenance interventions that traditionally consume 20-30% of maintenance budgets.

Labor efficiency improvements constitute another significant benefit stream. Automated fault detection reduces the need for manual inspection routines, allowing maintenance teams to focus on value-added activities. Organizations typically report 40-60% reduction in diagnostic time and 30% improvement in maintenance crew productivity within the first year of implementation.

Risk mitigation benefits provide substantial but often undervalued returns. Logic chip systems reduce catastrophic failure probability by 70-85%, preventing potential safety incidents, environmental damage, and regulatory penalties. Insurance premium reductions of 10-15% are commonly achieved due to improved risk profiles.

The total cost of ownership analysis over a five-year period typically shows break-even points between 8-18 months, with cumulative savings reaching 300-500% of initial investment. Energy efficiency gains through optimized equipment operation contribute additional savings of 5-12% in operational energy costs.

However, implementation costs extend beyond hardware acquisition to include system integration, staff training, and ongoing software licensing fees. Organizations must also consider cybersecurity infrastructure investments and potential production disruptions during deployment phases.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!