How to Set Up Phase-Locked Loop Oscillators for Stability

MAR 13, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

PLL Oscillator Technology Background and Stability Goals

Phase-locked loop (PLL) oscillators represent a fundamental building block in modern electronic systems, with their development tracing back to the 1930s when they were first conceived for synchronous motor control applications. The technology gained significant momentum during the space race era of the 1960s, where precise frequency synthesis and signal synchronization became critical for satellite communications and navigation systems.

The evolution of PLL technology has been driven by the increasing demand for stable, low-noise frequency sources across diverse applications. From early analog implementations using discrete components to today's sophisticated digital and hybrid architectures, PLL oscillators have undergone continuous refinement to meet stringent stability requirements in telecommunications, computing, and precision instrumentation.

Contemporary PLL oscillator systems face unprecedented challenges in achieving stability across multiple performance dimensions. Phase noise, frequency drift, and lock acquisition time have emerged as primary concerns, particularly as operating frequencies extend into millimeter-wave ranges and system integration densities increase. The proliferation of wireless communication standards and high-speed digital interfaces has further intensified the need for ultra-stable frequency references.

The primary stability goals for modern PLL oscillators encompass several critical parameters. Phase noise performance must typically achieve levels below -100 dBc/Hz at 10 kHz offset for high-performance applications, while maintaining frequency accuracy within parts-per-million tolerances across temperature and supply voltage variations. Lock time requirements have become increasingly stringent, with many applications demanding acquisition times under 100 microseconds.

Temperature stability represents another crucial objective, as PLL oscillators must maintain consistent performance across industrial temperature ranges spanning -40°C to +85°C. Supply voltage rejection and immunity to electromagnetic interference have also become essential stability criteria, particularly in automotive and aerospace applications where harsh operating environments are commonplace.

The convergence of Internet of Things devices, 5G communications, and autonomous systems has established new benchmarks for PLL oscillator stability. These applications demand not only exceptional frequency accuracy but also ultra-low power consumption and compact form factors, creating a complex optimization challenge that drives continued innovation in PLL architecture and implementation methodologies.

The evolution of PLL technology has been driven by the increasing demand for stable, low-noise frequency sources across diverse applications. From early analog implementations using discrete components to today's sophisticated digital and hybrid architectures, PLL oscillators have undergone continuous refinement to meet stringent stability requirements in telecommunications, computing, and precision instrumentation.

Contemporary PLL oscillator systems face unprecedented challenges in achieving stability across multiple performance dimensions. Phase noise, frequency drift, and lock acquisition time have emerged as primary concerns, particularly as operating frequencies extend into millimeter-wave ranges and system integration densities increase. The proliferation of wireless communication standards and high-speed digital interfaces has further intensified the need for ultra-stable frequency references.

The primary stability goals for modern PLL oscillators encompass several critical parameters. Phase noise performance must typically achieve levels below -100 dBc/Hz at 10 kHz offset for high-performance applications, while maintaining frequency accuracy within parts-per-million tolerances across temperature and supply voltage variations. Lock time requirements have become increasingly stringent, with many applications demanding acquisition times under 100 microseconds.

Temperature stability represents another crucial objective, as PLL oscillators must maintain consistent performance across industrial temperature ranges spanning -40°C to +85°C. Supply voltage rejection and immunity to electromagnetic interference have also become essential stability criteria, particularly in automotive and aerospace applications where harsh operating environments are commonplace.

The convergence of Internet of Things devices, 5G communications, and autonomous systems has established new benchmarks for PLL oscillator stability. These applications demand not only exceptional frequency accuracy but also ultra-low power consumption and compact form factors, creating a complex optimization challenge that drives continued innovation in PLL architecture and implementation methodologies.

Market Demand for High-Stability PLL Applications

The telecommunications industry represents the largest market segment driving demand for high-stability phase-locked loop oscillators. Modern 5G networks require precise frequency synchronization across base stations to maintain signal integrity and minimize interference. Network infrastructure equipment, including routers, switches, and optical transport systems, relies heavily on stable PLL circuits to ensure reliable data transmission rates and maintain synchronization protocols. The ongoing global 5G deployment has significantly amplified requirements for frequency stability performance, with specifications demanding phase noise levels below -140 dBc/Hz at 10 kHz offset frequencies.

Aerospace and defense applications constitute another critical market segment where PLL stability directly impacts mission-critical operations. Radar systems, satellite communications, and electronic warfare equipment demand exceptional frequency stability to maintain target tracking accuracy and secure communication links. Military-grade applications often require temperature stability coefficients better than 1 ppm across extended operating ranges, driving specialized PLL design requirements that exceed commercial standards.

The automotive sector has emerged as a rapidly growing market for high-stability PLLs, particularly with the advancement of autonomous driving technologies. Advanced driver assistance systems, vehicle-to-vehicle communication protocols, and precision GPS navigation systems require stable frequency references to ensure safety-critical functions operate reliably. Automotive radar systems operating at 77 GHz and 79 GHz bands demand phase noise performance that directly correlates with detection range and resolution capabilities.

Industrial automation and test equipment markets continue expanding their requirements for precision timing solutions. High-speed data acquisition systems, automated test equipment, and precision measurement instruments rely on stable PLL circuits to maintain measurement accuracy and repeatability. Manufacturing processes in semiconductor fabrication and precision machining increasingly depend on synchronized timing systems that utilize high-stability oscillators.

The medical device industry presents specialized demands for PLL stability, particularly in diagnostic imaging equipment and patient monitoring systems. MRI machines, CT scanners, and ultrasound equipment require precise frequency control to generate clear imaging results and maintain patient safety standards. Regulatory compliance requirements in medical applications often mandate stability specifications that exceed typical commercial standards.

Emerging applications in quantum computing and scientific research are creating new market opportunities for ultra-high stability PLL solutions. These applications often require frequency stability performance approaching atomic clock precision, pushing the boundaries of conventional PLL design methodologies and creating demand for innovative stability enhancement techniques.

Aerospace and defense applications constitute another critical market segment where PLL stability directly impacts mission-critical operations. Radar systems, satellite communications, and electronic warfare equipment demand exceptional frequency stability to maintain target tracking accuracy and secure communication links. Military-grade applications often require temperature stability coefficients better than 1 ppm across extended operating ranges, driving specialized PLL design requirements that exceed commercial standards.

The automotive sector has emerged as a rapidly growing market for high-stability PLLs, particularly with the advancement of autonomous driving technologies. Advanced driver assistance systems, vehicle-to-vehicle communication protocols, and precision GPS navigation systems require stable frequency references to ensure safety-critical functions operate reliably. Automotive radar systems operating at 77 GHz and 79 GHz bands demand phase noise performance that directly correlates with detection range and resolution capabilities.

Industrial automation and test equipment markets continue expanding their requirements for precision timing solutions. High-speed data acquisition systems, automated test equipment, and precision measurement instruments rely on stable PLL circuits to maintain measurement accuracy and repeatability. Manufacturing processes in semiconductor fabrication and precision machining increasingly depend on synchronized timing systems that utilize high-stability oscillators.

The medical device industry presents specialized demands for PLL stability, particularly in diagnostic imaging equipment and patient monitoring systems. MRI machines, CT scanners, and ultrasound equipment require precise frequency control to generate clear imaging results and maintain patient safety standards. Regulatory compliance requirements in medical applications often mandate stability specifications that exceed typical commercial standards.

Emerging applications in quantum computing and scientific research are creating new market opportunities for ultra-high stability PLL solutions. These applications often require frequency stability performance approaching atomic clock precision, pushing the boundaries of conventional PLL design methodologies and creating demand for innovative stability enhancement techniques.

Current PLL Stability Challenges and Technical Barriers

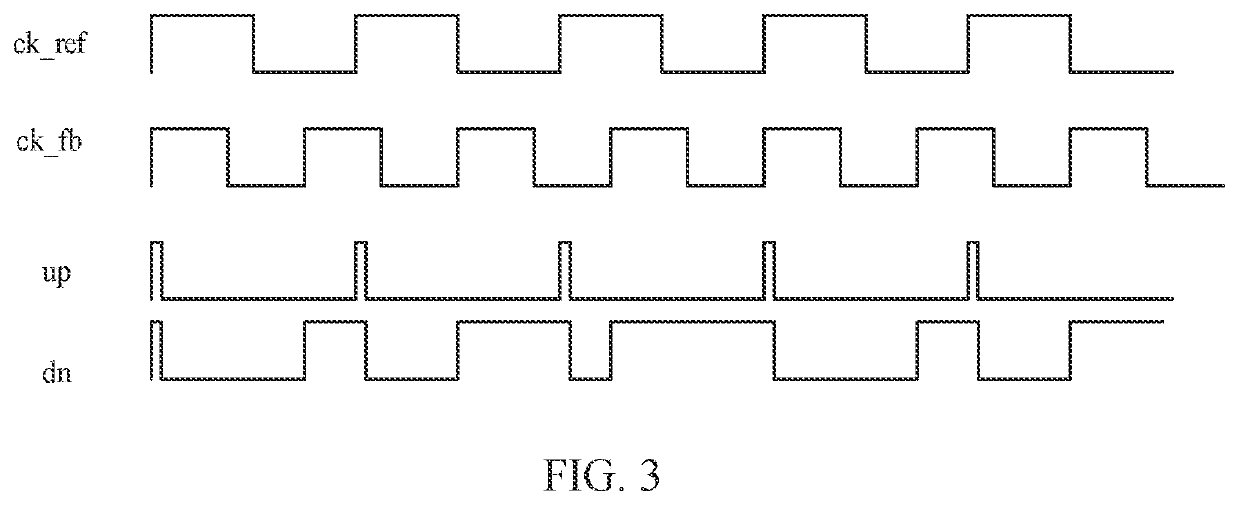

Phase-locked loop oscillators face significant stability challenges that stem from both fundamental design limitations and external environmental factors. The primary technical barrier lies in achieving optimal loop bandwidth selection, where engineers must balance between fast settling time and noise rejection capabilities. A narrow bandwidth provides excellent noise filtering but results in slow transient response, while wider bandwidths enable rapid frequency acquisition at the cost of increased susceptibility to reference clock jitter and voltage-controlled oscillator noise.

Temperature-induced frequency drift represents another critical stability challenge, particularly in voltage-controlled oscillators where semiconductor junction characteristics vary significantly across operating temperature ranges. This thermal sensitivity can cause frequency deviations of several parts per million, severely compromising long-term stability requirements in precision applications such as telecommunications infrastructure and high-speed data converters.

Power supply rejection ratio limitations create substantial technical barriers in modern integrated circuit environments. As supply voltages continue to decrease while switching noise increases, maintaining stable PLL operation becomes increasingly difficult. Charge pump current mismatches and leakage currents in the loop filter further exacerbate these issues, leading to static phase errors and reference spurs that degrade overall system performance.

Phase noise accumulation across multiple PLL stages presents complex engineering challenges, especially in frequency synthesis applications requiring low jitter clock generation. The multiplicative nature of phase noise in frequency multiplication scenarios means that even small noise contributions from individual components can result in significant degradation of the output signal quality.

Lock acquisition and cycle slipping issues pose additional technical barriers, particularly in applications with dynamic frequency requirements or harsh electromagnetic environments. False lock conditions can occur when the PLL settles to incorrect frequency relationships, while cycle slipping during transient events can cause temporary loss of synchronization and system instability.

Manufacturing process variations introduce statistical uncertainties in component matching, affecting charge pump symmetry and loop filter characteristics. These variations necessitate complex calibration schemes and adaptive control mechanisms, increasing design complexity and silicon area requirements while potentially introducing new failure modes that compromise overall reliability.

Temperature-induced frequency drift represents another critical stability challenge, particularly in voltage-controlled oscillators where semiconductor junction characteristics vary significantly across operating temperature ranges. This thermal sensitivity can cause frequency deviations of several parts per million, severely compromising long-term stability requirements in precision applications such as telecommunications infrastructure and high-speed data converters.

Power supply rejection ratio limitations create substantial technical barriers in modern integrated circuit environments. As supply voltages continue to decrease while switching noise increases, maintaining stable PLL operation becomes increasingly difficult. Charge pump current mismatches and leakage currents in the loop filter further exacerbate these issues, leading to static phase errors and reference spurs that degrade overall system performance.

Phase noise accumulation across multiple PLL stages presents complex engineering challenges, especially in frequency synthesis applications requiring low jitter clock generation. The multiplicative nature of phase noise in frequency multiplication scenarios means that even small noise contributions from individual components can result in significant degradation of the output signal quality.

Lock acquisition and cycle slipping issues pose additional technical barriers, particularly in applications with dynamic frequency requirements or harsh electromagnetic environments. False lock conditions can occur when the PLL settles to incorrect frequency relationships, while cycle slipping during transient events can cause temporary loss of synchronization and system instability.

Manufacturing process variations introduce statistical uncertainties in component matching, affecting charge pump symmetry and loop filter characteristics. These variations necessitate complex calibration schemes and adaptive control mechanisms, increasing design complexity and silicon area requirements while potentially introducing new failure modes that compromise overall reliability.

Existing PLL Stability Enhancement Solutions

01 Voltage-controlled oscillator design for improved stability

Phase-locked loop stability can be enhanced through optimized voltage-controlled oscillator (VCO) designs that minimize phase noise and frequency drift. Advanced VCO architectures incorporate temperature compensation circuits, improved bias networks, and noise filtering techniques to maintain stable oscillation frequencies across varying operating conditions. These designs focus on reducing sensitivity to supply voltage variations and environmental factors that can affect loop stability.- Voltage-controlled oscillator design for improved stability: Phase-locked loop stability can be enhanced through optimized voltage-controlled oscillator (VCO) designs that minimize phase noise and frequency drift. Advanced VCO architectures incorporate temperature compensation circuits, improved bias networks, and noise filtering techniques to maintain stable oscillation frequencies across varying operating conditions. These designs focus on reducing sensitivity to supply voltage variations and environmental factors that can affect loop stability.

- Loop filter optimization and bandwidth control: Stability in phase-locked loops can be achieved through careful design of loop filters that control the bandwidth and damping characteristics of the feedback system. Proper filter design ensures adequate phase margin and prevents oscillations or instability in the locked state. Techniques include multi-order filter implementations, adaptive bandwidth adjustment, and charge pump optimization to maintain stable lock conditions across different frequency ranges and operating modes.

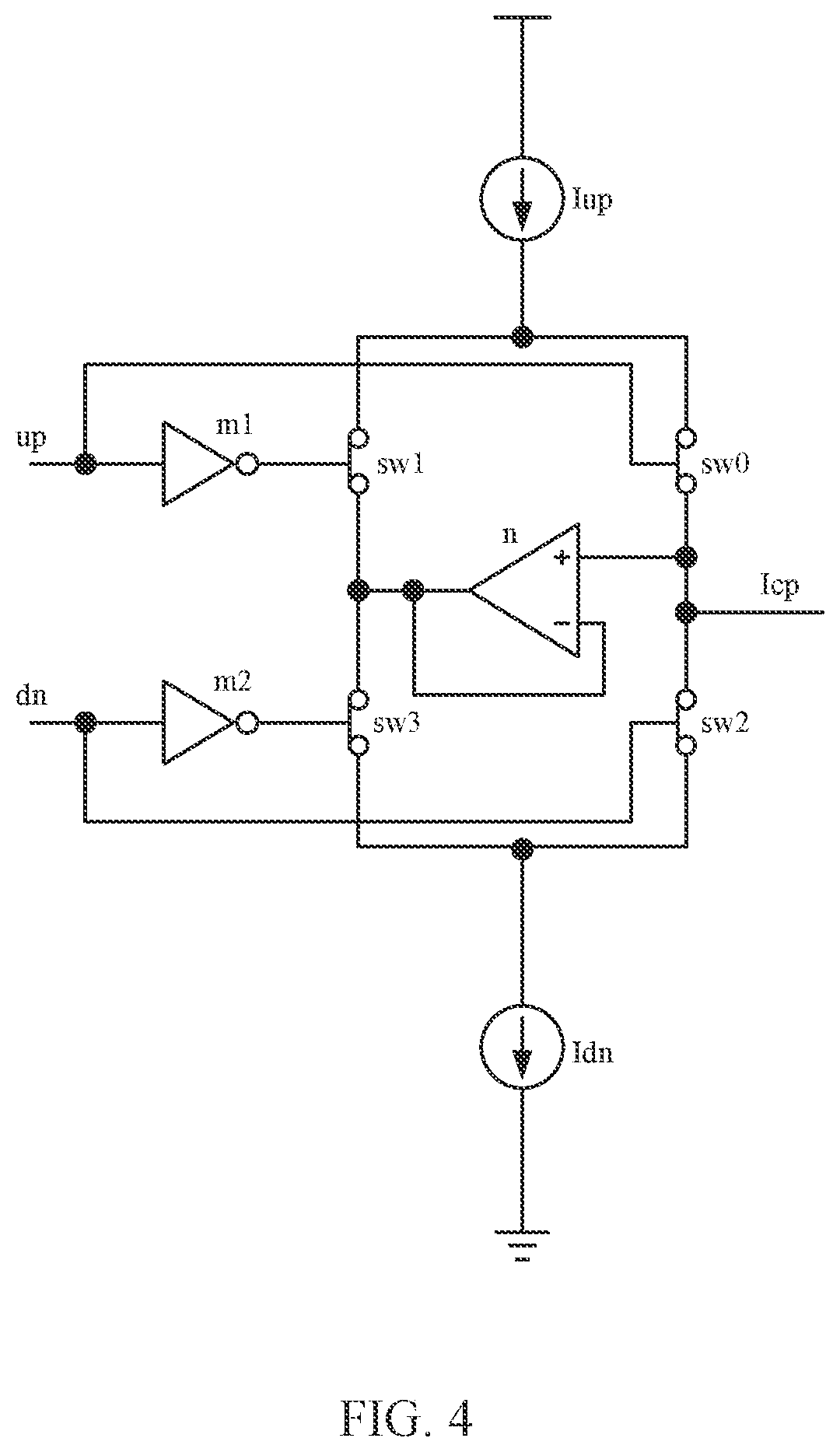

- Phase detector and charge pump stability enhancement: Improved phase detector architectures and charge pump circuits contribute significantly to overall phase-locked loop stability. Advanced phase detection methods reduce dead zones, minimize phase offset errors, and provide linear phase-to-voltage conversion characteristics. Charge pump designs with matched current sources, reduced current mismatch, and improved switching characteristics help maintain stable loop operation and reduce reference spurs.

- Frequency divider and feedback path stabilization: Stability improvements can be achieved through optimized frequency divider designs in the feedback path that maintain consistent division ratios and minimize jitter accumulation. Advanced divider architectures employ techniques such as dual-modulus division, programmable division ratios, and low-jitter circuit topologies. These designs ensure that the feedback signal accurately represents the output frequency while minimizing noise contribution to the loop dynamics.

- Compensation circuits and adaptive control mechanisms: Phase-locked loop stability can be maintained through compensation circuits and adaptive control mechanisms that respond to changing operating conditions. These include automatic gain control circuits, temperature compensation networks, and adaptive loop bandwidth adjustment systems. Such mechanisms monitor loop performance parameters and dynamically adjust circuit characteristics to maintain optimal stability margins, lock time, and phase noise performance across varying conditions.

02 Loop filter optimization and bandwidth control

Stability in phase-locked loops can be achieved through careful design of loop filters that control the bandwidth and damping characteristics of the feedback system. Proper filter design ensures adequate phase margin and prevents oscillations or instability in the locked state. Techniques include multi-order filter implementations, adaptive bandwidth adjustment, and compensation networks that optimize transient response while maintaining lock stability across different operating frequencies.Expand Specific Solutions03 Charge pump and phase detector improvements

Enhanced charge pump circuits and phase detector designs contribute significantly to phase-locked loop stability by reducing dead zones, minimizing current mismatch, and improving linearity. Advanced architectures employ differential structures, current calibration techniques, and symmetrical switching to reduce spurious signals and phase errors. These improvements result in reduced jitter, faster lock times, and more stable operation across the entire frequency range.Expand Specific Solutions04 Frequency divider and feedback path optimization

Stability enhancement through optimized frequency divider designs in the feedback path ensures accurate phase comparison and reduces noise contribution to the loop. High-speed divider architectures with low propagation delay, reduced power consumption, and minimal phase noise are employed. Techniques include dual-modulus prescalers, programmable division ratios, and synchronization circuits that maintain stable operation during frequency transitions and mode changes.Expand Specific Solutions05 Digital control and adaptive stabilization techniques

Modern phase-locked loop designs incorporate digital control mechanisms and adaptive algorithms to enhance stability under varying conditions. Digital implementations allow for programmable loop parameters, automatic gain control, and real-time compensation for process, voltage, and temperature variations. These systems employ calibration routines, lock detection circuits, and dynamic adjustment of loop characteristics to maintain optimal stability across different operating modes and environmental conditions.Expand Specific Solutions

Key Players in PLL and Oscillator Industry

The phase-locked loop oscillator stability market represents a mature yet evolving sector within the broader semiconductor and communications industry. The market demonstrates significant scale, driven by increasing demand across telecommunications, automotive, and IoT applications. Key players exhibit varying levels of technological maturity, with established semiconductor giants like Analog Devices, Texas Instruments, and Intel leading in advanced PLL design and manufacturing capabilities. Asian manufacturers including Samsung Electronics, Huawei Technologies, and SMIC demonstrate strong foundry and integration expertise, while specialized firms like Infineon Technologies and NXP focus on automotive and industrial applications. The competitive landscape shows consolidation around companies with comprehensive RF and mixed-signal portfolios, indicating the industry's progression toward integrated solutions that combine PLL stability with broader system-level performance optimization for next-generation wireless and computing platforms.

Analog Devices, Inc.

Technical Solution: Analog Devices provides comprehensive PLL solutions including the ADF4xxx series and HMC7xxx series PLLs designed for high-frequency applications. Their approach focuses on integrated fractional-N PLLs with low phase noise performance, typically achieving phase noise levels below -110 dBc/Hz at 10 kHz offset. The company implements advanced charge pump architectures and loop filter designs to minimize reference spurs and optimize settling time. Their PLLs feature programmable output dividers, integrated VCOs with wide tuning ranges, and sophisticated phase-frequency detectors that enable precise frequency synthesis across multiple octaves. The stability is enhanced through temperature compensation circuits and adaptive bandwidth control mechanisms.

Strengths: Industry-leading phase noise performance and comprehensive integration. Weaknesses: Higher cost compared to discrete solutions and complex programming requirements.

Intel Corp.

Technical Solution: Intel's PLL technology focuses on high-speed digital applications and processor clock generation, utilizing advanced CMOS processes for integration. Their approach emphasizes all-digital PLLs (ADPLLs) that replace traditional analog components with digital equivalents, providing better process scalability and reduced area. Intel implements sophisticated clock distribution networks with multiple PLL stages to maintain signal integrity across large die areas. Their PLL designs incorporate adaptive jitter cancellation, dynamic frequency scaling capabilities, and advanced phase interpolation techniques. The stability is achieved through digital loop filters with programmable coefficients and real-time monitoring systems that can detect and correct for process, voltage, and temperature variations.

Strengths: Excellent integration with digital systems and advanced process technology. Weaknesses: Primarily optimized for digital applications rather than analog RF performance.

Core Patents in PLL Stability Control Methods

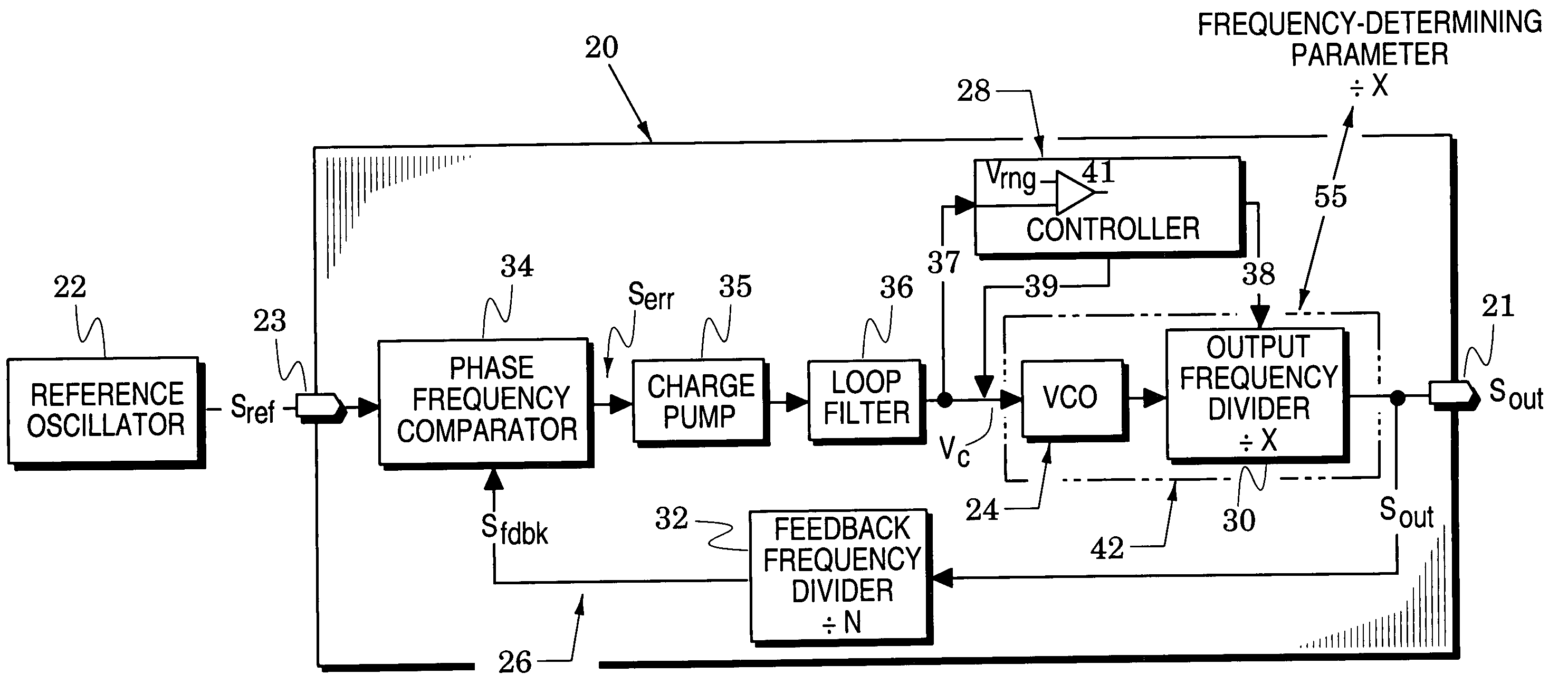

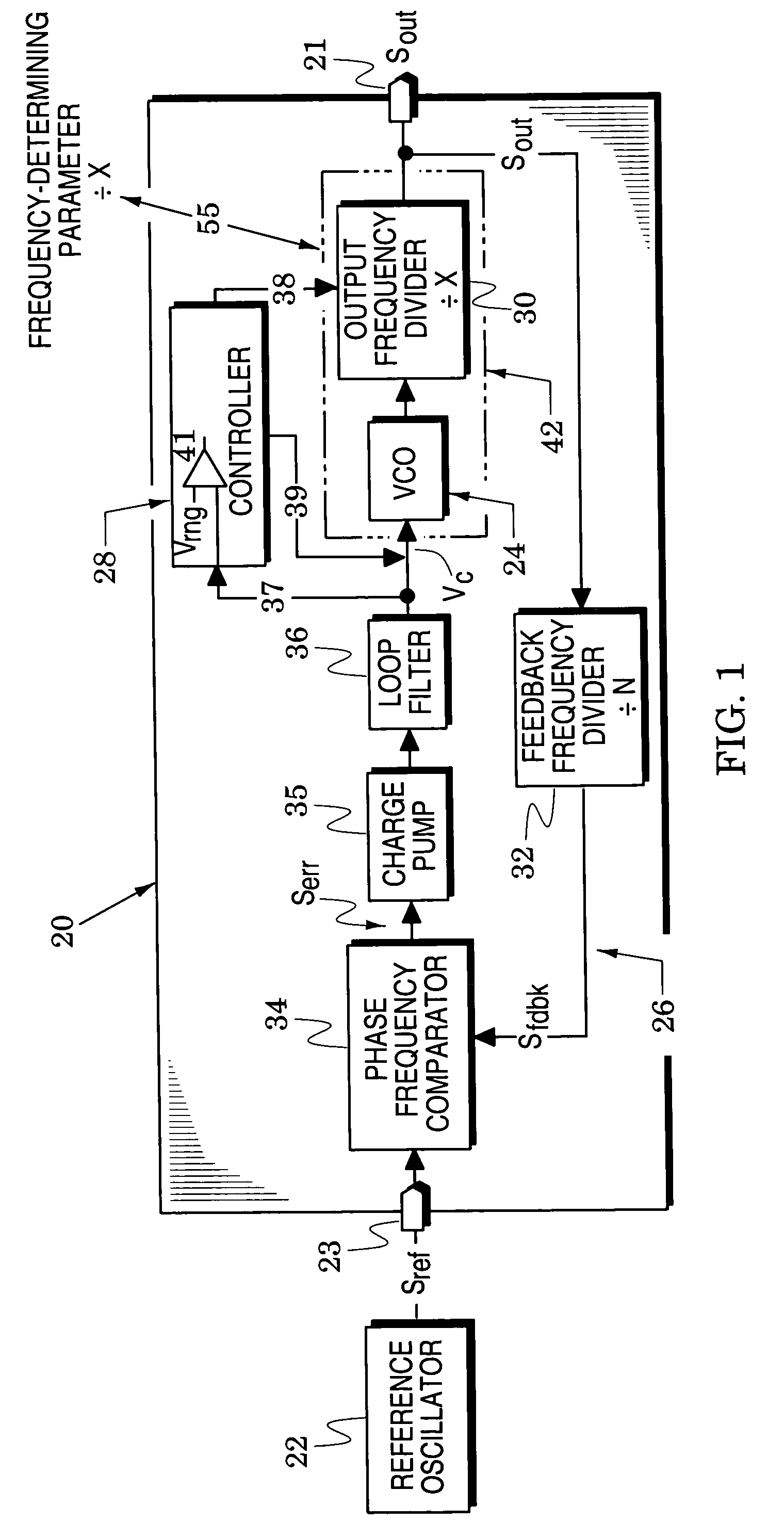

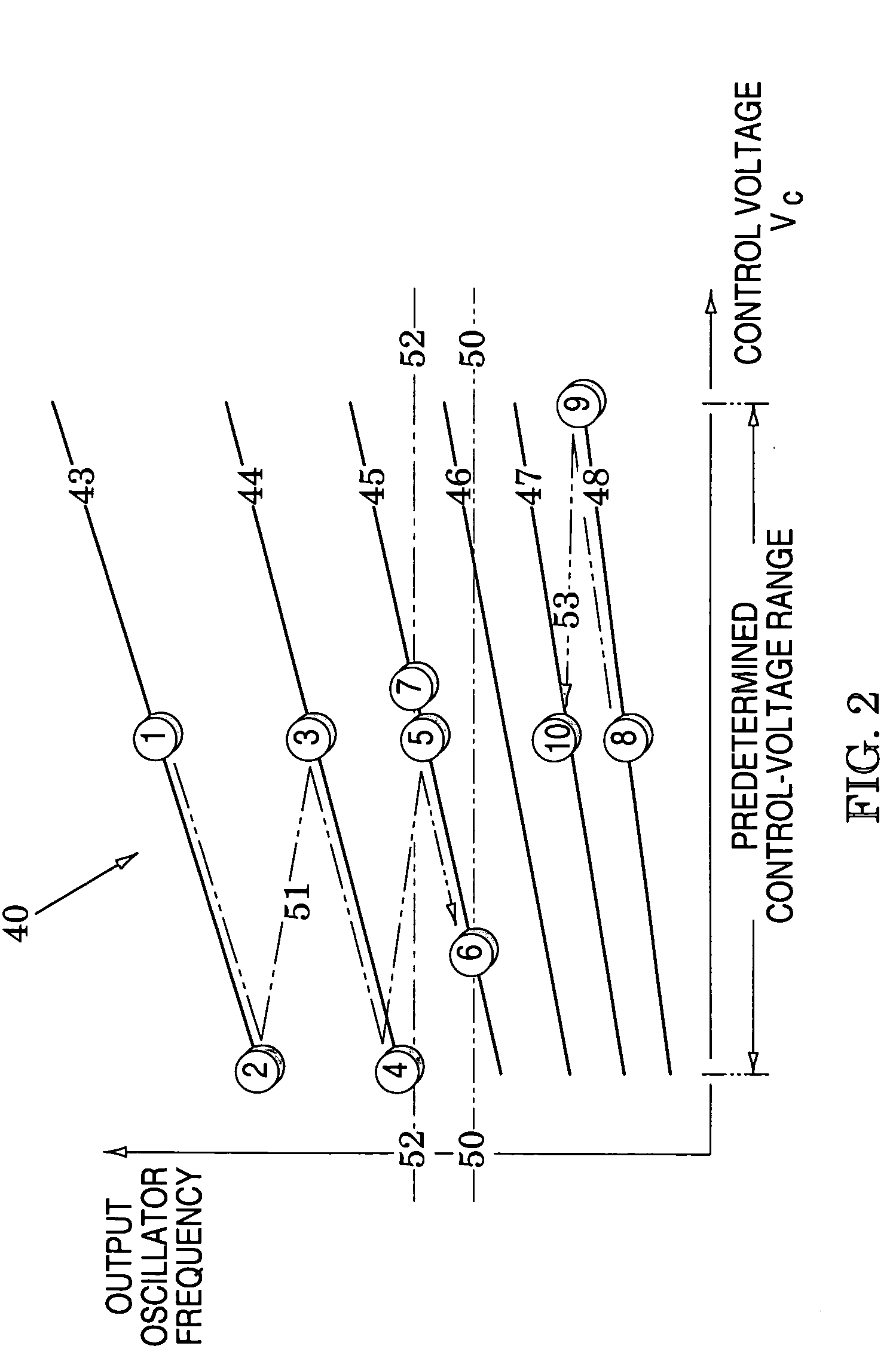

Phase-locked loop structures with enhanced signal stability

PatentInactiveUS20050105661A1

Innovation

- The use of low-gain oscillator structures with a feedback loop and controller that maintains the control voltage within a predetermined range by incrementing a frequency-determining parameter, allowing the phase-locked loop to operate in a closed-loop condition and reduce jitter noise.

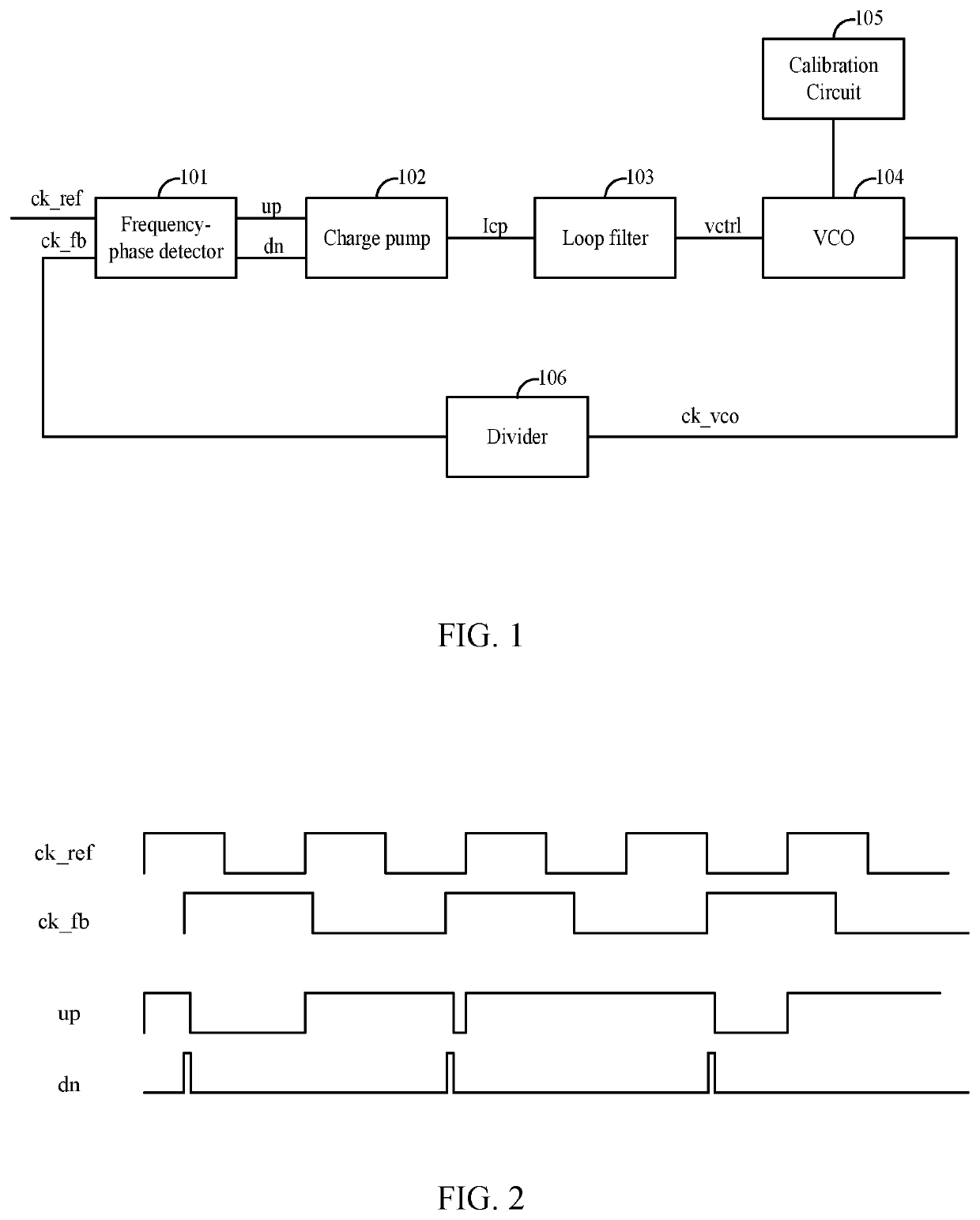

Phase-locked loop and method for calibrating voltage-controlled oscillator therein

PatentActiveUS20200403623A1

Innovation

- A phase-locked loop system comprising a frequency-phase detector, charge pump, loop filter, VCO, divider, and calibration circuit that generates pulse modulation signals, outputs current pulses, performs low-pass filtering, and adjusts frequency, amplitude, and gain control parameters to maintain constant output signal amplitude and gain across a wide frequency range.

EMC Standards for PLL Oscillator Systems

Electromagnetic compatibility standards for phase-locked loop oscillator systems establish critical requirements to ensure stable operation while minimizing interference with other electronic devices. These standards address both conducted and radiated emissions, as well as immunity requirements that directly impact PLL stability performance. The primary applicable standards include CISPR 22/32 for information technology equipment, FCC Part 15 for unintentional radiators, and IEC 61000 series for general EMC requirements.

Conducted emission limits are particularly crucial for PLL systems, as switching noise from the phase detector and charge pump can propagate through power supply lines. Standards typically specify limits from 150 kHz to 30 MHz for conducted emissions, with stricter requirements for Class B equipment intended for residential use. PLL designers must implement proper filtering and decoupling strategies to meet these requirements without compromising loop stability or response time.

Radiated emission standards focus on frequencies above 30 MHz, where PLL harmonics and spurious signals can cause significant interference. The reference oscillator frequency and its harmonics often fall within regulated bands, requiring careful PCB layout, shielding, and component selection. Standards specify measurement distances of 3 or 10 meters with corresponding limit adjustments, influencing the acceptable emission levels from PLL circuits.

Immunity requirements under IEC 61000-4 series ensure PLL systems maintain stable operation under various electromagnetic disturbances. Critical tests include conducted immunity (IEC 61000-4-6), radiated immunity (IEC 61000-4-3), and electrical fast transient immunity (IEC 61000-4-4). These standards define performance criteria where PLL systems must maintain frequency accuracy and phase noise specifications during and after exposure to specified interference levels.

Compliance verification requires specialized test procedures including pre-compliance screening, accredited laboratory testing, and documentation of design margins. The standards mandate specific test configurations, measurement bandwidths, and averaging methods that can reveal PLL stability issues not apparent during normal operation, making EMC compliance an integral part of the stability optimization process.

Conducted emission limits are particularly crucial for PLL systems, as switching noise from the phase detector and charge pump can propagate through power supply lines. Standards typically specify limits from 150 kHz to 30 MHz for conducted emissions, with stricter requirements for Class B equipment intended for residential use. PLL designers must implement proper filtering and decoupling strategies to meet these requirements without compromising loop stability or response time.

Radiated emission standards focus on frequencies above 30 MHz, where PLL harmonics and spurious signals can cause significant interference. The reference oscillator frequency and its harmonics often fall within regulated bands, requiring careful PCB layout, shielding, and component selection. Standards specify measurement distances of 3 or 10 meters with corresponding limit adjustments, influencing the acceptable emission levels from PLL circuits.

Immunity requirements under IEC 61000-4 series ensure PLL systems maintain stable operation under various electromagnetic disturbances. Critical tests include conducted immunity (IEC 61000-4-6), radiated immunity (IEC 61000-4-3), and electrical fast transient immunity (IEC 61000-4-4). These standards define performance criteria where PLL systems must maintain frequency accuracy and phase noise specifications during and after exposure to specified interference levels.

Compliance verification requires specialized test procedures including pre-compliance screening, accredited laboratory testing, and documentation of design margins. The standards mandate specific test configurations, measurement bandwidths, and averaging methods that can reveal PLL stability issues not apparent during normal operation, making EMC compliance an integral part of the stability optimization process.

Thermal Management in High-Stability PLL Design

Thermal management represents one of the most critical aspects in achieving high-stability phase-locked loop oscillator performance. Temperature variations directly impact the frequency stability of PLL circuits through multiple mechanisms, including changes in component values, crystal oscillator drift, and semiconductor junction characteristics. Effective thermal control strategies are essential for maintaining phase noise performance and long-term frequency accuracy in precision applications.

The primary thermal challenge in PLL design stems from the temperature coefficient of frequency (TCF) exhibited by reference oscillators and voltage-controlled oscillators. Crystal oscillators, commonly used as reference sources, demonstrate parabolic frequency-temperature characteristics with turning points typically occurring between 20°C to 30°C. Even high-quality temperature-compensated crystal oscillators (TCXOs) exhibit frequency variations of 0.5 to 2.5 ppm over industrial temperature ranges, which can significantly degrade PLL stability performance.

Active thermal management techniques include the implementation of oven-controlled crystal oscillators (OCXOs) within PLL systems. OCXOs maintain crystal temperature at a constant elevated level, typically 70°C to 85°C, using proportional heating control circuits. This approach can achieve frequency stability better than 0.1 ppm over wide ambient temperature ranges, though at the cost of increased power consumption and longer warm-up times.

Passive thermal management focuses on circuit board design optimization and component placement strategies. Thermal isolation of sensitive components using low thermal conductivity materials, strategic placement of heat-generating elements away from frequency-determining circuits, and implementation of thermal barriers help minimize temperature gradients across the PLL system. Multi-layer PCB designs with dedicated thermal planes provide effective heat spreading while maintaining electrical isolation.

Advanced thermal compensation techniques employ digital temperature sensing and algorithmic correction methods. Modern PLL synthesizers integrate on-chip temperature sensors with digital signal processing capabilities to implement real-time frequency correction algorithms. These systems can characterize individual component temperature responses and apply predictive compensation, achieving stability performance approaching that of OCXOs while maintaining lower power consumption and faster startup characteristics.

The primary thermal challenge in PLL design stems from the temperature coefficient of frequency (TCF) exhibited by reference oscillators and voltage-controlled oscillators. Crystal oscillators, commonly used as reference sources, demonstrate parabolic frequency-temperature characteristics with turning points typically occurring between 20°C to 30°C. Even high-quality temperature-compensated crystal oscillators (TCXOs) exhibit frequency variations of 0.5 to 2.5 ppm over industrial temperature ranges, which can significantly degrade PLL stability performance.

Active thermal management techniques include the implementation of oven-controlled crystal oscillators (OCXOs) within PLL systems. OCXOs maintain crystal temperature at a constant elevated level, typically 70°C to 85°C, using proportional heating control circuits. This approach can achieve frequency stability better than 0.1 ppm over wide ambient temperature ranges, though at the cost of increased power consumption and longer warm-up times.

Passive thermal management focuses on circuit board design optimization and component placement strategies. Thermal isolation of sensitive components using low thermal conductivity materials, strategic placement of heat-generating elements away from frequency-determining circuits, and implementation of thermal barriers help minimize temperature gradients across the PLL system. Multi-layer PCB designs with dedicated thermal planes provide effective heat spreading while maintaining electrical isolation.

Advanced thermal compensation techniques employ digital temperature sensing and algorithmic correction methods. Modern PLL synthesizers integrate on-chip temperature sensors with digital signal processing capabilities to implement real-time frequency correction algorithms. These systems can characterize individual component temperature responses and apply predictive compensation, achieving stability performance approaching that of OCXOs while maintaining lower power consumption and faster startup characteristics.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!