Microcontroller Vs Microprocessor: Architectural Insights

FEB 25, 20268 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Microcontroller vs Microprocessor Evolution and Objectives

The evolution of microcontrollers and microprocessors represents one of the most significant technological developments in modern computing history. Both architectures emerged from the need to create compact, efficient computing solutions, yet they evolved along distinct paths to serve different market segments and application requirements.

Microprocessors originated in the early 1970s with Intel's 4004, designed as a general-purpose computing engine that required external components for memory and input/output operations. This architecture prioritized computational power and flexibility, establishing the foundation for personal computers and high-performance systems. The evolution focused on increasing processing speed, expanding instruction sets, and enhancing parallel processing capabilities.

Microcontrollers emerged slightly later as integrated solutions combining a processor core with memory, timers, and peripheral interfaces on a single chip. The primary objective was to create cost-effective, space-efficient solutions for embedded applications where dedicated functionality mattered more than raw computational power. This integration approach revolutionized embedded system design by reducing component count and system complexity.

The architectural evolution of these technologies has been driven by distinct objectives. Microprocessor development has consistently pursued maximum performance, advanced instruction sets, and sophisticated memory management capabilities. Modern objectives include multi-core architectures, artificial intelligence acceleration, and energy efficiency improvements while maintaining backward compatibility.

Microcontroller evolution has focused on integration density, power efficiency, and real-time performance optimization. Contemporary objectives emphasize ultra-low power consumption for IoT applications, enhanced security features, wireless connectivity integration, and improved analog-digital convergence capabilities.

The convergence trend has become increasingly apparent as both architectures adopt features from each other. High-performance microcontrollers now incorporate advanced processing capabilities, while microprocessors integrate more peripheral functions. This technological convergence aims to address emerging applications requiring both computational power and integration efficiency, particularly in automotive, industrial automation, and smart device markets.

Future objectives center on addressing challenges in edge computing, where the boundary between microcontrollers and microprocessors continues to blur, creating hybrid architectures that combine the best attributes of both approaches.

Microprocessors originated in the early 1970s with Intel's 4004, designed as a general-purpose computing engine that required external components for memory and input/output operations. This architecture prioritized computational power and flexibility, establishing the foundation for personal computers and high-performance systems. The evolution focused on increasing processing speed, expanding instruction sets, and enhancing parallel processing capabilities.

Microcontrollers emerged slightly later as integrated solutions combining a processor core with memory, timers, and peripheral interfaces on a single chip. The primary objective was to create cost-effective, space-efficient solutions for embedded applications where dedicated functionality mattered more than raw computational power. This integration approach revolutionized embedded system design by reducing component count and system complexity.

The architectural evolution of these technologies has been driven by distinct objectives. Microprocessor development has consistently pursued maximum performance, advanced instruction sets, and sophisticated memory management capabilities. Modern objectives include multi-core architectures, artificial intelligence acceleration, and energy efficiency improvements while maintaining backward compatibility.

Microcontroller evolution has focused on integration density, power efficiency, and real-time performance optimization. Contemporary objectives emphasize ultra-low power consumption for IoT applications, enhanced security features, wireless connectivity integration, and improved analog-digital convergence capabilities.

The convergence trend has become increasingly apparent as both architectures adopt features from each other. High-performance microcontrollers now incorporate advanced processing capabilities, while microprocessors integrate more peripheral functions. This technological convergence aims to address emerging applications requiring both computational power and integration efficiency, particularly in automotive, industrial automation, and smart device markets.

Future objectives center on addressing challenges in edge computing, where the boundary between microcontrollers and microprocessors continues to blur, creating hybrid architectures that combine the best attributes of both approaches.

Market Demand for MCU and MPU Solutions

The global semiconductor market demonstrates distinct demand patterns for microcontroller units and microprocessor units, driven by fundamentally different application requirements and market dynamics. MCUs dominate embedded systems markets where integration, power efficiency, and cost-effectiveness are paramount, while MPUs serve computing-intensive applications requiring high performance and flexibility.

IoT and smart device proliferation represents the primary growth driver for MCU demand. Connected home appliances, wearable devices, industrial sensors, and automotive electronics create substantial volume requirements for low-power, integrated solutions. The automotive sector particularly drives premium MCU demand through advanced driver assistance systems, electric vehicle control units, and infotainment systems requiring real-time processing capabilities.

Industrial automation and Industry 4.0 initiatives generate significant demand for both MCU and MPU solutions. Factory automation systems utilize MCUs for sensor nodes and actuator control, while requiring MPUs for edge computing, machine vision, and complex data processing tasks. This dual requirement creates complementary market opportunities across the industrial ecosystem.

Consumer electronics markets exhibit divergent preferences based on device complexity. Simple appliances, toys, and basic electronic devices favor cost-optimized MCUs with integrated peripherals. Conversely, smartphones, tablets, gaming devices, and smart TVs drive MPU demand through requirements for high-performance computing, graphics processing, and multitasking capabilities.

Edge computing emergence creates new market dynamics favoring MPUs in applications traditionally served by cloud processing. Autonomous vehicles, smart city infrastructure, and industrial edge nodes require substantial local processing power, driving demand for high-performance MPU solutions with AI acceleration capabilities.

Geographic demand patterns reflect regional industrial strengths and market maturity. Asian markets lead MCU consumption through electronics manufacturing concentration, while North American and European markets drive premium MPU demand through automotive, aerospace, and industrial applications requiring advanced processing capabilities.

Supply chain considerations increasingly influence demand patterns, with customers seeking diversified sourcing options and regional manufacturing capabilities. This trend particularly affects high-volume MCU applications where supply security and cost predictability are critical factors in vendor selection and long-term planning strategies.

IoT and smart device proliferation represents the primary growth driver for MCU demand. Connected home appliances, wearable devices, industrial sensors, and automotive electronics create substantial volume requirements for low-power, integrated solutions. The automotive sector particularly drives premium MCU demand through advanced driver assistance systems, electric vehicle control units, and infotainment systems requiring real-time processing capabilities.

Industrial automation and Industry 4.0 initiatives generate significant demand for both MCU and MPU solutions. Factory automation systems utilize MCUs for sensor nodes and actuator control, while requiring MPUs for edge computing, machine vision, and complex data processing tasks. This dual requirement creates complementary market opportunities across the industrial ecosystem.

Consumer electronics markets exhibit divergent preferences based on device complexity. Simple appliances, toys, and basic electronic devices favor cost-optimized MCUs with integrated peripherals. Conversely, smartphones, tablets, gaming devices, and smart TVs drive MPU demand through requirements for high-performance computing, graphics processing, and multitasking capabilities.

Edge computing emergence creates new market dynamics favoring MPUs in applications traditionally served by cloud processing. Autonomous vehicles, smart city infrastructure, and industrial edge nodes require substantial local processing power, driving demand for high-performance MPU solutions with AI acceleration capabilities.

Geographic demand patterns reflect regional industrial strengths and market maturity. Asian markets lead MCU consumption through electronics manufacturing concentration, while North American and European markets drive premium MPU demand through automotive, aerospace, and industrial applications requiring advanced processing capabilities.

Supply chain considerations increasingly influence demand patterns, with customers seeking diversified sourcing options and regional manufacturing capabilities. This trend particularly affects high-volume MCU applications where supply security and cost predictability are critical factors in vendor selection and long-term planning strategies.

Current Architectural Landscape and Design Challenges

The contemporary architectural landscape of microcontrollers and microprocessors reflects decades of divergent evolution driven by distinct application requirements and performance objectives. Microcontrollers have evolved toward highly integrated system-on-chip designs that incorporate processing cores, memory subsystems, peripheral interfaces, and specialized functional blocks within single packages. This integration strategy prioritizes power efficiency, cost optimization, and real-time responsiveness for embedded applications.

Microprocessors have pursued a different trajectory, emphasizing raw computational performance through advanced architectural features including multi-core designs, sophisticated cache hierarchies, out-of-order execution engines, and complex instruction sets. Modern microprocessors leverage cutting-edge semiconductor processes to achieve maximum performance density while supporting extensive software ecosystems and operating system compatibility.

Current design challenges in microcontroller architectures center on balancing power consumption with processing capability as Internet of Things applications demand increasingly sophisticated functionality within strict energy budgets. Security integration presents another critical challenge, requiring hardware-based cryptographic accelerators and secure boot mechanisms without significantly impacting cost or power profiles. Memory architecture optimization remains complex, as designers must carefully partition on-chip SRAM, flash storage, and cache resources to meet diverse application requirements.

Microprocessor design faces distinct challenges related to thermal management and power delivery as transistor scaling benefits diminish. The breakdown of Dennard scaling forces architects to explore heterogeneous computing approaches, integrating specialized processing units for artificial intelligence, graphics, and signal processing workloads. Memory wall issues persist as the performance gap between processors and main memory continues widening, driving innovations in cache design and memory hierarchy optimization.

Manufacturing constraints increasingly influence both domains as advanced process nodes become more expensive and complex. Design teams must navigate trade-offs between performance gains and manufacturing costs while ensuring adequate yield rates. Verification complexity has grown exponentially, requiring sophisticated validation methodologies to ensure functional correctness across diverse operating conditions and use cases.

The convergence of edge computing requirements is blurring traditional boundaries between microcontroller and microprocessor domains. Applications now demand microcontroller-like power efficiency combined with microprocessor-level computational capabilities, challenging conventional architectural assumptions and driving exploration of hybrid design approaches that incorporate elements from both paradigms.

Microprocessors have pursued a different trajectory, emphasizing raw computational performance through advanced architectural features including multi-core designs, sophisticated cache hierarchies, out-of-order execution engines, and complex instruction sets. Modern microprocessors leverage cutting-edge semiconductor processes to achieve maximum performance density while supporting extensive software ecosystems and operating system compatibility.

Current design challenges in microcontroller architectures center on balancing power consumption with processing capability as Internet of Things applications demand increasingly sophisticated functionality within strict energy budgets. Security integration presents another critical challenge, requiring hardware-based cryptographic accelerators and secure boot mechanisms without significantly impacting cost or power profiles. Memory architecture optimization remains complex, as designers must carefully partition on-chip SRAM, flash storage, and cache resources to meet diverse application requirements.

Microprocessor design faces distinct challenges related to thermal management and power delivery as transistor scaling benefits diminish. The breakdown of Dennard scaling forces architects to explore heterogeneous computing approaches, integrating specialized processing units for artificial intelligence, graphics, and signal processing workloads. Memory wall issues persist as the performance gap between processors and main memory continues widening, driving innovations in cache design and memory hierarchy optimization.

Manufacturing constraints increasingly influence both domains as advanced process nodes become more expensive and complex. Design teams must navigate trade-offs between performance gains and manufacturing costs while ensuring adequate yield rates. Verification complexity has grown exponentially, requiring sophisticated validation methodologies to ensure functional correctness across diverse operating conditions and use cases.

The convergence of edge computing requirements is blurring traditional boundaries between microcontroller and microprocessor domains. Applications now demand microcontroller-like power efficiency combined with microprocessor-level computational capabilities, challenging conventional architectural assumptions and driving exploration of hybrid design approaches that incorporate elements from both paradigms.

Contemporary Architectural Design Approaches

01 Instruction set architecture and execution units

Microcontrollers and microprocessors feature distinct instruction set architectures that define how instructions are decoded and executed. The architecture includes specialized execution units for arithmetic, logic, and data processing operations. Different architectural designs optimize for specific performance characteristics, power consumption, and application requirements. The instruction pipeline and execution flow are fundamental characteristics that distinguish various processor architectures.- Instruction set architecture and execution units: Microcontrollers and microprocessors feature distinct instruction set architectures that define how instructions are decoded and executed. The architecture includes specialized execution units for arithmetic, logic, and data processing operations. Different architectural designs optimize for specific performance characteristics, power consumption, and application requirements. The instruction pipeline and execution flow are fundamental characteristics that differentiate various processor architectures.

- Memory hierarchy and cache organization: The memory architecture encompasses multiple levels of cache memory, including instruction and data caches, to improve processing speed and reduce latency. Memory management units handle address translation and memory protection. The organization of on-chip memory, external memory interfaces, and memory access patterns are critical architectural features. Different cache coherency protocols and memory bandwidth optimization techniques characterize various processor designs.

- Parallel processing and multi-core architectures: Modern processor architectures incorporate multiple processing cores and parallel execution capabilities to enhance computational throughput. The design includes mechanisms for task distribution, inter-core communication, and synchronization. Architectural features support simultaneous multi-threading and parallel instruction execution. Various interconnect topologies and resource sharing strategies define the multi-core architecture characteristics.

- Power management and clock distribution: Processor architectures integrate sophisticated power management features including dynamic voltage and frequency scaling, clock gating, and power domain isolation. The clock distribution network ensures synchronized operation across different functional units. Architectural elements support various low-power modes and energy-efficient operation states. Thermal management and power optimization techniques are embedded within the architectural design.

- Input/output interfaces and peripheral integration: The architectural design includes various input/output interfaces and peripheral controllers integrated within the processor. Communication protocols, interrupt handling mechanisms, and direct memory access controllers are key architectural components. The design supports multiple interface standards for external device connectivity and data transfer. Peripheral integration strategies and bus architectures define the system-level characteristics of microcontrollers and microprocessors.

02 Memory hierarchy and cache organization

The memory architecture encompasses multiple levels of cache memory, on-chip RAM, and external memory interfaces. Cache organization strategies include different associativity levels, replacement policies, and coherency protocols. Memory management units handle address translation and protection mechanisms. The memory subsystem design significantly impacts overall system performance and power efficiency.Expand Specific Solutions03 Peripheral integration and I/O interfaces

Microcontroller architectures integrate various peripheral modules and input/output interfaces directly on the chip. These include communication interfaces, timers, analog-to-digital converters, and specialized controllers. The peripheral architecture defines how these modules interact with the processor core and memory system. Integration strategies balance functionality, silicon area, and power consumption requirements.Expand Specific Solutions04 Power management and clock distribution

Architectural features for power management include multiple power domains, dynamic voltage and frequency scaling, and low-power operating modes. Clock distribution networks provide synchronized timing signals across different functional blocks. Power gating and clock gating techniques reduce energy consumption during idle periods. The power architecture enables efficient operation across varying workload conditions.Expand Specific Solutions05 Security features and isolation mechanisms

Modern processor architectures incorporate security features including secure boot, memory protection units, and cryptographic accelerators. Isolation mechanisms separate trusted and untrusted execution environments through hardware-enforced boundaries. Security architectures implement access control policies and protect sensitive data from unauthorized access. These features address growing requirements for secure embedded systems and computing platforms.Expand Specific Solutions

Leading MCU and MPU Manufacturers Analysis

The microcontroller versus microprocessor landscape represents a mature yet evolving semiconductor sector experiencing steady growth driven by IoT expansion and embedded system proliferation. The market demonstrates strong segmentation with established players like Intel and AMD dominating high-performance microprocessor segments, while specialized companies such as Microchip Technology, Atmel, and STMicroelectronics lead microcontroller markets. Technology maturity varies significantly across applications - traditional 8-bit and 16-bit microcontrollers from companies like Microchip and Cypress represent highly mature technologies, whereas advanced multi-core processors from Intel and emerging players like Feiteng showcase cutting-edge architectural innovations. The competitive dynamics reflect increasing convergence between traditionally separate domains, with companies like Infineon and Bosch driving automotive integration, while Google's entry signals growing importance of AI-optimized processing architectures in embedded applications.

Intel Corp.

Technical Solution: Intel develops both microprocessors and microcontrollers with distinct architectural approaches. Their microprocessors feature complex instruction set computing (CISC) architecture with sophisticated pipeline designs, multiple execution units, and advanced branch prediction mechanisms. The x86 architecture supports extensive instruction sets and virtual memory management. For microcontrollers, Intel offers 8051-based and newer 32-bit solutions with integrated peripherals, on-chip memory, and real-time processing capabilities. Their architectural design emphasizes power efficiency in embedded applications while maintaining computational performance for specific control tasks.

Strengths: Industry-leading processor architecture, extensive ecosystem support, advanced manufacturing processes. Weaknesses: Higher power consumption in embedded applications, complex architecture may be overkill for simple control tasks.

Microchip Technology, Inc.

Technical Solution: Microchip specializes in microcontroller architectures with their PIC and AVR families, featuring Harvard architecture that separates program and data memory spaces for enhanced performance. Their 8-bit, 16-bit, and 32-bit microcontrollers integrate comprehensive peripheral sets including ADCs, timers, communication interfaces, and motor control units on single chips. The architecture emphasizes low power consumption through multiple sleep modes, efficient instruction execution, and optimized silicon design. Their RISC-based instruction sets enable predictable timing and simplified programming models, making them ideal for real-time embedded applications requiring deterministic behavior.

Strengths: Excellent power efficiency, comprehensive development tools, strong real-time performance, cost-effective solutions. Weaknesses: Limited computational power for complex algorithms, smaller ecosystem compared to general-purpose processors.

Core Architectural Innovations and Patent Insights

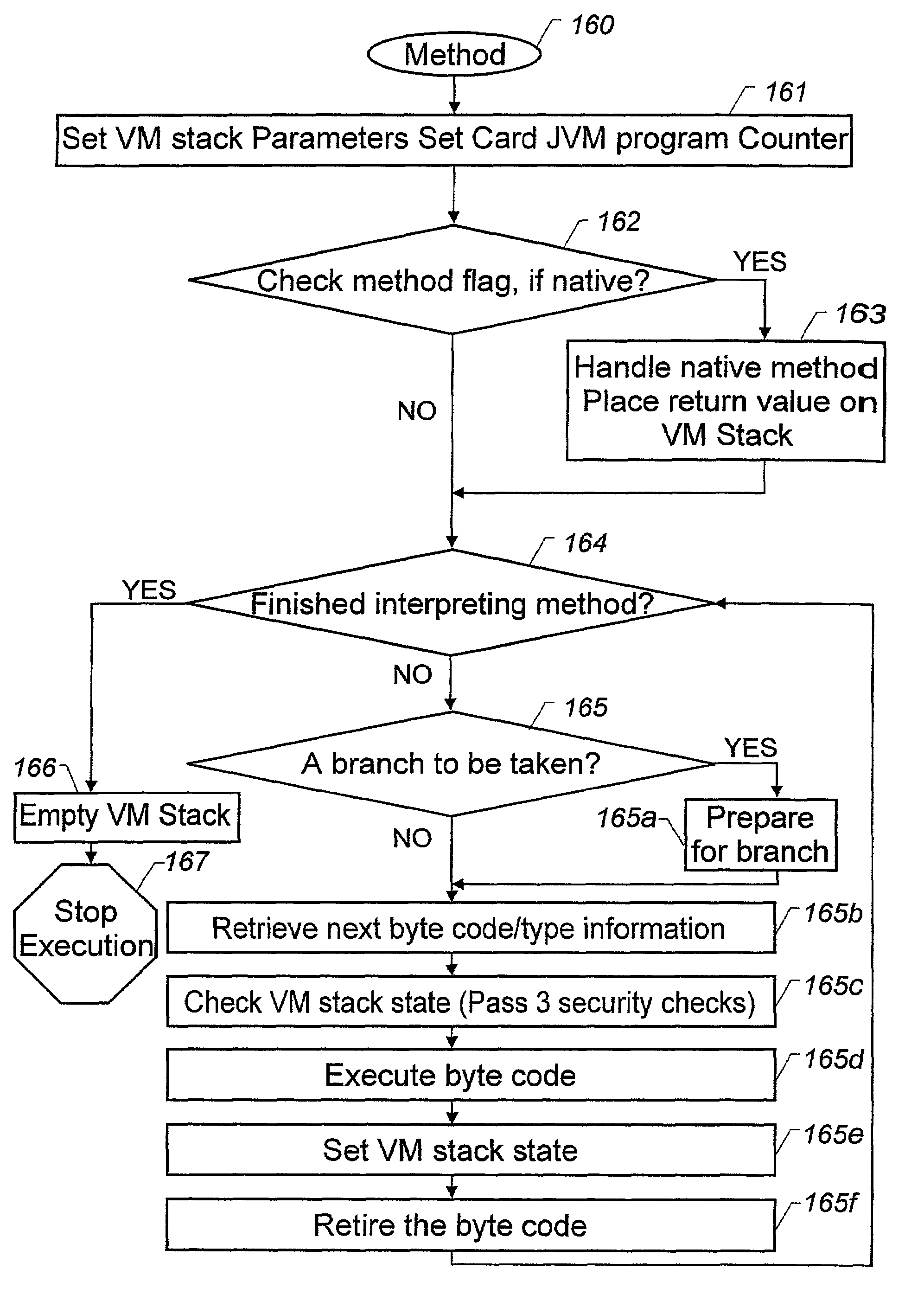

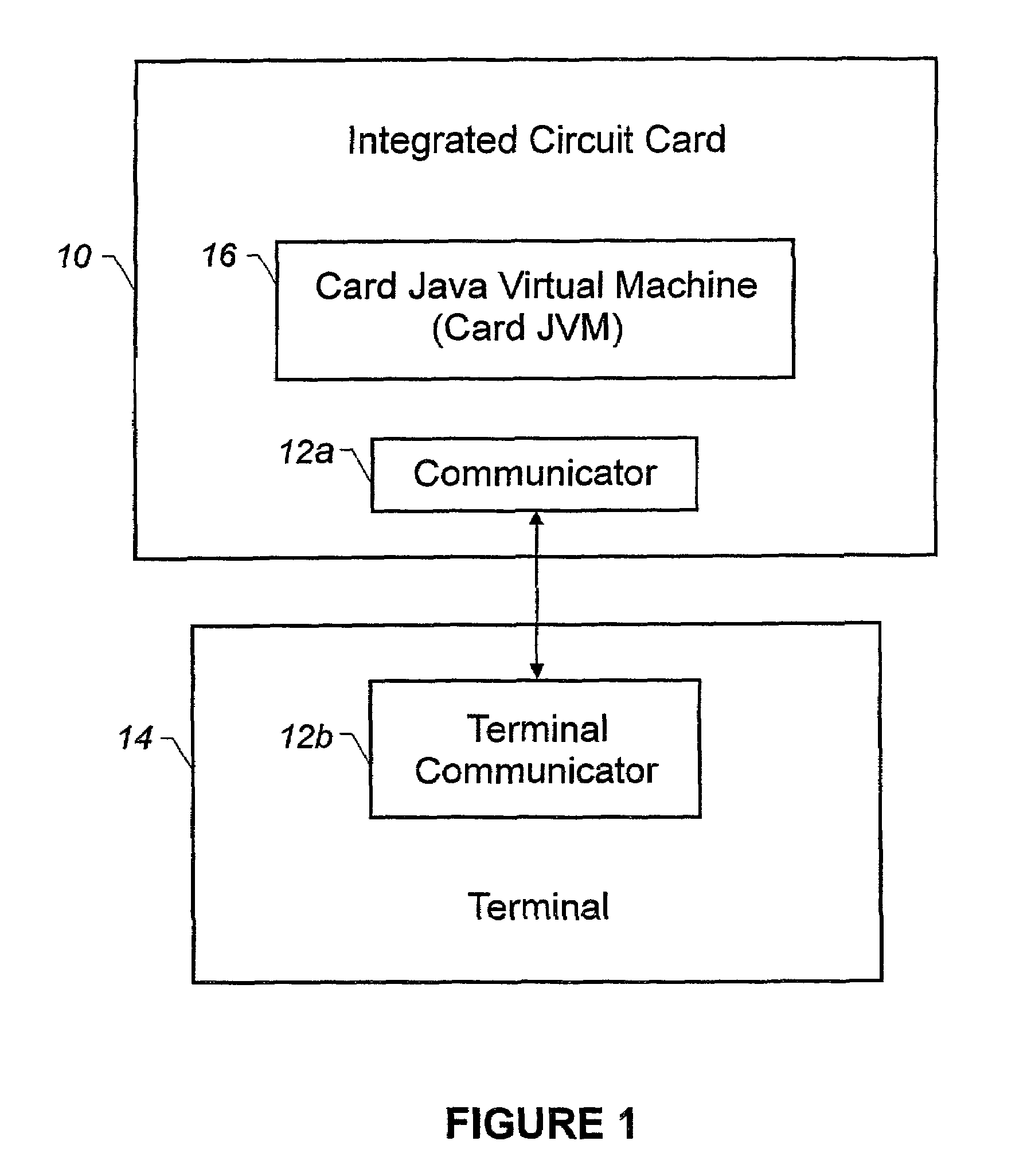

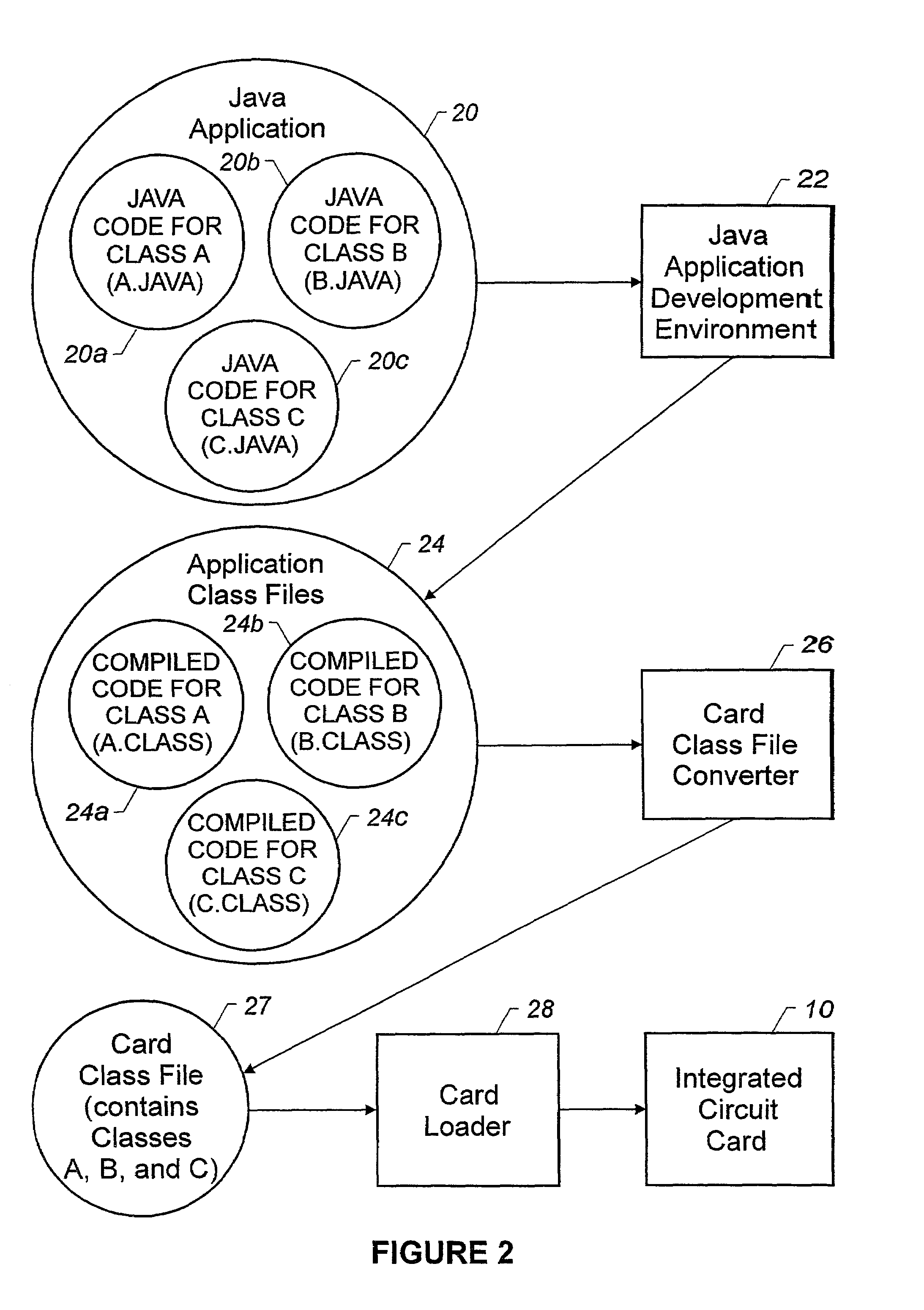

Using a high level programming language with a microcontroller

PatentInactiveUS7117485B2

Innovation

- Implementing a smart card with a Java-based high-level programming language environment, including a Java interpreter and communicator, allowing for secure execution and communication of applications across different terminals without the need for explicit provider knowledge, using a Card Java Virtual Machine (Card JVM) that interprets Java applications and enforces security checks.

Microcontroller or microprocessor with dual mode interrupt

PatentActiveEP3265921A1

Innovation

- A microcontroller with a central processing unit and an interrupt controller that operates in dual modes, allowing for enhanced interrupt handling by forwarding interrupt signals and additional information to generate vector addresses, enabling more flexible interrupt management and supporting a wider range of peripherals without the need for additional hardware.

Power Efficiency Standards and Performance Benchmarks

Power efficiency has become a critical differentiator between microcontrollers and microprocessors, with established industry standards providing frameworks for evaluation. The IEEE 1621 standard defines power measurement methodologies for computing devices, while ENERGY STAR specifications set efficiency thresholds for various electronic systems. These standards emphasize different metrics: microcontrollers typically focus on ultra-low power consumption measured in microamperes during sleep modes, whereas microprocessors prioritize performance-per-watt ratios under varying computational loads.

Performance benchmarking reveals distinct optimization strategies between the two architectures. Microcontrollers excel in power-constrained applications, with modern ARM Cortex-M series achieving operational currents as low as 100 microamperes per MHz. Industry benchmarks like EEMBC's ULPMark evaluate energy efficiency across typical embedded workloads, where leading microcontrollers demonstrate months of battery operation on single-cell power sources.

Microprocessors, conversely, are evaluated using comprehensive suites like SPEC CPU benchmarks combined with power measurement protocols. Advanced processors implement dynamic voltage and frequency scaling (DVFS), achieving significant efficiency gains through architectural features like heterogeneous computing cores and intelligent power gating. Performance metrics focus on computational throughput per watt, with modern processors delivering substantial processing capabilities while maintaining thermal design power (TDP) constraints.

The emergence of specialized benchmarks reflects evolving application requirements. IoT-focused standards emphasize standby power consumption and wake-up latency, while edge computing applications demand balanced performance-efficiency metrics. Machine learning workloads have introduced new benchmarking paradigms, measuring inference operations per joule across different precision levels.

Contemporary evaluation frameworks increasingly incorporate real-world usage patterns rather than synthetic workloads. This shift acknowledges that optimal efficiency depends heavily on application-specific duty cycles, communication protocols, and environmental factors. Advanced power profiling tools now provide granular analysis of power consumption across different operational states, enabling more accurate efficiency assessments for both microcontroller and microprocessor implementations in their respective target applications.

Performance benchmarking reveals distinct optimization strategies between the two architectures. Microcontrollers excel in power-constrained applications, with modern ARM Cortex-M series achieving operational currents as low as 100 microamperes per MHz. Industry benchmarks like EEMBC's ULPMark evaluate energy efficiency across typical embedded workloads, where leading microcontrollers demonstrate months of battery operation on single-cell power sources.

Microprocessors, conversely, are evaluated using comprehensive suites like SPEC CPU benchmarks combined with power measurement protocols. Advanced processors implement dynamic voltage and frequency scaling (DVFS), achieving significant efficiency gains through architectural features like heterogeneous computing cores and intelligent power gating. Performance metrics focus on computational throughput per watt, with modern processors delivering substantial processing capabilities while maintaining thermal design power (TDP) constraints.

The emergence of specialized benchmarks reflects evolving application requirements. IoT-focused standards emphasize standby power consumption and wake-up latency, while edge computing applications demand balanced performance-efficiency metrics. Machine learning workloads have introduced new benchmarking paradigms, measuring inference operations per joule across different precision levels.

Contemporary evaluation frameworks increasingly incorporate real-world usage patterns rather than synthetic workloads. This shift acknowledges that optimal efficiency depends heavily on application-specific duty cycles, communication protocols, and environmental factors. Advanced power profiling tools now provide granular analysis of power consumption across different operational states, enabling more accurate efficiency assessments for both microcontroller and microprocessor implementations in their respective target applications.

Edge Computing Integration and IoT Convergence Strategies

The convergence of microcontrollers and microprocessors in edge computing environments represents a fundamental shift in IoT architecture design. Traditional boundaries between these processing units are blurring as edge computing demands increasingly sophisticated local processing capabilities while maintaining the power efficiency and real-time responsiveness characteristic of embedded systems.

Edge computing integration strategies leverage the complementary strengths of both architectural approaches. Microcontrollers excel in sensor data acquisition, real-time control loops, and low-power standby operations, making them ideal for IoT endpoint devices. Meanwhile, microprocessors provide the computational horsepower necessary for complex data preprocessing, machine learning inference, and protocol translation at edge gateways.

Hybrid architectural frameworks are emerging as the dominant convergence strategy. These systems deploy microcontroller-based sensor nodes for data collection and immediate response functions, while utilizing microprocessor-powered edge gateways for aggregation, filtering, and intelligent processing before cloud transmission. This tiered approach optimizes both power consumption and processing capability across the IoT ecosystem.

The integration challenges center on seamless communication protocols and unified development environments. Modern solutions employ standardized interfaces such as SPI, I2C, and CAN for microcontroller-to-microprocessor communication, while software frameworks like FreeRTOS and Linux enable coordinated task scheduling across heterogeneous processing units.

IoT convergence strategies increasingly favor system-on-chip solutions that incorporate both microcontroller and microprocessor elements within single packages. These hybrid architectures enable dynamic workload distribution, where time-critical tasks execute on dedicated microcontroller cores while complex analytics run on application processor units.

Security considerations drive additional convergence requirements, necessitating hardware-based trust anchors and secure boot mechanisms that span both architectural domains. This unified security approach ensures end-to-end protection across the entire edge computing infrastructure, from sensor endpoints to cloud connectivity.

Edge computing integration strategies leverage the complementary strengths of both architectural approaches. Microcontrollers excel in sensor data acquisition, real-time control loops, and low-power standby operations, making them ideal for IoT endpoint devices. Meanwhile, microprocessors provide the computational horsepower necessary for complex data preprocessing, machine learning inference, and protocol translation at edge gateways.

Hybrid architectural frameworks are emerging as the dominant convergence strategy. These systems deploy microcontroller-based sensor nodes for data collection and immediate response functions, while utilizing microprocessor-powered edge gateways for aggregation, filtering, and intelligent processing before cloud transmission. This tiered approach optimizes both power consumption and processing capability across the IoT ecosystem.

The integration challenges center on seamless communication protocols and unified development environments. Modern solutions employ standardized interfaces such as SPI, I2C, and CAN for microcontroller-to-microprocessor communication, while software frameworks like FreeRTOS and Linux enable coordinated task scheduling across heterogeneous processing units.

IoT convergence strategies increasingly favor system-on-chip solutions that incorporate both microcontroller and microprocessor elements within single packages. These hybrid architectures enable dynamic workload distribution, where time-critical tasks execute on dedicated microcontroller cores while complex analytics run on application processor units.

Security considerations drive additional convergence requirements, necessitating hardware-based trust anchors and secure boot mechanisms that span both architectural domains. This unified security approach ensures end-to-end protection across the entire edge computing infrastructure, from sensor endpoints to cloud connectivity.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!