Synaptic Transistors in Real-Time Data Systems

APR 17, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Synaptic Transistor Technology Background and Objectives

Synaptic transistors represent a revolutionary paradigm in neuromorphic computing, drawing inspiration from the biological synapses that enable learning and memory formation in the human brain. These devices emerged from the convergence of materials science, neuroscience, and semiconductor technology, addressing the fundamental limitations of traditional von Neumann computing architectures. The concept originated in the early 2000s when researchers began exploring memristive devices that could mimic synaptic plasticity, leading to the development of transistor-based structures capable of emulating neural behavior.

The evolution of synaptic transistors has been driven by the exponential growth in data generation and the increasing demand for real-time processing capabilities. Traditional computing systems face significant bottlenecks when handling massive data streams, particularly in applications requiring immediate response and adaptive learning. The separation of memory and processing units in conventional architectures creates latency issues and energy inefficiencies that become critical in real-time scenarios.

Current technological trends indicate a shift toward edge computing and distributed intelligence, where data processing occurs closer to the source rather than in centralized cloud systems. This paradigm shift necessitates hardware solutions that can perform complex computations with minimal power consumption while maintaining high-speed processing capabilities. Synaptic transistors address these requirements by integrating memory and processing functions within a single device, enabling parallel computation similar to biological neural networks.

The primary objective of synaptic transistor research in real-time data systems is to develop hardware platforms capable of instantaneous pattern recognition, adaptive filtering, and predictive analytics. These systems aim to process streaming data with microsecond-level latency while continuously learning and adapting to changing input patterns. Key performance targets include achieving synaptic weight updates within nanosecond timeframes, maintaining stable operation across millions of switching cycles, and demonstrating energy consumption levels comparable to biological synapses.

Furthermore, the research seeks to establish scalable fabrication processes that enable the integration of millions of synaptic transistors on a single chip, creating dense neural networks capable of handling complex real-time applications such as autonomous vehicle control, industrial process monitoring, and adaptive communication systems.

The evolution of synaptic transistors has been driven by the exponential growth in data generation and the increasing demand for real-time processing capabilities. Traditional computing systems face significant bottlenecks when handling massive data streams, particularly in applications requiring immediate response and adaptive learning. The separation of memory and processing units in conventional architectures creates latency issues and energy inefficiencies that become critical in real-time scenarios.

Current technological trends indicate a shift toward edge computing and distributed intelligence, where data processing occurs closer to the source rather than in centralized cloud systems. This paradigm shift necessitates hardware solutions that can perform complex computations with minimal power consumption while maintaining high-speed processing capabilities. Synaptic transistors address these requirements by integrating memory and processing functions within a single device, enabling parallel computation similar to biological neural networks.

The primary objective of synaptic transistor research in real-time data systems is to develop hardware platforms capable of instantaneous pattern recognition, adaptive filtering, and predictive analytics. These systems aim to process streaming data with microsecond-level latency while continuously learning and adapting to changing input patterns. Key performance targets include achieving synaptic weight updates within nanosecond timeframes, maintaining stable operation across millions of switching cycles, and demonstrating energy consumption levels comparable to biological synapses.

Furthermore, the research seeks to establish scalable fabrication processes that enable the integration of millions of synaptic transistors on a single chip, creating dense neural networks capable of handling complex real-time applications such as autonomous vehicle control, industrial process monitoring, and adaptive communication systems.

Market Demand for Real-Time Neuromorphic Computing Systems

The global demand for real-time neuromorphic computing systems is experiencing unprecedented growth, driven by the exponential increase in data generation and the limitations of traditional von Neumann architectures in handling complex, time-sensitive computational tasks. Industries across sectors are recognizing the critical need for computing paradigms that can process information with the speed, efficiency, and adaptability of biological neural networks.

Edge computing applications represent one of the most significant demand drivers for neuromorphic systems. As Internet of Things devices proliferate and autonomous systems become more sophisticated, there is an urgent requirement for processing units that can make instantaneous decisions without relying on cloud connectivity. Synaptic transistors offer the potential to enable real-time pattern recognition, anomaly detection, and adaptive learning directly at the data source, addressing latency constraints that traditional processors cannot meet.

The automotive industry demonstrates particularly strong demand for neuromorphic computing solutions, especially in autonomous vehicle development. Real-time processing of sensor data from cameras, LiDAR, and radar systems requires computational architectures that can simultaneously handle multiple data streams while making split-second decisions. Current market requirements emphasize systems capable of processing sensory information with minimal power consumption while maintaining high reliability standards.

Healthcare and biomedical applications are emerging as another substantial market segment. Real-time monitoring systems, brain-computer interfaces, and prosthetic control devices require neuromorphic processors that can interpret biological signals and respond with natural timing characteristics. The demand extends to wearable health monitoring devices that need continuous operation with extended battery life.

Financial services sector shows increasing interest in neuromorphic systems for high-frequency trading and real-time fraud detection. The ability to process vast amounts of transactional data instantaneously while identifying complex patterns makes synaptic transistor-based systems attractive for time-critical financial applications.

Industrial automation and robotics markets are driving demand for adaptive control systems that can learn and respond to changing environmental conditions in real-time. Manufacturing processes increasingly require intelligent systems capable of quality control, predictive maintenance, and adaptive optimization without human intervention.

The convergence of artificial intelligence with edge computing is creating new market opportunities where traditional digital processors face fundamental limitations in power efficiency and processing speed, establishing a clear market pull for neuromorphic computing solutions.

Edge computing applications represent one of the most significant demand drivers for neuromorphic systems. As Internet of Things devices proliferate and autonomous systems become more sophisticated, there is an urgent requirement for processing units that can make instantaneous decisions without relying on cloud connectivity. Synaptic transistors offer the potential to enable real-time pattern recognition, anomaly detection, and adaptive learning directly at the data source, addressing latency constraints that traditional processors cannot meet.

The automotive industry demonstrates particularly strong demand for neuromorphic computing solutions, especially in autonomous vehicle development. Real-time processing of sensor data from cameras, LiDAR, and radar systems requires computational architectures that can simultaneously handle multiple data streams while making split-second decisions. Current market requirements emphasize systems capable of processing sensory information with minimal power consumption while maintaining high reliability standards.

Healthcare and biomedical applications are emerging as another substantial market segment. Real-time monitoring systems, brain-computer interfaces, and prosthetic control devices require neuromorphic processors that can interpret biological signals and respond with natural timing characteristics. The demand extends to wearable health monitoring devices that need continuous operation with extended battery life.

Financial services sector shows increasing interest in neuromorphic systems for high-frequency trading and real-time fraud detection. The ability to process vast amounts of transactional data instantaneously while identifying complex patterns makes synaptic transistor-based systems attractive for time-critical financial applications.

Industrial automation and robotics markets are driving demand for adaptive control systems that can learn and respond to changing environmental conditions in real-time. Manufacturing processes increasingly require intelligent systems capable of quality control, predictive maintenance, and adaptive optimization without human intervention.

The convergence of artificial intelligence with edge computing is creating new market opportunities where traditional digital processors face fundamental limitations in power efficiency and processing speed, establishing a clear market pull for neuromorphic computing solutions.

Current State and Challenges of Synaptic Transistor Development

Synaptic transistors represent a revolutionary approach to neuromorphic computing, mimicking the functionality of biological synapses through semiconductor devices. Currently, the field has achieved significant milestones in demonstrating basic synaptic behaviors including potentiation, depression, and spike-timing-dependent plasticity. Leading research institutions have successfully fabricated devices using various materials such as organic semiconductors, metal oxides, and two-dimensional materials like graphene and transition metal dichalcogenides.

The global development landscape shows concentrated efforts in Asia, particularly South Korea, China, and Japan, alongside strong research programs in the United States and Europe. Samsung, TSMC, and Intel have invested heavily in neuromorphic chip development, while academic institutions like Stanford, MIT, and KAIST continue pushing fundamental research boundaries. Current prototypes demonstrate promising characteristics including low power consumption, high integration density, and real-time learning capabilities.

However, several critical challenges impede widespread adoption in real-time data systems. Device variability remains a primary concern, as manufacturing inconsistencies lead to unpredictable synaptic weights and learning behaviors. This variability significantly impacts system reliability and reproducibility, essential requirements for practical applications. Additionally, current synaptic transistors suffer from limited endurance, with device degradation occurring after repeated programming cycles, restricting their operational lifespan.

Scalability presents another major obstacle, as existing fabrication processes struggle to maintain uniform device characteristics across large arrays. The integration of synaptic transistors with conventional CMOS circuits introduces compatibility issues, requiring novel hybrid architectures and specialized interface circuits. Power management also poses challenges, despite theoretical advantages, as current implementations often require complex control circuitry that negates energy efficiency gains.

Speed limitations further constrain real-time applications, with many synaptic transistors exhibiting response times incompatible with high-frequency data processing requirements. Temperature sensitivity and environmental stability issues compound these challenges, as device performance varies significantly under different operating conditions. The lack of standardized characterization methods and performance metrics hampers systematic comparison and optimization efforts across different research groups and technological approaches.

The global development landscape shows concentrated efforts in Asia, particularly South Korea, China, and Japan, alongside strong research programs in the United States and Europe. Samsung, TSMC, and Intel have invested heavily in neuromorphic chip development, while academic institutions like Stanford, MIT, and KAIST continue pushing fundamental research boundaries. Current prototypes demonstrate promising characteristics including low power consumption, high integration density, and real-time learning capabilities.

However, several critical challenges impede widespread adoption in real-time data systems. Device variability remains a primary concern, as manufacturing inconsistencies lead to unpredictable synaptic weights and learning behaviors. This variability significantly impacts system reliability and reproducibility, essential requirements for practical applications. Additionally, current synaptic transistors suffer from limited endurance, with device degradation occurring after repeated programming cycles, restricting their operational lifespan.

Scalability presents another major obstacle, as existing fabrication processes struggle to maintain uniform device characteristics across large arrays. The integration of synaptic transistors with conventional CMOS circuits introduces compatibility issues, requiring novel hybrid architectures and specialized interface circuits. Power management also poses challenges, despite theoretical advantages, as current implementations often require complex control circuitry that negates energy efficiency gains.

Speed limitations further constrain real-time applications, with many synaptic transistors exhibiting response times incompatible with high-frequency data processing requirements. Temperature sensitivity and environmental stability issues compound these challenges, as device performance varies significantly under different operating conditions. The lack of standardized characterization methods and performance metrics hampers systematic comparison and optimization efforts across different research groups and technological approaches.

Current Synaptic Transistor Implementation Solutions

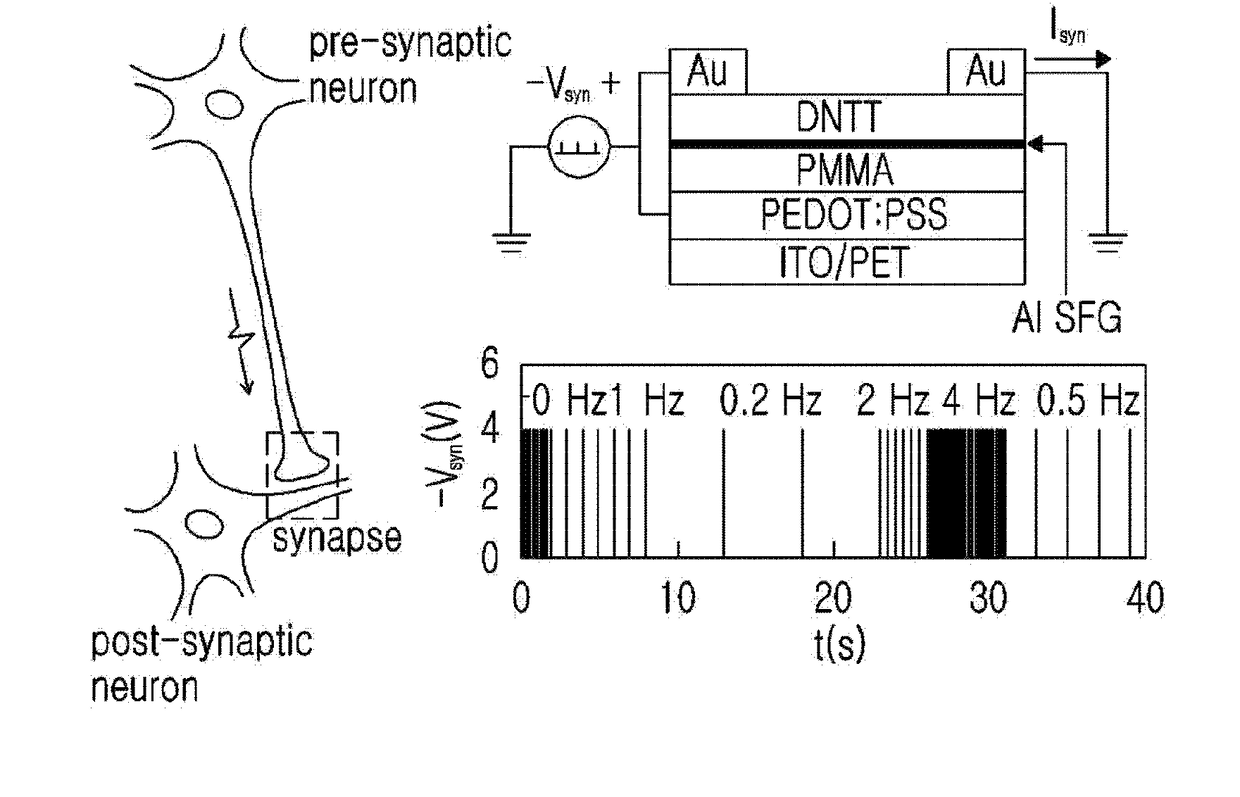

01 Organic semiconductor-based synaptic transistors

Synaptic transistors can be fabricated using organic semiconductor materials to mimic biological synaptic functions. These devices utilize organic thin-film transistor structures with ion-gel or electrolyte gates to achieve synaptic plasticity, including short-term and long-term potentiation and depression. The organic materials provide advantages such as flexibility, low-cost fabrication, and biocompatibility, making them suitable for neuromorphic computing applications.- Organic semiconductor-based synaptic transistors: Synaptic transistors can be fabricated using organic semiconductor materials to mimic biological synaptic functions. These devices utilize organic thin-film transistor structures with ion-gel or electrolyte gates to achieve synaptic plasticity, including short-term and long-term potentiation and depression. The organic materials provide advantages such as flexibility, low-cost fabrication, and biocompatibility, making them suitable for neuromorphic computing applications.

- Oxide-based synaptic transistors with memristive properties: Synaptic transistors incorporating oxide materials exhibit memristive characteristics that enable synaptic weight modulation. These devices utilize metal oxide semiconductors or dielectric layers to create ion migration and trapping mechanisms that modulate channel conductance. The oxide-based approach provides non-volatile memory characteristics, high switching ratios, and compatibility with conventional semiconductor processing technologies for neuromorphic hardware implementation.

- Three-terminal synaptic transistor architectures: Three-terminal synaptic transistor configurations provide independent control of synaptic weight through gate modulation while maintaining separate input and output terminals. These architectures enable more complex synaptic functions including spike-timing-dependent plasticity and multi-level weight states. The three-terminal design allows for better integration density and lower power consumption compared to two-terminal memristive devices in neural network circuits.

- Floating-gate synaptic transistors for analog weight storage: Floating-gate transistor structures enable analog storage of synaptic weights through charge trapping mechanisms. These devices utilize isolated conductive layers within the gate dielectric stack to store charge that modulates the threshold voltage and channel conductance. The floating-gate approach provides multi-level analog states, long retention times, and precise weight tuning capabilities essential for implementing artificial neural networks with high accuracy.

- Two-dimensional material-based synaptic transistors: Synaptic transistors fabricated with two-dimensional materials such as graphene, transition metal dichalcogenides, or other layered materials exhibit unique electronic properties for neuromorphic applications. These atomically thin channel materials provide excellent electrostatic control, high carrier mobility, and tunable electronic properties through material engineering. The two-dimensional material approach enables ultra-low power operation, high switching speeds, and potential for three-dimensional integration in neuromorphic computing systems.

02 Oxide-based synaptic transistors with memristive properties

Synaptic transistors incorporating oxide materials exhibit memristive characteristics that enable neuromorphic functionality. These devices utilize metal oxide semiconductors or dielectric layers to achieve controllable conductance modulation through ion migration or charge trapping mechanisms. The oxide-based structures demonstrate excellent retention, multiple conductance states, and energy-efficient operation for artificial neural network implementations.Expand Specific Solutions03 Three-terminal synaptic transistor architectures

Three-terminal synaptic transistor configurations provide independent control of synaptic weight modulation through gate, source, and drain terminals. These architectures enable decoupled read and write operations, allowing for more precise control of synaptic plasticity. The three-terminal design facilitates implementation of various learning rules and provides better scalability for large-scale neuromorphic systems compared to two-terminal devices.Expand Specific Solutions04 Floating-gate synaptic transistors for non-volatile memory

Floating-gate transistor structures enable non-volatile synaptic weight storage through charge retention in isolated conductive layers. These devices achieve long-term synaptic plasticity by controlling charge injection and removal through tunneling or hot-carrier injection mechanisms. The floating-gate architecture provides multi-level conductance states, low power consumption, and compatibility with standard semiconductor fabrication processes.Expand Specific Solutions05 Two-dimensional material-based synaptic transistors

Synaptic transistors utilizing two-dimensional materials such as graphene, transition metal dichalcogenides, or other layered structures offer unique electronic properties for neuromorphic applications. These materials provide atomic-scale thickness, high carrier mobility, and tunable electronic characteristics. The two-dimensional material-based devices demonstrate excellent synaptic behavior including spike-timing-dependent plasticity and can be integrated into flexible or transparent neuromorphic systems.Expand Specific Solutions

Key Players in Synaptic Transistor and Neuromorphic Industry

The synaptic transistor technology for real-time data systems represents an emerging field at the intersection of neuromorphic computing and advanced memory solutions, currently in early-to-mid development stages. The market shows significant growth potential driven by AI and edge computing demands, though commercial applications remain limited. Technology maturity varies considerably across key players: established semiconductor giants like Samsung Electronics, SK Hynix, Micron Technology, and IBM leverage their manufacturing expertise and R&D capabilities to advance neuromorphic architectures, while companies such as Toshiba, Renesas Electronics, and AMD contribute specialized processor and memory technologies. Academic institutions including KAIST, Peking University, and University of California provide foundational research breakthroughs. Emerging specialists like CrossBar and SunRise Memory focus on novel memory technologies that complement synaptic transistor development, creating a competitive landscape where traditional memory manufacturers compete alongside innovative startups and research institutions to commercialize brain-inspired computing solutions.

Micron Technology, Inc.

Technical Solution: Micron has developed resistive RAM (ReRAM) based synaptic transistors utilizing metal oxide switching layers for neuromorphic applications. Their technology employs tantalum oxide and hafnium oxide materials to create memristive devices that exhibit synaptic plasticity behaviors including spike-timing dependent plasticity (STDP). Micron's synaptic transistors demonstrate sub-100ns switching times and multi-bit storage capabilities with over 64 distinct conductance levels. The company has integrated these devices into crossbar array architectures optimized for real-time inference tasks, achieving throughput rates exceeding 10^15 operations per second per square centimeter while maintaining power efficiency below 10fJ per synaptic operation.

Strengths: High integration density, fast switching speeds, excellent multi-level storage capability. Weaknesses: Variability in switching characteristics, limited temperature stability for some applications.

SK hynix, Inc.

Technical Solution: SK Hynix has developed floating-gate based synaptic transistors that leverage their extensive NAND flash memory expertise for neuromorphic computing applications. Their approach utilizes charge-trap flash (CTF) technology with silicon nitride storage layers to implement analog synaptic weights. The company's synaptic devices support incremental programming and erasing operations that closely mimic biological synaptic potentiation and depression. SK Hynix has demonstrated real-time learning capabilities in their synaptic arrays with programming speeds under 1μs and retention times exceeding 10 years. Their technology shows particular promise for edge AI applications requiring continuous learning and adaptation in real-time data processing scenarios.

Strengths: Leverages mature flash memory technology, excellent retention characteristics, cost-effective manufacturing. Weaknesses: Slower programming speeds compared to emerging technologies, limited precision in analog weight storage.

Core Patents in Synaptic Device Real-Time Processing

Synaptic transistor

PatentActiveUS20220077314A1

Innovation

- A synaptic transistor design is introduced, featuring a substrate with an expansion gate electrode, gate insulating layer with ions, a channel layer, and source and drain electrodes, which allows for the movement of ions or electrons under different biases to adjust synaptic strength and provide both short-term and long-term memory characteristics, enhancing hysteresis and signal-to-noise ratio.

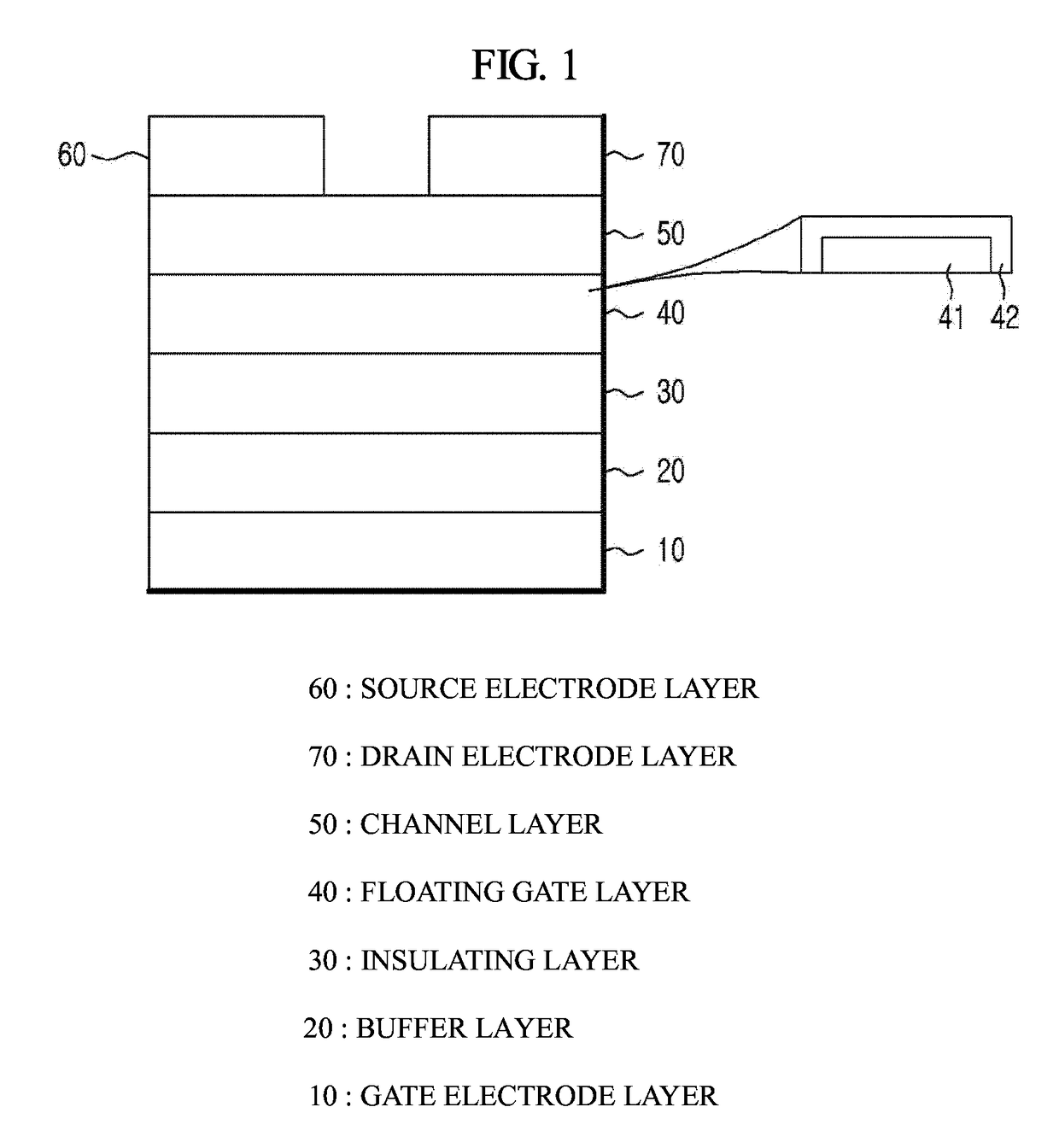

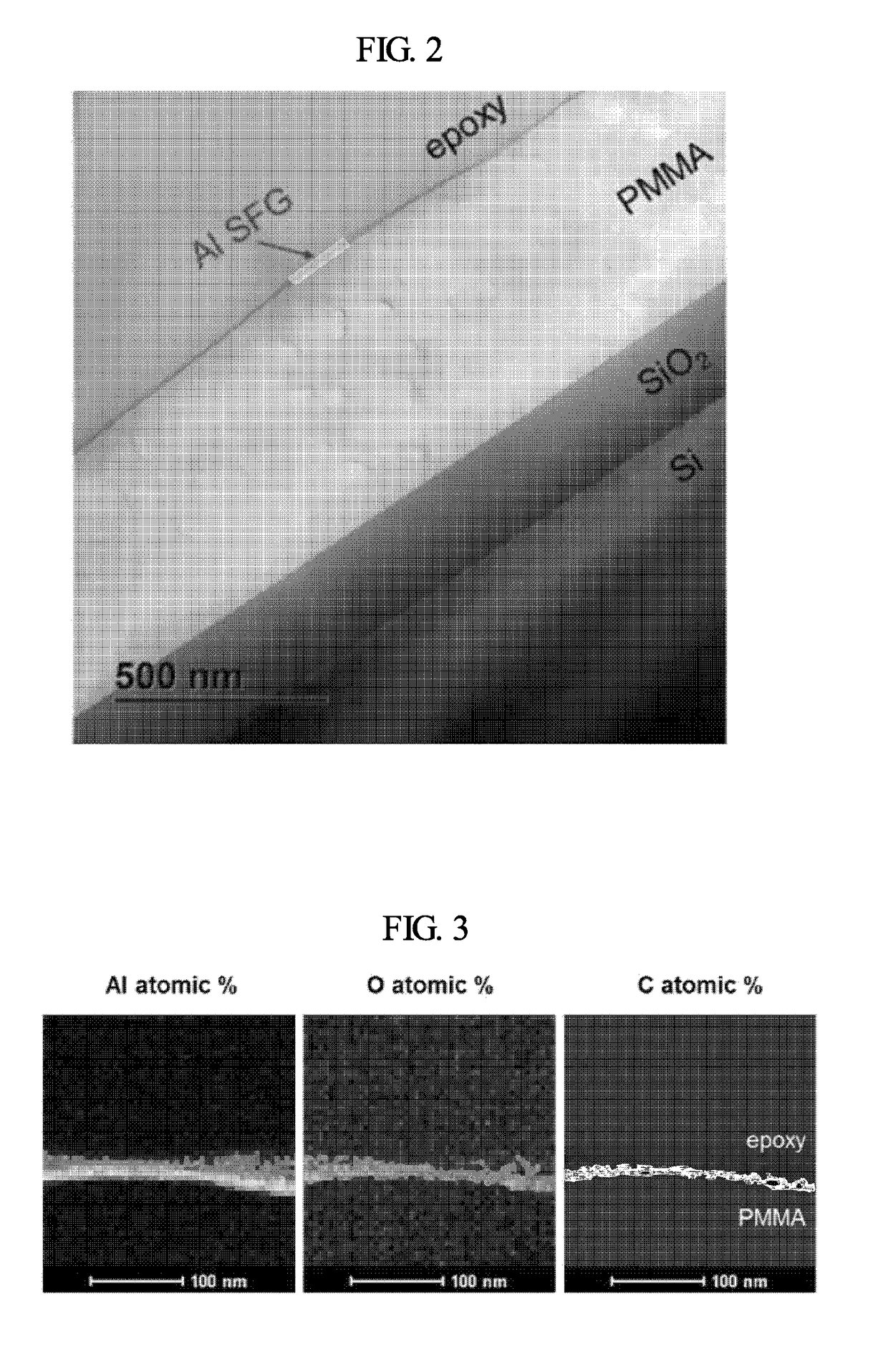

Synaptic transistor based on metal nano-sheet and method of manufacturing the same

PatentActiveUS20180083212A1

Innovation

- A synaptic transistor based on a metal nano-sheet structure, featuring a gate electrode layer, buffer layer, insulating layer, self-assembled floating gate layer, source electrode layer, and drain electrode layer, where the self-assembled floating gate layer includes naturally oxidizing materials like silver, copper, or aluminum, and a metal oxide layer for efficient charge storage and isolation.

Energy Efficiency Standards for Neuromorphic Systems

Energy efficiency has emerged as a critical performance metric for neuromorphic systems implementing synaptic transistors in real-time data processing applications. Current industry standards primarily focus on traditional computing architectures, leaving a significant gap in specialized benchmarks for neuromorphic hardware that operates fundamentally differently from conventional digital systems.

The IEEE 2857 standard represents the most comprehensive framework for neuromorphic system evaluation, establishing baseline metrics for energy consumption per synaptic operation. This standard defines energy efficiency as the ratio of computational throughput to power consumption, measured in operations per joule. For synaptic transistors, the standard specifies measurement protocols that account for both active switching energy and leakage power during idle states.

Emerging standards from the International Technology Roadmap for Semiconductors propose energy efficiency targets of less than 1 femtojoule per synaptic event for next-generation neuromorphic processors. These targets consider the unique operational characteristics of synaptic transistors, including their analog nature and event-driven processing capabilities that differ significantly from traditional CMOS logic.

The Neuromorphic Engineering Consortium has developed supplementary guidelines addressing energy efficiency in real-time applications. These standards emphasize dynamic power management techniques specific to synaptic arrays, including adaptive voltage scaling and selective activation protocols that can reduce overall system power consumption by up to 40% compared to always-on configurations.

Recent standardization efforts focus on establishing unified testing methodologies for comparing energy efficiency across different neuromorphic architectures. The proposed standards include specific protocols for measuring energy consumption during various operational modes, from high-frequency real-time processing to low-power standby states, ensuring comprehensive evaluation of synaptic transistor performance.

Industry adoption of these standards remains in early stages, with major semiconductor manufacturers beginning to incorporate these metrics into their neuromorphic chip specifications. The standardization process continues to evolve as the technology matures and real-world deployment data becomes available.

The IEEE 2857 standard represents the most comprehensive framework for neuromorphic system evaluation, establishing baseline metrics for energy consumption per synaptic operation. This standard defines energy efficiency as the ratio of computational throughput to power consumption, measured in operations per joule. For synaptic transistors, the standard specifies measurement protocols that account for both active switching energy and leakage power during idle states.

Emerging standards from the International Technology Roadmap for Semiconductors propose energy efficiency targets of less than 1 femtojoule per synaptic event for next-generation neuromorphic processors. These targets consider the unique operational characteristics of synaptic transistors, including their analog nature and event-driven processing capabilities that differ significantly from traditional CMOS logic.

The Neuromorphic Engineering Consortium has developed supplementary guidelines addressing energy efficiency in real-time applications. These standards emphasize dynamic power management techniques specific to synaptic arrays, including adaptive voltage scaling and selective activation protocols that can reduce overall system power consumption by up to 40% compared to always-on configurations.

Recent standardization efforts focus on establishing unified testing methodologies for comparing energy efficiency across different neuromorphic architectures. The proposed standards include specific protocols for measuring energy consumption during various operational modes, from high-frequency real-time processing to low-power standby states, ensuring comprehensive evaluation of synaptic transistor performance.

Industry adoption of these standards remains in early stages, with major semiconductor manufacturers beginning to incorporate these metrics into their neuromorphic chip specifications. The standardization process continues to evolve as the technology matures and real-world deployment data becomes available.

Integration Challenges in Real-Time Data Processing

The integration of synaptic transistors into real-time data processing systems presents multifaceted challenges that span hardware architecture, software compatibility, and system-level optimization. These neuromorphic devices, while offering unprecedented computational efficiency for certain tasks, require fundamental rethinking of traditional computing paradigms to achieve seamless integration with existing real-time systems.

Hardware-level integration challenges primarily stem from the analog nature of synaptic transistors operating within predominantly digital infrastructures. The continuous conductance modulation characteristic of these devices necessitates sophisticated analog-to-digital conversion interfaces that can maintain signal integrity while meeting stringent timing requirements. Additionally, the inherent variability in synaptic transistor behavior, including device-to-device variations and temporal drift, poses significant challenges for maintaining consistent performance across large-scale arrays required for practical real-time applications.

System architecture compatibility represents another critical integration hurdle. Traditional real-time systems rely on deterministic processing pipelines with predictable latency characteristics. Synaptic transistors, however, introduce probabilistic computing elements that can enhance pattern recognition and adaptive learning capabilities but may compromise the deterministic behavior essential for hard real-time constraints. This fundamental mismatch requires innovative hybrid architectures that can leverage neuromorphic advantages while preserving critical timing guarantees.

Software integration challenges encompass the development of appropriate programming models and runtime systems capable of efficiently managing synaptic transistor arrays. Existing real-time operating systems lack native support for neuromorphic computing primitives, necessitating the creation of specialized middleware layers that can translate high-level application requirements into low-level synaptic operations while maintaining real-time scheduling constraints.

Power management and thermal considerations further complicate integration efforts. While synaptic transistors offer superior energy efficiency for specific computational tasks, their integration with conventional processing units can create complex power distribution and thermal management challenges that must be carefully addressed to maintain system reliability and performance consistency in real-time environments.

Hardware-level integration challenges primarily stem from the analog nature of synaptic transistors operating within predominantly digital infrastructures. The continuous conductance modulation characteristic of these devices necessitates sophisticated analog-to-digital conversion interfaces that can maintain signal integrity while meeting stringent timing requirements. Additionally, the inherent variability in synaptic transistor behavior, including device-to-device variations and temporal drift, poses significant challenges for maintaining consistent performance across large-scale arrays required for practical real-time applications.

System architecture compatibility represents another critical integration hurdle. Traditional real-time systems rely on deterministic processing pipelines with predictable latency characteristics. Synaptic transistors, however, introduce probabilistic computing elements that can enhance pattern recognition and adaptive learning capabilities but may compromise the deterministic behavior essential for hard real-time constraints. This fundamental mismatch requires innovative hybrid architectures that can leverage neuromorphic advantages while preserving critical timing guarantees.

Software integration challenges encompass the development of appropriate programming models and runtime systems capable of efficiently managing synaptic transistor arrays. Existing real-time operating systems lack native support for neuromorphic computing primitives, necessitating the creation of specialized middleware layers that can translate high-level application requirements into low-level synaptic operations while maintaining real-time scheduling constraints.

Power management and thermal considerations further complicate integration efforts. While synaptic transistors offer superior energy efficiency for specific computational tasks, their integration with conventional processing units can create complex power distribution and thermal management challenges that must be carefully addressed to maintain system reliability and performance consistency in real-time environments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!