RISC vs CISC: Strengths in High-Performance Computing

MAR 26, 20268 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RISC vs CISC Architecture Background and HPC Goals

The fundamental distinction between Reduced Instruction Set Computing (RISC) and Complex Instruction Set Computing (CISC) architectures emerged in the 1970s and 1980s as a response to evolving computational demands and hardware capabilities. RISC philosophy advocates for simplified instruction sets with uniform instruction formats, emphasizing hardware simplicity and compiler optimization. Conversely, CISC architectures feature comprehensive instruction sets capable of executing complex operations in single instructions, prioritizing code density and programmer convenience.

RISC architectures originated from research at IBM, Stanford, and Berkeley, demonstrating that simpler processors could achieve superior performance through higher clock frequencies and efficient pipelining. The design philosophy centers on load-store architecture, fixed-length instructions, and extensive register files. Notable implementations include ARM, MIPS, PowerPC, and RISC-V processors, which have dominated embedded systems and mobile computing markets.

CISC architectures, exemplified by Intel's x86 family, evolved from early microprocessors where memory was expensive and programming complexity needed mitigation. These processors feature variable-length instructions, complex addressing modes, and microcode-based execution units. The architecture's strength lies in backward compatibility and rich instruction semantics that can reduce program size and development complexity.

In high-performance computing contexts, both architectures have undergone significant evolution to address computational intensity, parallel processing requirements, and energy efficiency constraints. Modern HPC workloads demand exceptional floating-point performance, memory bandwidth utilization, and scalability across distributed systems. The architectural choice significantly impacts performance characteristics, power consumption, and software ecosystem compatibility.

The convergence of architectural features has blurred traditional RISC-CISC boundaries, with modern processors incorporating elements from both paradigms. Contemporary HPC processors utilize sophisticated techniques including out-of-order execution, speculative execution, and advanced branch prediction regardless of their foundational architecture. This evolution reflects the industry's pursuit of optimal performance-per-watt ratios and computational throughput.

Current HPC objectives emphasize exascale computing capabilities, requiring processors to deliver unprecedented performance while maintaining energy efficiency. The architectural evaluation must consider factors including instruction-level parallelism, memory hierarchy optimization, interconnect bandwidth, and software stack maturity. These considerations directly influence the suitability of RISC versus CISC approaches for next-generation supercomputing systems.

RISC architectures originated from research at IBM, Stanford, and Berkeley, demonstrating that simpler processors could achieve superior performance through higher clock frequencies and efficient pipelining. The design philosophy centers on load-store architecture, fixed-length instructions, and extensive register files. Notable implementations include ARM, MIPS, PowerPC, and RISC-V processors, which have dominated embedded systems and mobile computing markets.

CISC architectures, exemplified by Intel's x86 family, evolved from early microprocessors where memory was expensive and programming complexity needed mitigation. These processors feature variable-length instructions, complex addressing modes, and microcode-based execution units. The architecture's strength lies in backward compatibility and rich instruction semantics that can reduce program size and development complexity.

In high-performance computing contexts, both architectures have undergone significant evolution to address computational intensity, parallel processing requirements, and energy efficiency constraints. Modern HPC workloads demand exceptional floating-point performance, memory bandwidth utilization, and scalability across distributed systems. The architectural choice significantly impacts performance characteristics, power consumption, and software ecosystem compatibility.

The convergence of architectural features has blurred traditional RISC-CISC boundaries, with modern processors incorporating elements from both paradigms. Contemporary HPC processors utilize sophisticated techniques including out-of-order execution, speculative execution, and advanced branch prediction regardless of their foundational architecture. This evolution reflects the industry's pursuit of optimal performance-per-watt ratios and computational throughput.

Current HPC objectives emphasize exascale computing capabilities, requiring processors to deliver unprecedented performance while maintaining energy efficiency. The architectural evaluation must consider factors including instruction-level parallelism, memory hierarchy optimization, interconnect bandwidth, and software stack maturity. These considerations directly influence the suitability of RISC versus CISC approaches for next-generation supercomputing systems.

HPC Market Demand for Advanced Processor Architectures

The high-performance computing market is experiencing unprecedented growth driven by the exponential increase in computational demands across multiple sectors. Scientific research institutions require massive parallel processing capabilities for climate modeling, genomics analysis, and particle physics simulations. The artificial intelligence revolution has created substantial demand for specialized computing architectures capable of handling deep learning workloads and neural network training at scale.

Enterprise applications are increasingly relying on HPC solutions for real-time analytics, financial modeling, and supply chain optimization. The emergence of edge computing and Internet of Things applications has further expanded the market scope, requiring processors that can deliver high performance while maintaining energy efficiency. Cloud service providers are investing heavily in advanced processor architectures to support their expanding infrastructure and meet growing customer demands for computational resources.

The automotive industry's transition toward autonomous vehicles has created new requirements for processors capable of real-time decision making and sensor data processing. Similarly, the aerospace and defense sectors demand robust computing solutions for radar processing, satellite communications, and mission-critical applications. These applications require processors that can maintain consistent performance under varying operational conditions while meeting strict reliability standards.

Energy efficiency has become a critical factor in processor selection, as data centers seek to reduce operational costs and environmental impact. The market increasingly favors architectures that can deliver superior performance-per-watt ratios, driving innovation in both RISC and CISC processor designs. This trend has intensified competition between different architectural approaches, each offering distinct advantages for specific HPC workloads.

The growing complexity of modern applications has created demand for processors with enhanced parallel processing capabilities, advanced memory hierarchies, and specialized instruction sets. Market participants are seeking architectures that can efficiently handle diverse workloads while providing scalability for future growth. This has led to increased interest in hybrid approaches that combine the strengths of different processor architectures to optimize performance across varied computational tasks.

Enterprise applications are increasingly relying on HPC solutions for real-time analytics, financial modeling, and supply chain optimization. The emergence of edge computing and Internet of Things applications has further expanded the market scope, requiring processors that can deliver high performance while maintaining energy efficiency. Cloud service providers are investing heavily in advanced processor architectures to support their expanding infrastructure and meet growing customer demands for computational resources.

The automotive industry's transition toward autonomous vehicles has created new requirements for processors capable of real-time decision making and sensor data processing. Similarly, the aerospace and defense sectors demand robust computing solutions for radar processing, satellite communications, and mission-critical applications. These applications require processors that can maintain consistent performance under varying operational conditions while meeting strict reliability standards.

Energy efficiency has become a critical factor in processor selection, as data centers seek to reduce operational costs and environmental impact. The market increasingly favors architectures that can deliver superior performance-per-watt ratios, driving innovation in both RISC and CISC processor designs. This trend has intensified competition between different architectural approaches, each offering distinct advantages for specific HPC workloads.

The growing complexity of modern applications has created demand for processors with enhanced parallel processing capabilities, advanced memory hierarchies, and specialized instruction sets. Market participants are seeking architectures that can efficiently handle diverse workloads while providing scalability for future growth. This has led to increased interest in hybrid approaches that combine the strengths of different processor architectures to optimize performance across varied computational tasks.

Current RISC and CISC Performance Status in HPC

RISC architectures currently demonstrate significant advantages in HPC environments through their streamlined instruction sets and optimized execution pipelines. Modern RISC processors like ARM-based systems and RISC-V implementations achieve superior performance-per-watt ratios, making them increasingly attractive for large-scale computing clusters where power efficiency directly impacts operational costs. The simplified instruction decode mechanisms in RISC designs enable higher clock frequencies and more predictable execution patterns, which are crucial for parallel computing workloads.

Contemporary CISC processors, particularly x86-64 architectures from Intel and AMD, maintain dominance in traditional HPC markets through decades of optimization and extensive software ecosystem support. These processors leverage complex instruction sets to reduce code size and improve memory bandwidth utilization, while advanced microarchitectural features like out-of-order execution and sophisticated branch prediction compensate for instruction complexity overhead.

Performance benchmarking reveals distinct strengths across different HPC application domains. RISC architectures excel in highly parallel, compute-intensive tasks such as scientific simulations and machine learning inference, where their regular instruction patterns align well with vectorized operations. CISC processors demonstrate superior performance in legacy HPC applications and workloads requiring complex memory addressing modes or specialized instruction sets like AVX-512 for vector processing.

Power consumption analysis shows RISC architectures achieving 2-3x better performance-per-watt ratios in specific workloads, particularly in sustained throughput scenarios. However, CISC processors often deliver higher absolute performance in single-threaded applications and tasks requiring complex control flow, making them preferred for certain computational fluid dynamics and finite element analysis applications.

The emergence of heterogeneous computing platforms combining both architectures represents a growing trend in HPC system design. Leading supercomputing installations increasingly deploy hybrid configurations, utilizing CISC processors for control plane operations and complex sequential tasks while leveraging RISC-based accelerators for massively parallel computations, optimizing overall system efficiency and performance characteristics.

Contemporary CISC processors, particularly x86-64 architectures from Intel and AMD, maintain dominance in traditional HPC markets through decades of optimization and extensive software ecosystem support. These processors leverage complex instruction sets to reduce code size and improve memory bandwidth utilization, while advanced microarchitectural features like out-of-order execution and sophisticated branch prediction compensate for instruction complexity overhead.

Performance benchmarking reveals distinct strengths across different HPC application domains. RISC architectures excel in highly parallel, compute-intensive tasks such as scientific simulations and machine learning inference, where their regular instruction patterns align well with vectorized operations. CISC processors demonstrate superior performance in legacy HPC applications and workloads requiring complex memory addressing modes or specialized instruction sets like AVX-512 for vector processing.

Power consumption analysis shows RISC architectures achieving 2-3x better performance-per-watt ratios in specific workloads, particularly in sustained throughput scenarios. However, CISC processors often deliver higher absolute performance in single-threaded applications and tasks requiring complex control flow, making them preferred for certain computational fluid dynamics and finite element analysis applications.

The emergence of heterogeneous computing platforms combining both architectures represents a growing trend in HPC system design. Leading supercomputing installations increasingly deploy hybrid configurations, utilizing CISC processors for control plane operations and complex sequential tasks while leveraging RISC-based accelerators for massively parallel computations, optimizing overall system efficiency and performance characteristics.

Current RISC and CISC Solutions for HPC Workloads

01 Hybrid RISC-CISC architecture for enhanced performance

Processor architectures that combine RISC and CISC design principles to leverage the advantages of both approaches. These hybrid architectures utilize RISC-style execution cores with CISC-compatible instruction decoding, allowing for simplified instruction execution while maintaining compatibility with complex instruction sets. The design enables improved performance through reduced instruction decode complexity and enhanced pipeline efficiency.- Hybrid RISC-CISC architecture for enhanced performance: Processor architectures that combine RISC and CISC design principles to leverage the advantages of both approaches. These hybrid architectures utilize RISC-style execution cores with CISC-compatible instruction decoding, allowing for simplified instruction execution while maintaining compatibility with complex instruction sets. The design enables improved performance through reduced instruction decode complexity and enhanced pipeline efficiency.

- Instruction translation and optimization techniques: Methods for converting complex instructions into simpler micro-operations to improve execution efficiency. These techniques involve decoding CISC instructions into RISC-like micro-ops that can be executed more efficiently in pipelined architectures. The translation process enables better utilization of execution resources and reduces instruction execution latency while maintaining instruction set compatibility.

- Pipeline optimization and instruction scheduling: Advanced pipeline designs and instruction scheduling mechanisms that enhance processor throughput and reduce execution stalls. These approaches focus on optimizing instruction flow through multiple pipeline stages, implementing out-of-order execution capabilities, and managing data dependencies efficiently. The techniques enable higher instruction-level parallelism and improved overall processor performance.

- Cache architecture and memory access optimization: Specialized cache designs and memory hierarchy optimizations tailored for different instruction set architectures. These implementations focus on reducing memory access latency and improving data locality through advanced cache management strategies. The designs address the different memory access patterns characteristic of RISC and CISC architectures to maximize performance.

- Performance monitoring and adaptive execution: Systems for monitoring processor performance metrics and dynamically adjusting execution strategies based on workload characteristics. These mechanisms collect runtime performance data and optimize instruction execution paths, resource allocation, and power consumption. The adaptive approaches enable processors to achieve optimal performance across diverse application scenarios and workload types.

02 Instruction translation and optimization techniques

Methods for converting complex instructions into simpler micro-operations to improve execution efficiency. These techniques involve decoding CISC instructions into RISC-like micro-ops that can be executed more efficiently in pipelined architectures. The translation process enables better utilization of execution units and reduces the performance gap between different instruction set architectures.Expand Specific Solutions03 Pipeline optimization and instruction scheduling

Advanced pipeline designs and instruction scheduling mechanisms that enhance throughput and reduce execution latency. These approaches focus on optimizing instruction flow through multiple pipeline stages, minimizing stalls and hazards, and maximizing parallel execution capabilities. The techniques are applicable to both architecture types to improve overall processor performance.Expand Specific Solutions04 Cache and memory hierarchy optimization

Strategies for improving memory access performance through enhanced cache designs and memory management techniques. These optimizations address the memory bottleneck that affects both architecture types by implementing efficient cache hierarchies, prefetching mechanisms, and memory access scheduling. The approaches help reduce memory latency and improve data availability for instruction execution.Expand Specific Solutions05 Performance monitoring and adaptive execution

Systems for monitoring processor performance metrics and dynamically adjusting execution strategies based on workload characteristics. These mechanisms collect runtime performance data and use it to optimize instruction execution, resource allocation, and power consumption. The adaptive approaches enable processors to achieve better performance across diverse application scenarios regardless of the underlying architecture type.Expand Specific Solutions

Major Players in RISC and CISC HPC Processor Market

The RISC vs CISC competition in high-performance computing represents a mature technology landscape experiencing renewed dynamism. The market, valued in hundreds of billions globally, spans data centers, AI acceleration, and edge computing applications. Traditional CISC leaders like Intel and AMD dominate x86 server markets, while RISC architectures gain momentum through ARM's energy-efficient designs adopted by companies like Huawei and Samsung. IBM's POWER architecture maintains presence in enterprise computing, while emerging players like XMOS explore RISC-V adoption. Technology maturity varies significantly: established x86 CISC solutions offer proven performance and software compatibility, while RISC architectures demonstrate superior power efficiency and scalability. The competitive landscape shows increasing convergence, with hybrid approaches and specialized accelerators from companies like Mellanox and Altera complementing traditional CPU architectures, suggesting the future favors heterogeneous computing solutions rather than pure architectural dominance.

International Business Machines Corp.

Technical Solution: IBM has pioneered both RISC and CISC architectures for high-performance computing, notably through their POWER RISC processors and mainframe CISC systems. Their POWER architecture demonstrates pure RISC principles with simplified instruction sets, large register files, and efficient pipeline designs optimized for scientific computing workloads. IBM's approach includes advanced out-of-order execution, sophisticated branch prediction algorithms, and multi-threading capabilities that maximize instruction throughput. The POWER processors feature specialized execution units for floating-point operations and vector processing, making them particularly effective for computational intensive HPC applications requiring sustained performance and reliability.

Strengths: Exceptional reliability and specialized HPC optimization with strong enterprise support. Weaknesses: Higher cost and limited market adoption compared to mainstream x86 solutions.

Intel Corp.

Technical Solution: Intel has developed hybrid architectures combining CISC x86 cores with RISC-like microarchitectures for high-performance computing. Their latest processors feature complex instruction decoding that breaks CISC instructions into RISC-like micro-operations, enabling superscalar execution and out-of-order processing. Intel's approach leverages CISC compatibility for software ecosystem while achieving RISC-like performance through advanced branch prediction, speculative execution, and multi-level cache hierarchies. Their Xeon processors demonstrate sustained performance in HPC workloads through sophisticated instruction scheduling and parallel execution units.

Strengths: Excellent software compatibility and mature ecosystem. Weaknesses: Higher power consumption and complex design overhead compared to pure RISC implementations.

Core Technical Innovations in RISC vs CISC for HPC

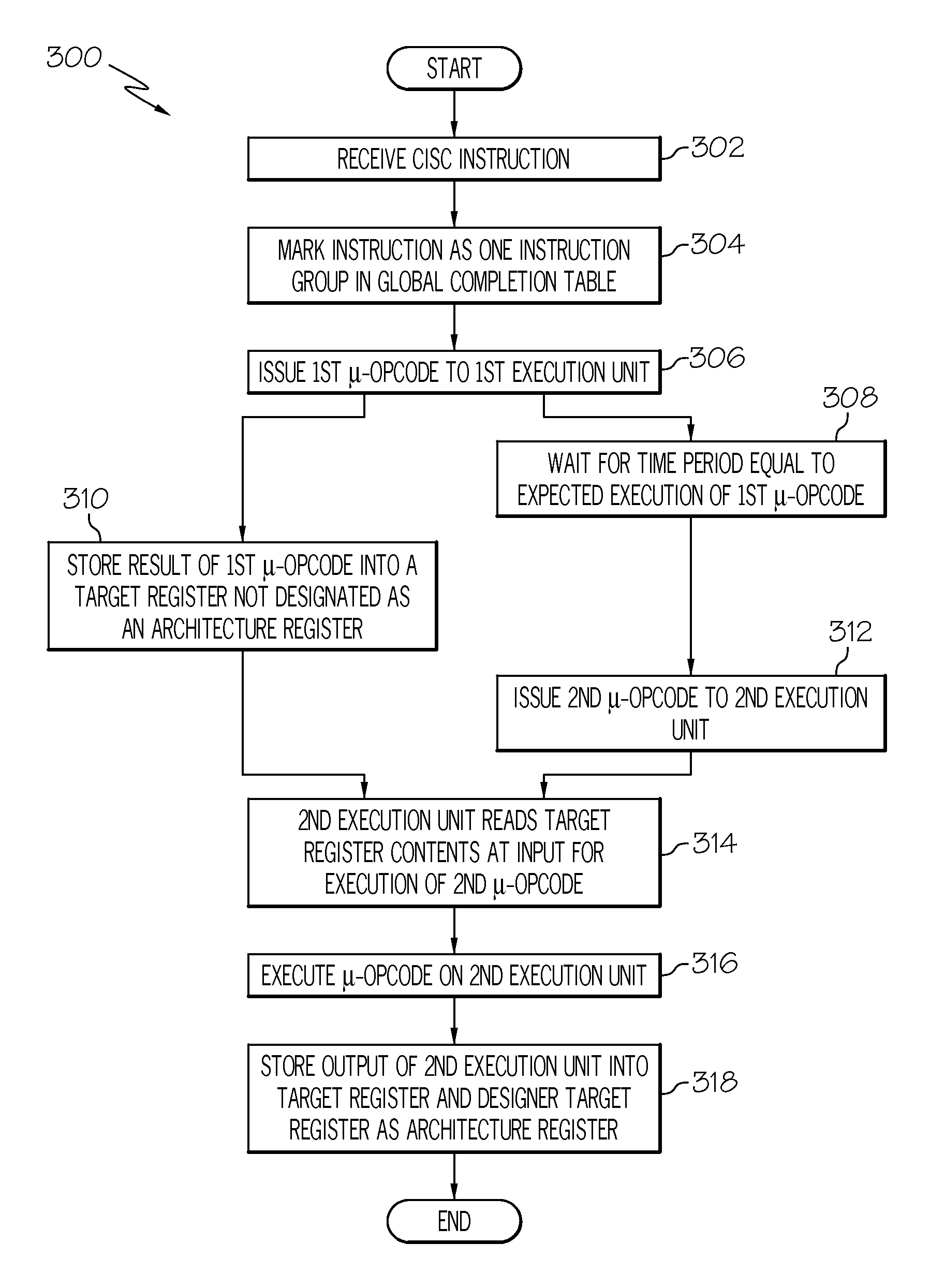

Dual issuing of complex instruction set instructions

PatentInactiveUS20110153991A1

Innovation

- A dual-issue processing method where a CISC instruction is cracked into two micro-ops, with the first micro-op executed by one execution unit to produce intermediate data, which is then used by a second micro-op executed by another unit, with a predetermined delay to align with the execution time of the first micro-op, optimizing the out-of-order processing pipeline architecture.

RISC-v branch prediction method, device, electronic device and storage medium

PatentInactiveUS20220236992A1

Innovation

- An RISC-V branch prediction method that acquires remaining jump times and calculates the single jump step length to determine if a jump is the last one, allowing for proactive execution of either the last or next jump instruction, thereby optimizing resource usage and efficiency.

Energy Efficiency Standards for HPC Processor Design

Energy efficiency has emerged as a critical design criterion for high-performance computing processors, fundamentally reshaping the architectural decisions between RISC and CISC paradigms. The exponential growth in computational demands, coupled with stringent power budgets in data centers and supercomputing facilities, has necessitated the establishment of comprehensive energy efficiency standards that directly influence processor architecture selection.

Modern HPC environments operate under increasingly restrictive power envelopes, with typical data centers allocating 20-30 megawatts for computing infrastructure. This constraint has driven the development of performance-per-watt metrics as primary evaluation criteria, fundamentally altering the traditional focus on raw computational throughput. Energy efficiency standards now mandate specific power consumption thresholds for different performance tiers, creating a framework where architectural simplicity often translates to superior energy characteristics.

RISC architectures demonstrate inherent advantages in meeting these energy efficiency standards through their streamlined instruction sets and simplified decode logic. The reduced complexity of RISC processors typically results in 15-25% lower power consumption per instruction compared to equivalent CISC implementations. This efficiency gain becomes particularly pronounced in parallel computing scenarios where thousands of cores operate simultaneously, amplifying the cumulative energy savings across the entire system.

Contemporary energy efficiency standards emphasize dynamic voltage and frequency scaling capabilities, thermal design power optimization, and idle state management. RISC processors excel in these areas due to their predictable instruction execution patterns and uniform pipeline structures, enabling more effective power management strategies. The simplified control logic allows for finer-grained power gating and more responsive frequency scaling, essential features for meeting modern energy efficiency requirements.

Industry standards such as ENERGY STAR for servers and the Green500 supercomputer rankings have established quantitative benchmarks that favor architectures capable of delivering maximum computational efficiency per watt consumed. These standards typically require processors to achieve specific performance thresholds while maintaining power consumption below defined limits, creating a competitive landscape where RISC architectures' inherent energy efficiency provides significant advantages in HPC deployment scenarios.

Modern HPC environments operate under increasingly restrictive power envelopes, with typical data centers allocating 20-30 megawatts for computing infrastructure. This constraint has driven the development of performance-per-watt metrics as primary evaluation criteria, fundamentally altering the traditional focus on raw computational throughput. Energy efficiency standards now mandate specific power consumption thresholds for different performance tiers, creating a framework where architectural simplicity often translates to superior energy characteristics.

RISC architectures demonstrate inherent advantages in meeting these energy efficiency standards through their streamlined instruction sets and simplified decode logic. The reduced complexity of RISC processors typically results in 15-25% lower power consumption per instruction compared to equivalent CISC implementations. This efficiency gain becomes particularly pronounced in parallel computing scenarios where thousands of cores operate simultaneously, amplifying the cumulative energy savings across the entire system.

Contemporary energy efficiency standards emphasize dynamic voltage and frequency scaling capabilities, thermal design power optimization, and idle state management. RISC processors excel in these areas due to their predictable instruction execution patterns and uniform pipeline structures, enabling more effective power management strategies. The simplified control logic allows for finer-grained power gating and more responsive frequency scaling, essential features for meeting modern energy efficiency requirements.

Industry standards such as ENERGY STAR for servers and the Green500 supercomputer rankings have established quantitative benchmarks that favor architectures capable of delivering maximum computational efficiency per watt consumed. These standards typically require processors to achieve specific performance thresholds while maintaining power consumption below defined limits, creating a competitive landscape where RISC architectures' inherent energy efficiency provides significant advantages in HPC deployment scenarios.

Hybrid Architecture Trends in Next-Gen HPC Systems

The convergence of RISC and CISC architectures represents a fundamental shift in high-performance computing system design, driven by the need to optimize both computational efficiency and energy consumption. Modern HPC systems increasingly adopt hybrid approaches that leverage the strengths of both architectural paradigms rather than adhering to traditional design boundaries.

Contemporary hybrid architectures integrate RISC-based processors with specialized CISC components to create heterogeneous computing environments. These systems typically feature RISC processors as primary compute engines, capitalizing on their superior parallel processing capabilities and energy efficiency, while incorporating CISC-based accelerators for specific workloads requiring complex instruction handling. This architectural fusion enables optimal resource allocation across diverse computational tasks.

The emergence of domain-specific architectures within HPC systems exemplifies this hybrid trend. Graphics processing units originally designed with RISC principles now incorporate CISC-like features for enhanced programmability. Similarly, modern CPUs blend simplified instruction sets with complex microarchitectural optimizations, creating processors that exhibit characteristics of both paradigms while maintaining performance advantages.

Memory hierarchy optimization in hybrid systems leverages architectural diversity to minimize data movement costs. RISC components excel at managing distributed memory systems through their streamlined instruction pipelines, while CISC elements provide sophisticated cache management and memory virtualization capabilities. This complementary approach addresses the memory wall challenge that constrains traditional single-architecture HPC systems.

Software-hardware co-design methodologies are reshaping hybrid architecture development, enabling dynamic reconfiguration based on workload characteristics. Advanced runtime systems can allocate computational tasks to the most suitable architectural components, whether RISC-based cores for parallel algorithms or CISC-enhanced units for sequential processing intensive operations.

Future hybrid architectures will likely incorporate neuromorphic computing elements alongside traditional RISC and CISC components, creating tri-hybrid systems capable of handling artificial intelligence workloads alongside conventional scientific computing applications. This evolution represents the natural progression toward truly adaptive computing platforms that transcend historical architectural limitations.

Contemporary hybrid architectures integrate RISC-based processors with specialized CISC components to create heterogeneous computing environments. These systems typically feature RISC processors as primary compute engines, capitalizing on their superior parallel processing capabilities and energy efficiency, while incorporating CISC-based accelerators for specific workloads requiring complex instruction handling. This architectural fusion enables optimal resource allocation across diverse computational tasks.

The emergence of domain-specific architectures within HPC systems exemplifies this hybrid trend. Graphics processing units originally designed with RISC principles now incorporate CISC-like features for enhanced programmability. Similarly, modern CPUs blend simplified instruction sets with complex microarchitectural optimizations, creating processors that exhibit characteristics of both paradigms while maintaining performance advantages.

Memory hierarchy optimization in hybrid systems leverages architectural diversity to minimize data movement costs. RISC components excel at managing distributed memory systems through their streamlined instruction pipelines, while CISC elements provide sophisticated cache management and memory virtualization capabilities. This complementary approach addresses the memory wall challenge that constrains traditional single-architecture HPC systems.

Software-hardware co-design methodologies are reshaping hybrid architecture development, enabling dynamic reconfiguration based on workload characteristics. Advanced runtime systems can allocate computational tasks to the most suitable architectural components, whether RISC-based cores for parallel algorithms or CISC-enhanced units for sequential processing intensive operations.

Future hybrid architectures will likely incorporate neuromorphic computing elements alongside traditional RISC and CISC components, creating tri-hybrid systems capable of handling artificial intelligence workloads alongside conventional scientific computing applications. This evolution represents the natural progression toward truly adaptive computing platforms that transcend historical architectural limitations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!